来源:本文内容来自公众号【SiP与先进封装技术】,谢谢。

虽然,所有以指数规律增长的曲线在物理意义上均是不可持续的,摩尔定律正是如此。

然而,人们却一直想方设法地去延续摩尔定律,为什么明知不可为而为之?这其实代表了人类的一种理想主义,这种理想或信念往往让人类超越自身,创造出意想不到的科技和文明。

或许正是人们相信了摩尔定律的可持续性,从而带来的信念推动了集成电路五十多年的高速发展。摩尔定律刚提出的时候,我想摩尔本人也不相信在不到芝麻粒大小的一平方毫米,可以集成超过一亿只以上的晶体管。

今天,在指甲盖大小的芯片上,集成的晶体管数量超过了100亿,还可以再多吗?答案依然是肯定的。

然而,随着芯片特征尺寸日益走向极致(3nm~1nm),集成电路中晶体管尺寸的微缩逐渐接近硅原子的物理极限。1nm的宽度中仅能容纳2个硅原子晶格(a=0.5nm),也就是说,在单晶硅中,3个硅原子并排排列的宽度就达到了1nm。

下一步,集成电路技术会走向何方呢?在本文中,您或许能找到自己的答案。

现代科技的发展是以集成电路为基石。集成电路发展的最直接的目标就是在单位面积内或者单位体积内集成更多的晶体管。因此,集成电路的第一个发展方向就是集成更多的晶体管。

在单位面积内集成更多的晶体管就需要将晶体管做的更小,几十年来,在摩尔定律的推动下,晶体管的特征尺寸从毫米级到微米级再到纳米级,尺寸缩小了百万倍。今天,在一平方毫米内可集成超过上亿的晶体管,芯片上的晶体管数量已经达到百亿量级。

那么,晶体管能小到什么程度呢?大致受两个因素的制约,一个是晶体管内最小的结构宽度,另一个是晶体管自身所占的面积。

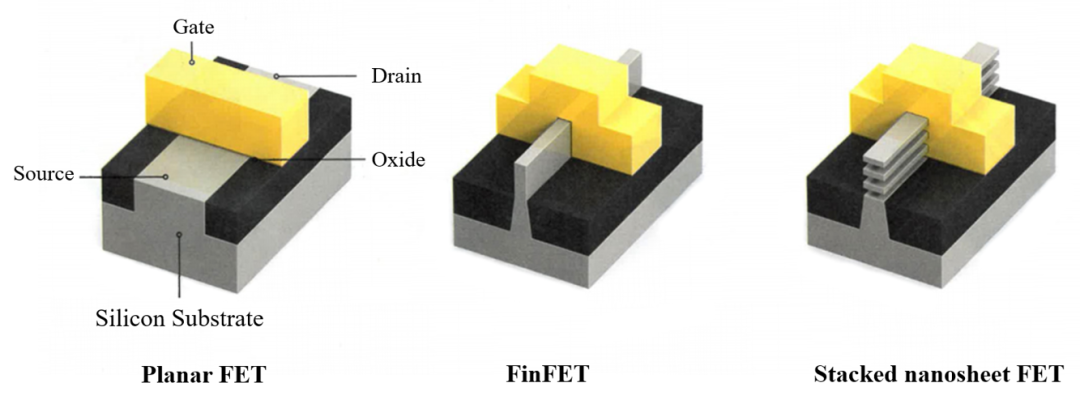

晶体管的最小的结构宽度在22nm之前,通常是栅极宽度,被称为特征尺寸。随着晶体管面积的日益缩小,特征尺寸和厂家的命名逐渐脱节,而栅极宽度也不再是晶体管的最小结构宽度,例如在FinFET中,Fin的宽度通常是小于栅极宽度的,在GAA堆叠纳米片晶体管中,纳米片的厚度也是要小于栅极宽度的。

因此,各大Foundry不再以栅极宽度作为晶体管的特征尺寸,其工艺节点成为一个代名词,并不和某个特定的宽度相对应,但依然是有其物理意义的。主要体现在晶体管面积的缩小,在同样的面积内可集成更多的晶体管。

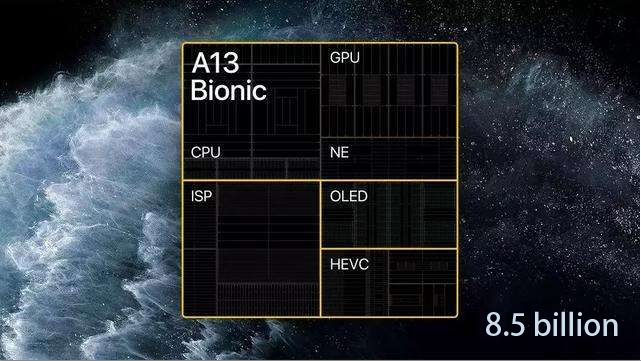

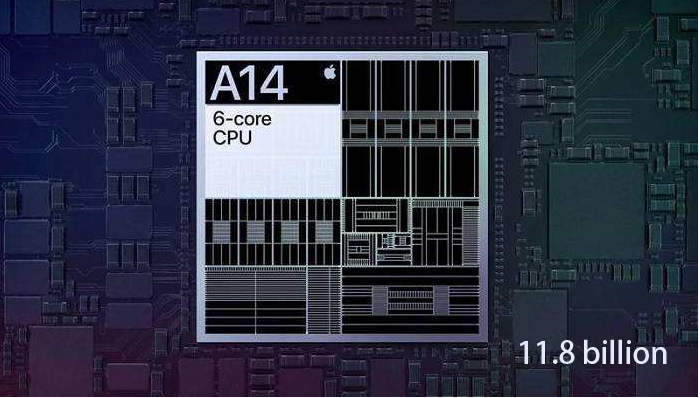

例如,苹果A13芯片采用7nm工艺制程,内有85亿个晶体管,其面积为94.48平方毫米,在1平方毫米可集成8997万个晶体管:0.8997亿/mm^2。苹果A14芯片采用5nm工艺制程,内有118亿个晶体管,其面积为88平方毫米,在1平方毫米可集成1.34亿个晶体管:1.34亿/mm^2

两者的晶体管平均面积之比为1.49,如果严格按照7:5的比值为1.4,其平方为1.96,可以看出,相对于7纳米芯片,5纳米芯片做到了理论值的76%。这也是intel一直认为别的Foundry厂家的命名有水分的原因。

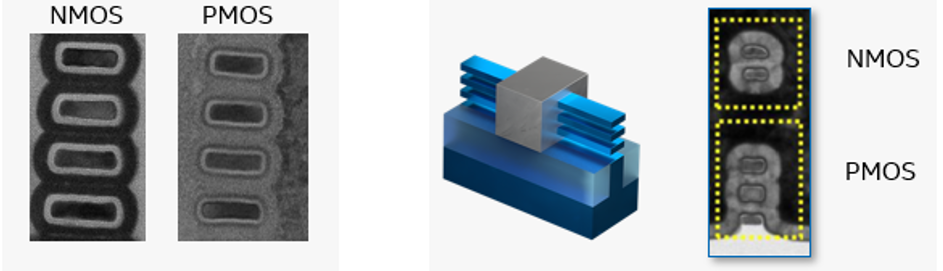

从平面晶体管到FinFET到GAA,晶体管的尺寸不断缩小,结构不断优化,就是为了在单位面积内集成更多的晶体管。

而在单位体积内集成更多的晶体管,除了可以将晶体管做的更小之外,还因为多了一个空间维度,因此可以将晶体管堆叠起来。

大致两种方法,第一种就是在晶圆上通过特殊工艺将晶体管直接做成多层的;另外一种就是和传统工艺相同的方法在晶圆上制作一层晶体管,然后将多个晶圆堆叠起来,晶圆之间通过TSV连接。

关于第一种方法,目前有很多研究,例如将NMOS堆叠在PMOS上,从而节省一半的面积,使晶体管密度提升一倍。其难点在于上层的晶体管没有致密的硅基底作为支撑,很难制作出高质量的晶体管,另外,目前的技术也只能支持两层堆叠。

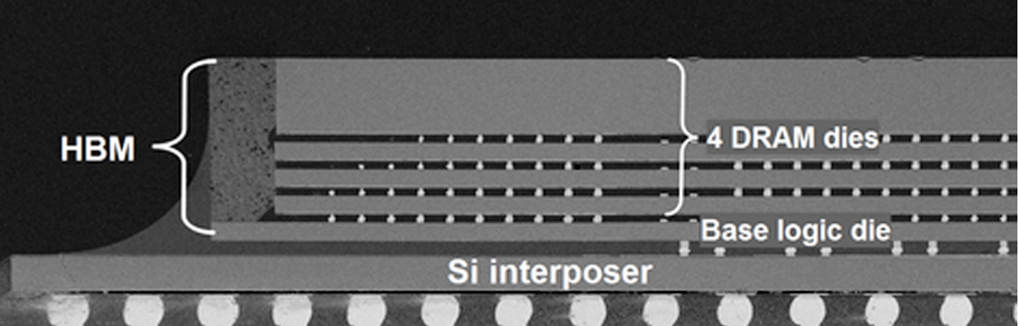

第二种方法目前应用如火如荼,通常被称之为先进封装技术(Advanced Packaging)。

先进封装也称为HDAP高密度先进封装,目前受关注度很高,技术发展迅速,晶圆间互连的TSV密度越来越高,并且理论上不受堆叠层数的限制,最先进的技术目前掌握在Foundry手中。

不过,现在Foundry厂逐渐不把其作为封装技术来看待,而将其视为晶圆制造的一个重要环节,例如TSMC,在其产品线种将其定义为3D Fabric。

理论上讲,XYZ三个维度并没有本质不同,因此,增加一个维度,其集成的晶体管数量可能会成千上万倍地增加,这也被很多人认为摩尔定律可持续的重要原因。

在集成电路中,晶体管作为最小的功能单位,我们可以称之为功能细胞。在单位体积内集成更多的功能细胞,即提升系统的功能密度。

从历史来看,在所有的人造系统中,功能密度都在不断地提升,虽然不同的历史阶段提升的有快有慢,但在人类文明发展的进程中不会停滞。

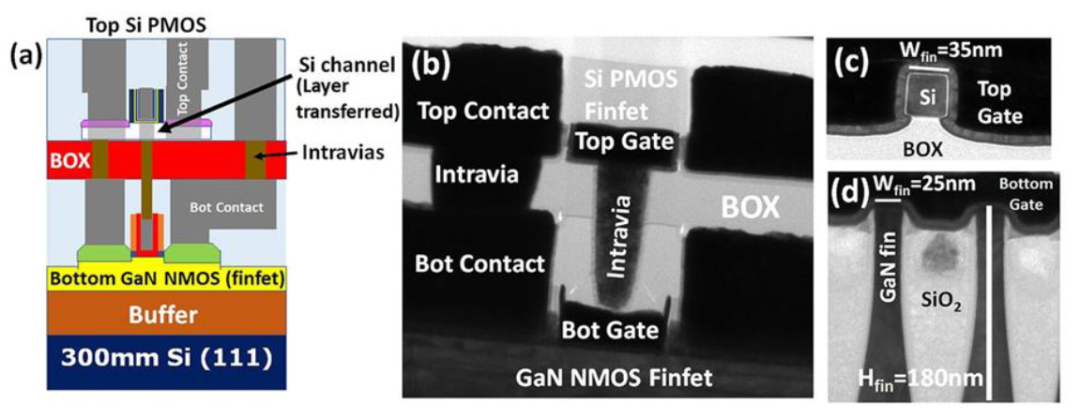

虽然化合物半导体近来比较热门,但集成电路中,硅目前还是占据着绝对的主流位置。因此,芯片制造商一直试图将化合物半导体应用在传统的硅晶圆上,从而有效利用现有资源并创造出更大的经济效益。

通过在300毫米的硅晶圆上集成氮化镓基(GaN-based)功率器件与硅基CMOS,实现了更高效的电源技术。这为CPU提供低损耗、高速电能传输创造了条件,同时也减少了主板组件和空间。

氮化镓半导体器件主要可分为GaN-on-Si(硅基氮化镓)、GaN-on-SiC(碳化硅基氮化镓),GaN-on-sapphire(蓝宝石基氮化镓)等几种晶圆。

由于成本和技术等因素,硅基氮化镓成为了目前半导体市场主流。

英特尔在300毫米的硅晶圆上首次集成氮化镓基(GaN-based)功率器件,此研究验证了300毫米工艺兼容可行性,更适配高电压应用,增加了功能,提升了大规模制造可能性。

全世界现在大概有上万亿美元的投资都是在300毫米硅晶圆设备、生态系统上,需要把这些充分利用起来,这样制造成本才能下降。

此外,台积电目前采用的也是GaN-on-Si(硅基氮化镓)技术。

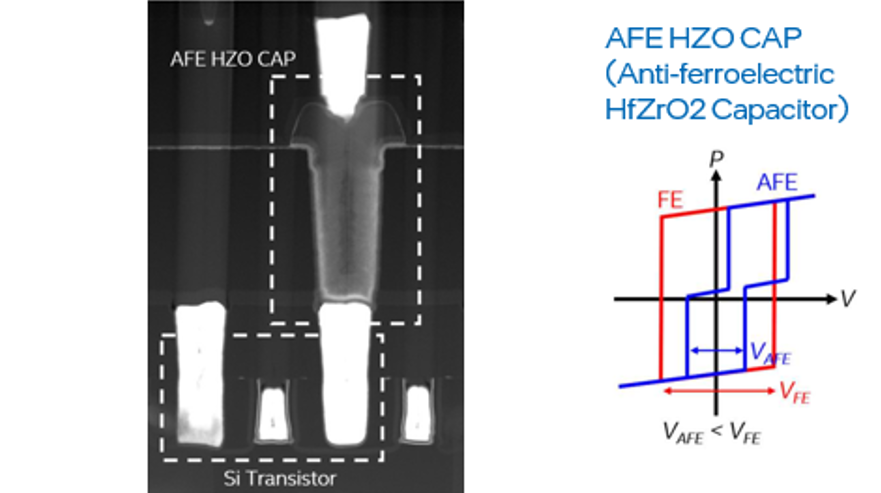

另一项技术是利用新型铁电体材料作为下一代嵌入式DRAM技术的可行方案。该项技术可提供更大内存资源和低时延读写能力,用于解决从人工智能到高性能计算等应用所面临的日益复杂的问题。

新型铁电存储器,采用新的技术实现了2纳秒的读写速度和超过10的12次方的读写周期,其性能和寿命都远超现有的存储器。

铁电存储器可以和传统的CMOS工艺结合,用来作为从L1 Cache到DRMA之间的中间层。

扩展硅元素,在功率器件和内存增益领域提升硅基半导体的性能,目前已经取得了不错的进展。人们还在不断地努力探寻其它的方法来扩展硅元素。

由于量子力学隧道效应,电子可以穿越绝缘体,这将使元件功能失效。人们开始寻找一种新型晶体管,可以进一步提高未来集成电路的性能,作为传统晶体管的替代品。目前有很多研究,但还没有领先者可以取代硅MOSFET。

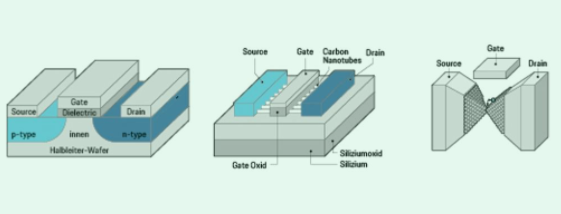

研究人员列出了一系列MOSFET替代品,包括隧道场效应晶体管TFET,碳纳米管场效应晶体管,单原子晶体管。

隧道场效应晶体管(TFET-Tunnel Field Effect Transistor),和传统MOSFET晶体管原理不同,在TFET中源极和漏极掺杂不同。

它使用量子力学隧道效应,栅极和源极之间的电压决定了电荷载流子是否可以“隧穿”通过源极和漏极之

间的能量势垒,以及电流是否可能流动。

根据量子理论,有些电子纵使明显缺乏足够的能量来穿过能量势垒,它们也能做到这一点,这就是量子隧道效应。

在隧道场效应晶体管中,两个小槽被一个能量势垒分开。在第一个小槽中,一大群电子在静静等待着,晶体管没有被激活,当施加电压时,电子就会通过能量势垒并且移入第二个小槽内,同时激活晶体管。TFET在结构上类似于传统晶体管,但在开关方面利用了量子力学隧道效应,既节能又快捷。

通过减少能量势垒的幅度,增强并利用量子效应将成为可能,因此,电子穿过势垒所需要的能量会大大减少,晶体管的能耗也会因此而显著下降。利用量子隧道效应研制出的隧道场效应晶体管有望将芯片的能耗减少到百分之一(1/100)。

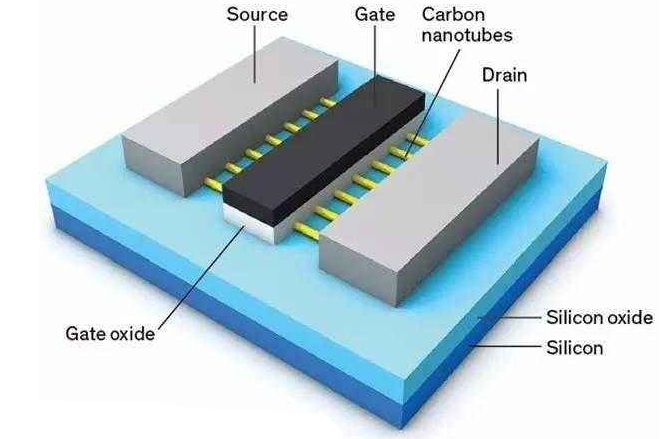

碳纳米管场效应晶体管(CNFET-Carbon Nanotube Field Effect Transistor)

在CNFET中,源极和漏极之间的沟道由碳纳米管组成,其直径仅有1–3 nm, 意味着其作为晶体管的沟道更容易被栅控制。因此, 碳纳米管晶体管比传统硅基晶体管在比例缩减上的潜力会更大。

碳纳米管具有超高的室温载流子迁移率和饱和速度,室温下,碳纳米管中载流子迁移率大约为硅的100倍, 饱和速度大约是硅的4倍。在相同沟道长度下, 载流子迁移率越高,饱和速度越高,速度越快,并能增加能量的利用效率。

碳纳米管晶体管具备超低电压驱动的潜力,从而在低功耗方面具有巨大优势,在沟道材料的选择中, 碳纳米管沟道同时具备了天然小尺寸、更好的尺寸缩减潜力和低功耗等关键因素。

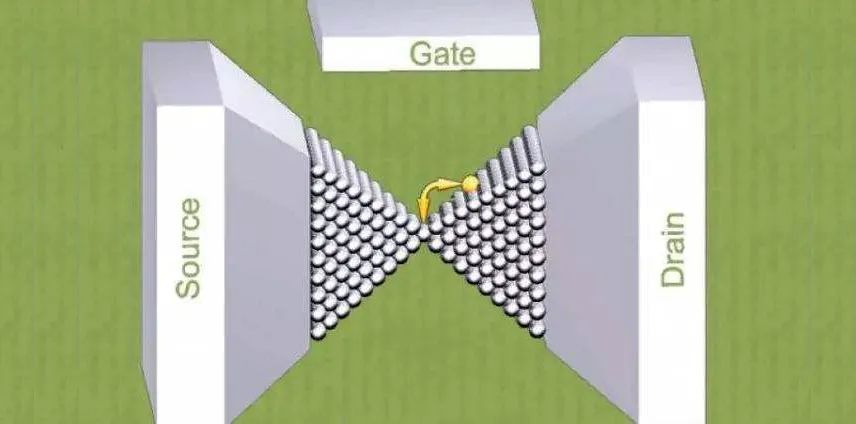

单原子晶体管(Single-Atom Transistor),在这种晶体管中,控制电极移动一个原子,该原子可以连接两端之间的微小间隙,从而使电流能够流动。原则上,它的工作原理就像一个有两个稳定状态的继电器。

在单原子晶体管中,通过源极和栅极之间的电压移动单个原子,从而关闭或打开源极和漏极之间的电路。

在只有单一金属原子宽度的缝隙间建立微小的金属触点,实现目前晶体管所能达到的最小极限。在此缝隙通过电控脉冲移动单个原子,完成电路闭合,将该原子移出缝隙,电路被切断。

由此实现世界上最小晶体管在接通电源情况下单个原子的受控可逆运动。

单原子晶体管由金属构成,不含半导体材料,所需电压极低,能耗也极低。据称,单原子晶体管的能耗将只有传统硅基晶体管的万分之一(1/10000)。

与传统量子电子元件不同,单原子晶体管不需要在接近绝对零度的低温条件工作,它可以在室温下工作,这对未来应用是一个决定性的优势。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2941内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!