来源:内容由半导体行业观察(ID:icbank)

编译自tomshardware

,谢谢。

英特尔可能会将目光投向新的晶体管设计,作为马其顿骑兵实现其 2 纳米以下制造的愿望。最近公布的一项在线专利似乎为英特尔指明了前进的方向,即通过所谓的“堆叠叉板晶体管”来保持摩尔定律的活力。然而,该专利往往是模糊的,而且英特尔没有声称 PPA(功率性能面积)的改进。

英特尔 Forksheet 晶体管 (图片来源:英特尔)

据这家蓝色巨人称,新的晶体管设计最终可以实现 3D、垂直堆叠的 CMOS 架构,与当今最先进的三栅极设计相比,该架构允许增加晶体管数量。然而,进一步缩小晶体管的难度已经变得如此之大,甚至英特尔的专利也将这些限制描述为“压倒性的”——成本、风险和复杂性现在似乎都超过了潜在的好处。

英特尔的专利描述了纳米带晶体管与新的原子薄锗薄膜配对的使用,该薄膜充当介电壁(dielectric wall)。该壁(WALL)用作层之间的物理分隔,用作p-栅极沟槽和n-栅极沟槽之间的绝缘体。它在每个垂直堆叠的晶体管层中重复,这取决于有多少晶体管彼此堆叠。实际上,这允许 PMOS和 NMOS 器件之间的空间在其功能受到影响之前更加紧密(与没有wall的情况下它们必须保持相同的效果相比),这意味着英特尔可以将更多的器件放入一个较小的区域。结果,摩尔定律又喘了一口气。

英特尔旱在 2019 年就已经开始探索该技术一一该公司在其电子设备会议 (EDM)活动中展示了该技术。然而,无论是在这项专利中,我们都找不到关于 forksheet 技术如何提高晶体管密度、性能和功率效率的一些"硬估计”的具体数据。

幸运的是,英特尔并不是第一家引用这种制造方法的公司。总部位于比利时的研究小组Imec 在2019 年也宣布开发出第一个用于"forksheet设备"的标准单元模拟结果。是的,这些

forksheet 设备是英特尔专利的基础。

因此,两家机构在纳米电子学领域有着密切而长久的联系也就不足为奇了。

堆叠叉板晶体管的平面图和横截面图。 (图片来源:英特尔)

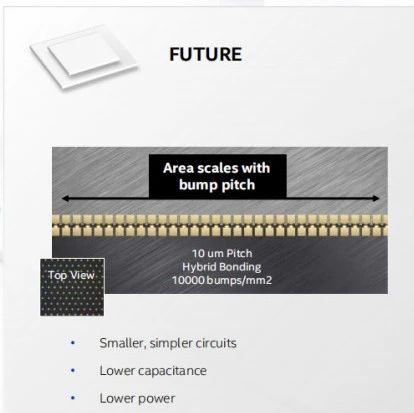

根据 Imec 的第一个标准单元模拟结果,当应用于 2nm 技术节点时,与传统的纳米片方法相比,该技术可以显着提高晶体管密度。我们希望在恒定速度下提高 10% 的速度或提高 24% 的能效,同时“减少 20% 以上的电池面积”。此外,静态随机存取存储器 (SRAM) 占用空间(通常构成 CPU 的高速缓存并且是芯片面积的最重要贡献者之一)显着减少了 30%。

与台积电宣布的 3nm 节点相比 5nm 的改进:其b性能提升 10% 到 15%(在相同的功率和晶体管数量下),最多降低 30% 的功率(在相同的时钟和复杂性下),最多 70%逻辑密度增益(适用于内核)和高达 20% 的 SRAM 密度增益。

我们必须记住,并不是所有的专利都能够成为实际的产品或制造技术——它们有时是保护潜在或试探性投资或研究场所的方法,甚至可以隐喻地烧毁竞争对手在该领域的进步。然而,Imec 从 2019 年开始的研究已经为 2 纳米以下节点提出了令人印象深刻的可能改进,特别是考虑到它在精确的蚀刻分辨率范围内但具有不同的晶体管架构时。所以它是跳转——没有节点跳转。

英特尔现在有时间进行更多的研究,而且我们现在知道对堆叠叉板晶体管的研究至少持续到 2020 年 6 月。而且我们还知道,半导体制造规划和研究是令人难以置信的长尾。英特尔首席执行官 Pat Gelsinger在 2008 年首次提到10 纳米技术——现在是Intel 7——当时他仍担任首席技术官,理由是他看到了“一条清晰的道路”。这种清晰的方式只有在今年的 Alder Lake 中才真正体现出来,这表明了前沿半导体制造的资本需求。Intel 7 可能来晚了,但 Alder Lake 打破超频的世界纪录。

目前尚不清楚英特尔是否会在 2nm 工艺中选择堆叠叉板架构,或者是否希望更早地获得其设计优势。但英特尔提交了专利申请,这最终意味着该设计具有一定的价值。该公司似乎比我们更了解这项技术的可行性。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2930内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!