来源:内容由半导体行业观察(ID:icbank)

编译自semiconductor-digest

,谢谢。

去年11月,AMD 举行了AMD 加速数据中心首映式,英特尔也举办了他们的创新日,CNET 的 Stephen Shankland参观了英特尔在钱德勒的 42 号和 CH-4 晶圆厂。

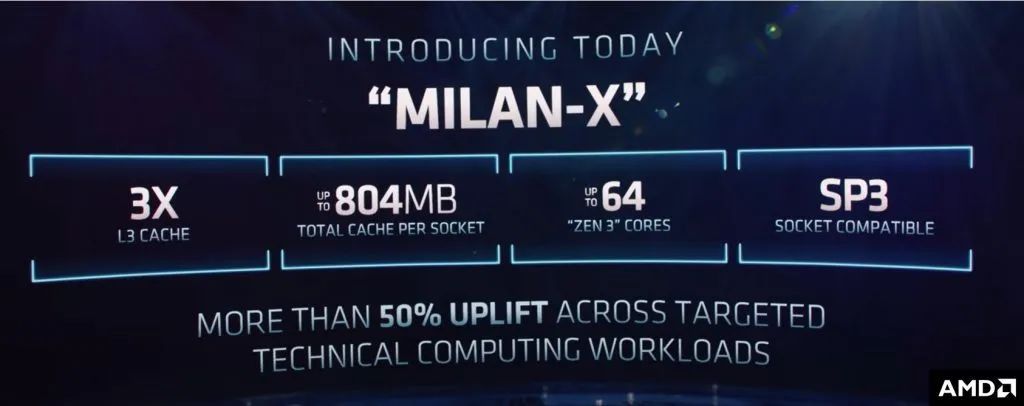

在首映式上,AMD 首席执行官 Lisa Su 介绍了新的 Milan-X,这是第三代 AMD EPYC (霄龙)处理器,带有 3D V-cache。

它有八个 Zen 3 CCD,每个 CCD 上混合粘合了 6 x 6 mm 64 MB SRAM,因此与我们今年早些时候在 Computex 之后报道的 SRAM 芯片基本相同。

这为部件增加了 512 MB L3 缓存,总共 768 MB,加上 L2 缓存,总共就获得了 804 MB。

AMD 显然对台积电的 SOIC 混合键合技术感到满意,因为他们正在推出这款备受瞩目的新产品,每台设备有 8 个这样的芯片。

在随后的主题演讲中,AMD 数据中心和嵌入式解决方案事业部高级副总裁/总经理 Forrest Norrod 讨论了新的 AMD Instinct MI200 系列加速器。它们包含两个 CDNA2 GPU 芯片,总共 580 亿个晶体管,采用 6 纳米技术,具有多达 8 个 HBM2E 内存堆栈,使其成为世界上第一款配备 128 GB HBM2E 的 GPU。这引起了我们 3D 封装的注意,因为他们使用了““Elevated Fanout Bridge”。

这本质上是一个连接器die,如英特尔的 EMIB 和台积电的 InFO-LSI,但位于基板 PCB 的顶部,而不是嵌入其中。

AMD 拥有此类结构的专利(US 10,867,978)。

这让我倾向于认为 AMD 将使用 OSAT 而不是 TSMC 来实现这项技术。碰巧的是,SPIL(Siliconware Precision Industries Co., Ltd)在 ECTC 2020 上宣布,他们拥有类似的技术,标记为“Fan-Out Embedded Bridge”。

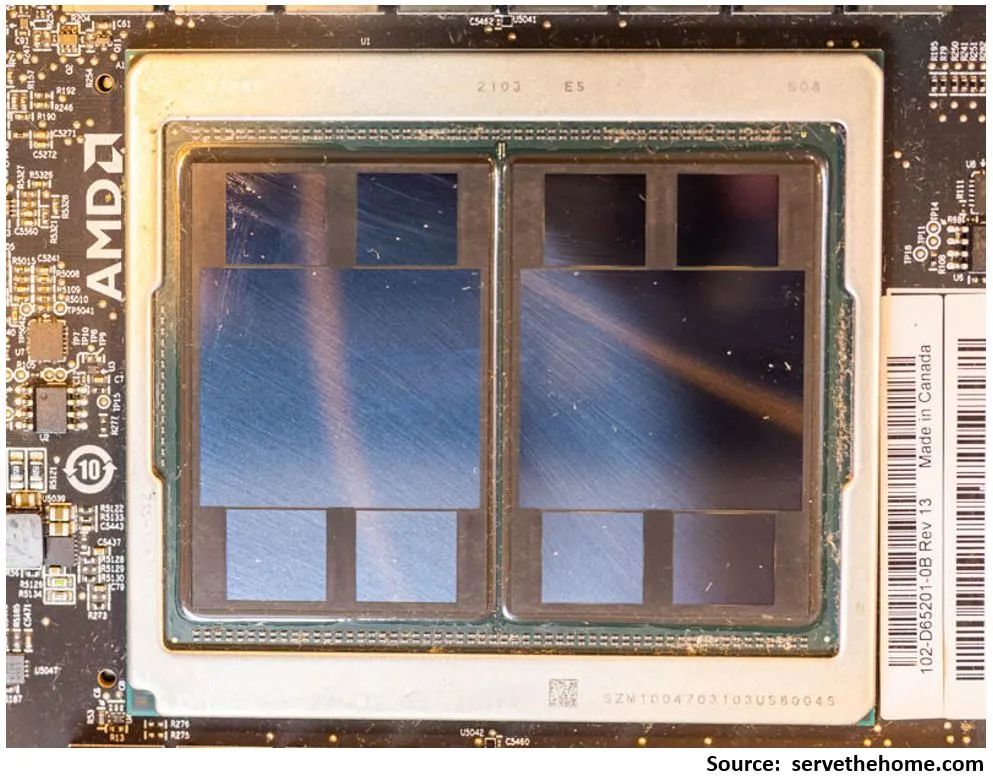

在几周前的 SC21 大会上,AMD 展示了一个 HPE Cray EX235a 节点,它使用了 AMD Instinct MI250X,Serve The Home的 Patrick Kennedy眼尖地发现了它,并发布了详细信息,所以我们知道 Instincts 是至少已经送样被OEM 了。

没有 EFB 的迹象,但大概我们的视线被底部填充物遮住了。

在英特尔活动中实际上并没有太多提及封装,尽管他们确实讨论过“Sapphire Rapids”(SPR)下一代至强处理器,由四个与 EMIB 裸片相连的“tiles” 组成,并可选择添加 HBM。

正如我们所见,SPR 裸片约为 400mm

2

,有 10 个 EMIB die连接它们,另外四个用于四个 HBM 堆栈时使用。

当 Stephen Shankland 参观英特尔的 CH4 封装工厂时,他拍下了一张 SPR 基板的照片,显示了 EMIB 芯片所在的位置。

我们可以看到,每个裸片有 5 个用于计算 tile 互连的 EMIB 点,另外还有 1 个用于 HBM 堆栈。他还向我们展示了填充基板的样子:

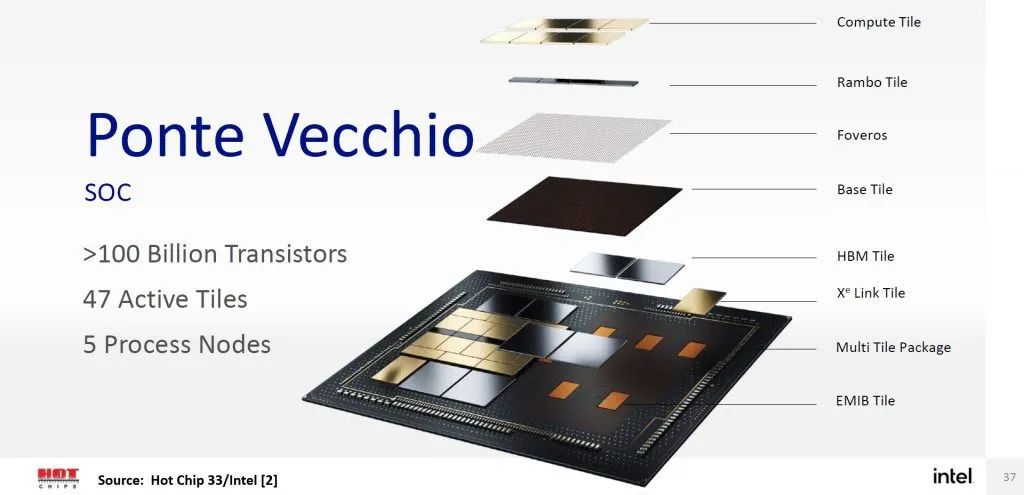

一段时间以来,英特尔一直在推广他们的 Ponte Vecchio (PVC) 高端 GPU,它大量使用了 Foveros 芯片堆叠和 EMIB 互连。

计算 tile 是使用 TSMC N5,Xe Link tile 是使用 TSMC N7,base tile 则是 使用Intel 7 制造的。Ravi Mahajan 在 Hot Chips 33 大会上给出了一些封装细节,包括 base tile 的 die 尺寸和第一个交叉-我见过的部分。

CNET 还看到了一块由四个组装好的 PVC 部件组成的板:

AMD Instinct 和 Ponte Vecchio 都是耗电的野兽,并使用开放计算项目的 OCP 加速器模块 (OAM),旨在处理高达 700W 的功率。

感谢 Stephen Shankland,我们现在对即将推出的 Meteor Lake CPU 的外观有所了解;他看到了组装测试部件,以评估使用减小的 36 微米凸块间距的 Foveros 堆叠。

我们在那里看到了四个芯片,所以大概一个是填filter,因为 Meteor Lake 由离散计算、GPU 和低功耗 SoC 块组成。Pat Gelsinger 在第三季度电话会议上表示,虽然一个或多个tile来自代工厂,但计算tile是在intel 4 工艺(以前的 7 纳米)中制造的,并且正在运行:

“在英intel 4 上,我们已经流片了Meteor Lake 的计算块,本季度它将从晶圆厂出来,并在 30 分钟内以出色的性能启动,这正是我们预期的。总而言之,这是我们在最近的记忆中看到的最好的领先产品初创企业之一,这说明了这个过程的健康状况。”

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2928内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!