来源:内容由半导体行业观察(ID:icbank)

编译自anandtech

,谢谢。

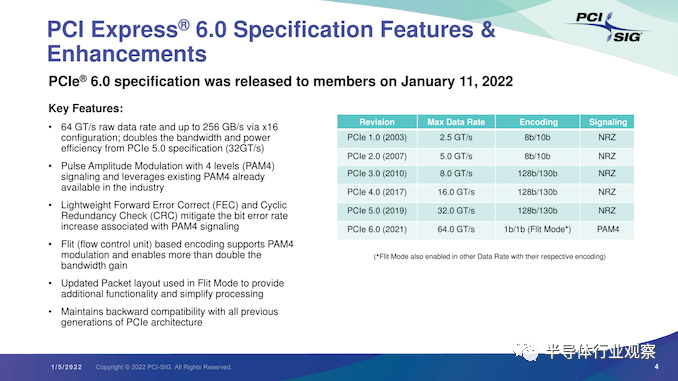

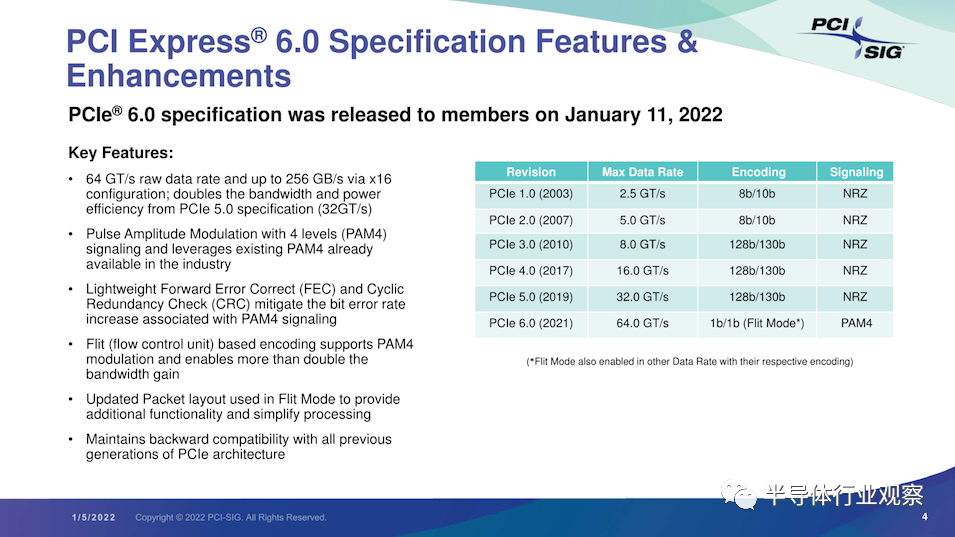

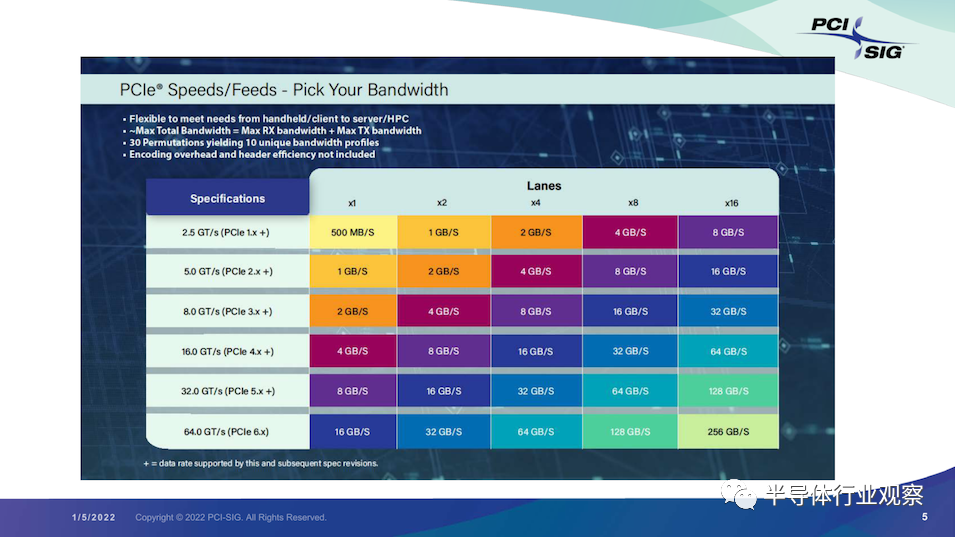

今天早上,PCI 特别兴趣小组 (PCI-SIG) 发布了期待已久的 PCI Express 6.0 最终 (1.0) 规范。下一代无处不在的总线再次将 PCIe 通道的数据速率提高一倍,使其在每个方向上达到 8GB/秒,并且对于多通道配置来说要高得多。随着规范的最终版本现已整理和批准,该组织预计第一批商业硬件将在 12 到 18 个月内投放市场,这实际上意味着它应该在 2023 年开始出现在服务器中。

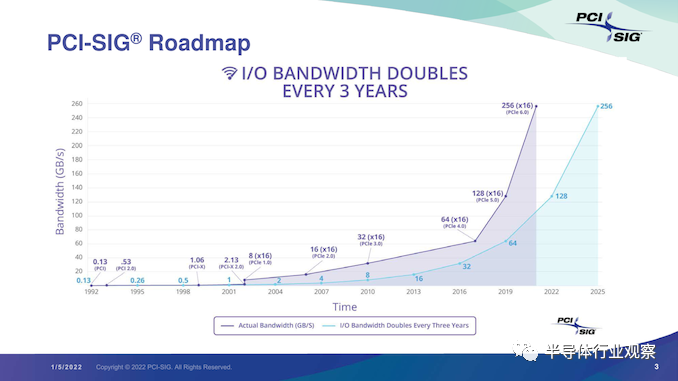

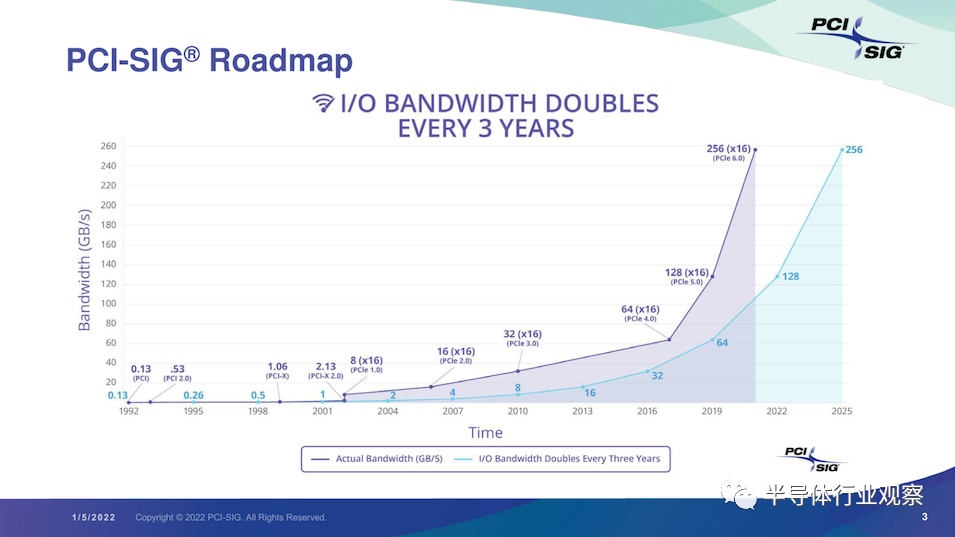

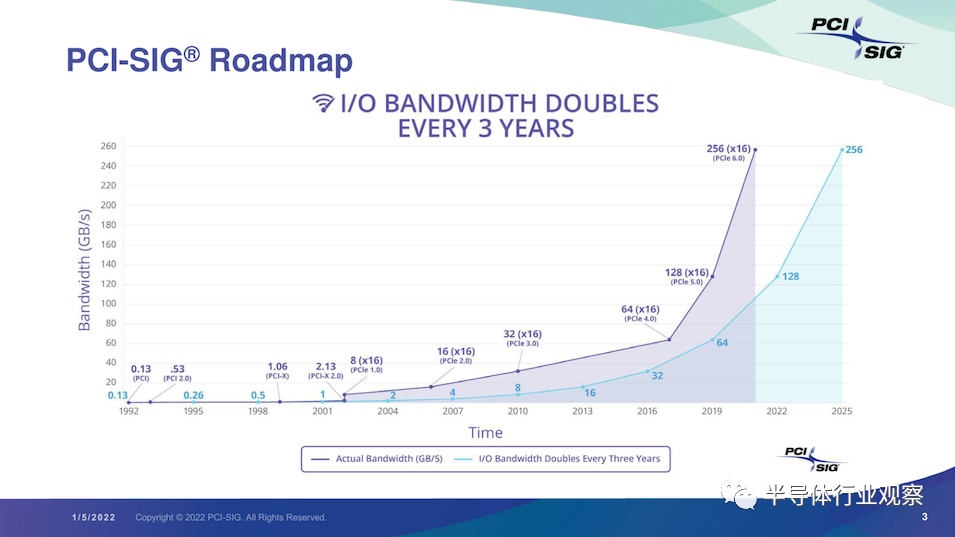

PCI Express 6.0 于 2019 年夏天首次发布,顾名思义,是当前一代 PCIe 5.0 规范的直接后续产品。PCI-SIG 的目标是大约每 3 年将 PCIe 带宽翻一番,一旦 5.0 规范完成,PCI-SIG 几乎立即着手开发 PCIe 6.0,寻找再次将 PCIe 带宽翻倍的方法。这些开发工作的产物是新的 PCIe 6.0 规范,尽管该组织仅在几周前就错过了 2021 年末发布的最初目标,但今天他们宣布该规范已最终确定并将发布给该组织的成员。

与往常一样,更快版本的 PCIe 技术的创建是由行业永不满足的带宽需求推动的。由显卡、加速器、网卡、SSD 和其他 PCIe 设备移动的数据量只会继续增加,因此总线速度也必须如此发展才能保持这些设备的性能。与该标准的过去版本一样,对更快规范的直接需求来自服务器运营商,他们已经定期使用大量高速硬件。但在适当的时候,该技术也应该过滤到消费设备(即个人电脑)。

通过将 PCIe 链路的速度提高一倍,PCIe 6.0 实现了带宽速率的全面加倍。X1 链接从 4GB/秒/方向移动到 8GB/秒/方向,并且对于完整的 x16 链接一直扩展到 128GB/秒/方向。对于已经缝合给定宽度的链路的设备,额外的带宽意味着总线限制的显着增加;同时,对于尚未使链路饱和的设备,PCIe 6.0 提供了减少链路宽度、保持相同带宽同时降低硬件成本的机会。

PCI Express 于 2003 年首次推出,今天的 6.0 版本基本上标志着该技术的第三次重大修订。虽然 PCIe 4.0 和 5.0 只是对早期信号方法的“扩展”——特别是继续使用 PCIe 3.0 的 128b/130b 信号和 NRZ——但 PCIe 6.0 进行了更重大的改革,可以说是该标准历史上最大的一次。

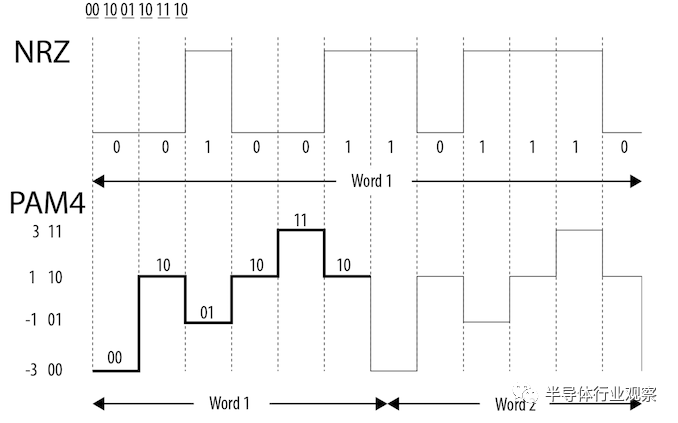

为了使带宽再次翻倍,PCI-SIG 彻底颠覆了信号技术,从一开始就使用的不归零 (NRZ) 技术转向脉冲幅度调制 4 (PAM4)。

正如我们在首次宣布 PCIe 6.0 开发时所写的那样:

在非常高的水平上,PAM4 与 NRZ 相比,是从MLC NAND 手册中获取一页,并将单个单元(或在本例中为传输)将保持的电气状态数量增加一倍。与传统的 0/1 高/低信号不同,PAM4 使用 4 个信号电平,因此信号可以编码为四种可能的两位模式:00/01/10/11。这使得 PAM4 可以承载两倍于 NRZ 的数据,而不必将传输带宽加倍,对于 PCIe 6.0 来说,这将带来大约 30GHz 的频率。

PAM4 本身并不是一项新技术,但到目前为止,它一直是 200G 以太网等超高端网络标准的领域,其中可用于更多物理通道的空间量更加有限。因此,业界在使用信号标准方面已经有几年的经验,并且随着自身带宽需求的不断增长,PCI-SIG 决定将其带入机箱中,以下一代 PCIe 为基础.

使用 PAM4 的代价当然是成本。即使每赫兹带宽更大,PAM4 目前在几乎每个级别上的实施成本都更高,从PHY到物理层。这就是为什么它没有风靡全球,以及为什么 NRZ 继续在其他地方使用的原因。PCIe 的大规模部署规模当然会在这里大有帮助——规模经济仍然很重要——但是一旦 PCIe 6.0 处于上升阶段,看看几年后的情况将会很有趣。

同时,与我之前的类比中的 MLC NAND 不同,由于附加的信号状态,PAM4 信号本身比 NRZ 信号更脆弱。这意味着与 PAM4 一起,PCIe 历史上第一次该标准还获得了前向纠错 (FEC)。名副其实,前向纠错是一种通过提供恒定的纠错数据流来纠正链路中的信号错误的方法,它已经普遍用于数据完整性至关重要且没有时间重新传输的情况下(例如作为带 DSC 的 DisplayPort 1.4)。虽然到目前为止 PCIe 还不需要 FEC,但 PAM4 的脆弱性将改变这一点。包含 FEC 不应该对最终用户产生明显的影响,但对于 PCI-SIG,这是另一个需要应对的设计要求。

值得注意的是,FEC 还与循环冗余校验 (CRC) 配对,作为防止误码的最后一层。即使在 FEC 仍然未能通过 CRC(因此仍然是损坏的)的数据包将触发数据包的完全重传。

切换到 PAM4 的结果是,通过在不增加频率的情况下增加传输的数据量,信号损失要求不会上升。PCIe 6.0 将具有与 PCIe 5.0 相同的 36dB 损耗,这意味着虽然标准并未正式定义走线长度,但 PCIe 6.0 链路应该能够达到与 PCIe 5.0 链路一样远的距离。这无疑让供应商和工程师都松了一口气。

除了 PAM4 和 FEC,PCIe 6.0 的最后一项主要技术补充是它的流量控制单元(FLow control unIT:FLIT) 编码方式。不要与物理层的 PAM4 混淆,FLIT 编码用于逻辑层,将数据分解为固定大小的数据包。通过将逻辑层移动到固定大小的数据包,PCIe 6.0 能够实现 FEC 和其他纠错方法,因为这些方法需要所述固定大小的数据包。FLIT 编码本身并不是一项新技术,但与 PAM4 一样,本质上是从已经使用的高速网络领域借来的。而且,根据 PCI-SIG,它是规范中最重要的部分之一,因为它是启用(持续)具有 FEC 的 PCIe 低延迟操作的关键部分,并且允许非常小的开销。总而言之,PCI-SIG 认为 PCIe 6.0 编码是一种 1b/1b 编码方法,

由于它更像是一个启用部分而不是规范的一个特性,因此 FLIT 编码对用户来说应该是相当不可见的。然而,需要注意的是,PCI-SIG 认为 FLIT 编码在某种意义上也被向后移植以降低链路速率非常重要/有用。一旦在链路上启用 FLIT,链路将始终保持 FLIT 模式,即使链路速率协商下降。因此,例如,如果 PCIe 6.0 显卡要从 64 GT/s (PCIe 6.0) 速率下降到 2.5GT/s (PCIe 1.x) 速率以节省空闲时的电量,则链路本身仍将是在 FLIT 模式下运行,而不是回到完整的 PCIe 1.x 样式链接。这既简化了规范的设计(不必重新协商超出链路速率的连接),又允许所有链路速率受益于 FLIT 的低延迟和低开销。

与往常一样,PCIe 6.0 向后兼容早期规范;因此旧设备将在较新的主机上运行,而较新的设备将在较旧的主机上运行。此外,目前的连接器形式仍然受到支持,包括无处不在的 PCIe 卡边缘连接器。因此,虽然对规范的支持需要内置到新一代设备中,但它应该是一个相对简单的过渡,就像前几代技术一样。

不幸的是,PCI-SIG 无法为我们提供太多指导,说明这对实施意味着什么,特别是在消费者系统中——该小组只是制定标准,由硬件供应商来实施。因为切换到 PAM4 意味着给定走线长度的信号损失量没有增加,从概念上讲,放置 PCIe 6.0 插槽应该与放置 PCIe 5.0 插槽一样灵活。也就是说,我们将不得不拭目以待,看看 AMD 和英特尔在未来几年会设计出什么。能够做某事,以及能够在消费者硬件预算上做这件事并不总是一回事。

总结一下,随着 PCIe 6.0 规范最终完成,PCI-SIG 告诉我们,根据之前的采用时间表,我们应该会在 12 到 18 个月内看到符合 PCIe 6.0 的硬件上市。实际上,这意味着我们应该在明年看到第一个服务器设备,然后可能再过一两年用于消费设备。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2918内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!