来源:内容由半导体行业观察(ID:icbank)

编译自

allaboutcircuits

,谢谢。

在最近的一份报告中,中国阿里巴巴表示,其研究中心达摩院已

通过突破性的内存处理 (PIM) 芯片

打破了冯诺依曼瓶颈,

该芯片在 3D 中堆叠内存和逻辑

。

这其实不是大公司第一次转向垂直结构以缩短内存和计算之间的距离。几年前,IBM 发表了关于

3D 堆栈存储器和字节可寻址电阻非易失性存储器 (NVM) 如何为 EE 解决 PIM 的新方法的研究

。

从这个话题,我们看到了 PIM 的研究在大学和主要半导体供应商之间是如何升温的。

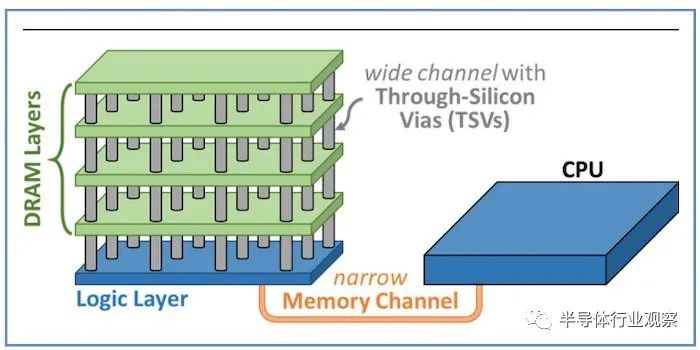

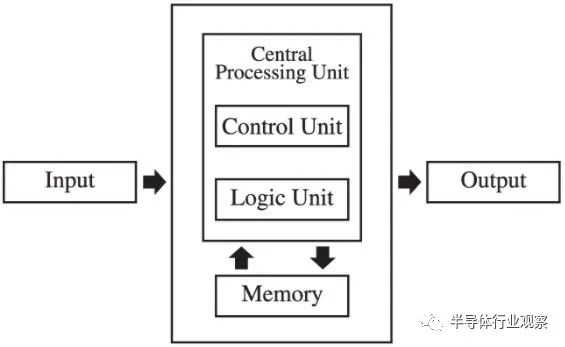

传统的

冯诺依曼计算机体系结构

使用一个子系统进行数据存储,使用另一个子系统进行计算。数据和逻辑是分开的。

要执行操作,必须通过向内存控制器发送内存请求,将数据从 DRAM 存储移动到 CPU,通过窄内存通道进行通信。但是这种从 DRAM 到 CPU 的转移可能会给系统带来主要的瓶颈问题——增加能源消耗,同时减慢多个内存请求的交换速度。这就是系统一直工作的方式,至少自从数字二进制模型被广泛采用以来。

存内

处理式存储器(PIM)模型

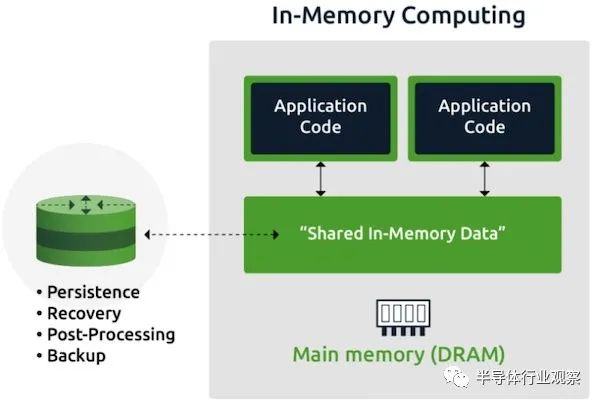

通过合并运算和数据这就是为什么PIM也称为反思冯·诺依曼体系结构 近数据处理。

一些研究小组和公司正在创建 PIM 架构,以使内存处理更接近现实。去年,All About Circuits 讨论了有多少公司发现

内存计算可以在速度、容量和处理方面解决 AI 内存平衡问题

。

这是因为,与数字芯片不同,PIM AI 芯片在模拟领域执行

——Imec 和 Globalfoundries

在最近的 AI 芯片中将其

称为“模拟内存计算(AiMC)”

。

现在,圣路易斯华盛顿大学的一个研究小组,由Xuan“Silvia”Zhang领导,使用电阻代替晶体管,

构建了绕过冯诺依曼架构限制的PIM电路

。存储器和处理器都在电阻器中。组件的这种放置使得从模拟到数字或二进制 (1-0) 的转换变得不必要,并简化了 AI 计算所需的复杂加法和乘法。

PIM 电路不是使用晶体管来打开和关闭栅极并控制电流流动或不流动(创建 1 和 0 的序列),而是通过连接两个电流并通过调整电阻值进行乘法来执行加法。

但是,在某些时候,模拟数据必须转换为数字数据才能融入当今的数字技术。研究人员最初假设这仅需要将 ADC(模数转换)在转换层次结构中进一步向下移动。

然而,该团队发现,引入

神经逼近器可以

提高多个方向上单独转换的电阻列的处理效率:向下、横向或任何其他最大效率方向。

Zhang 的团队做出的最重要的发现是,可以使用单个 ADC 将 RRAM crossbar 列创建的部分和转换为数字格式,无论它们的数量是 18、64 还是 128,从而减少了外边缘的转换次数尽可能。

华盛顿大学的研究结果提出了一个有趣的问题:模拟会推动计算的未来吗?

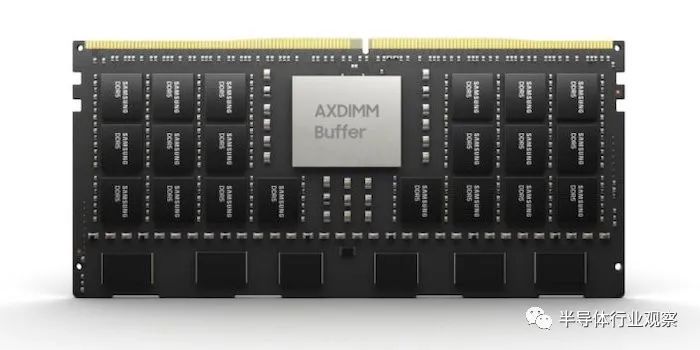

三星最近对内存处理应用的投资

可能会回答这个问题。

三星正试图

通过将高带宽内存 (HBM) 和内存处理与加速器系统集成

来弥合内存和逻辑之间的差距。结果是 HBM-PIM 架构适用于移动和其他商业 DRAM 模块,包括数据中心和超级计算机。

DIMM (AXDIMM) 缓冲芯片(一种可以处理多个内存列的多核处理器)中的加速是通过称为

可编程计算单元 (PCU)

的内置 AI 引擎实现的。据称,该设备可将系统性能提高 2.5 倍,并将能耗降低 60%。

三星已经看到这款 PCU 在图像分类、语音识别和翻译方面取得了可喜的成果。SAP HANA 还与三星合作改进内存数据库管理系统 (IMDBMS)。

随着越来越多的处理需求堆积在嵌入式系统上,尤其是在边缘,制造商正在寻找方法来减少从内存中获取数据的旅行时间。随着 PIM 在学术和行业领域获得越来越多的关注,内存计算可能是一种可行的解决方案——尤其是在三星和 IBM 等知名企业大力推广的情况下。

尽管如此,程序员仍面临着定义与编程模型通信的方式的挑战性任务。这些工程师和系统架构师还必须找到数据分配问题和 PIM 运行时调度的解决方案。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2900内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!