来源:内容由半导体行业观察(ID:icbank)

编译自

「

semianalysis

」,谢谢。

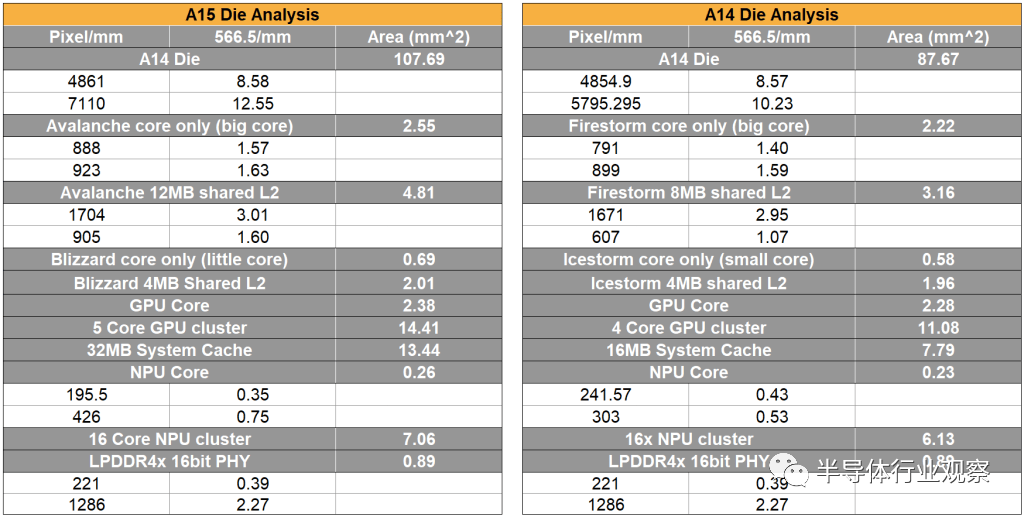

近日,TechInsights 发布了 A15 的die shot,在 SkyJuice 的帮助下,我们今天正在对其进行分析。整体来看,A15的die尺寸从上一代的 87.76mm

2

显着增加到 107.7mm

2

,晶体管也从118亿增加到 150亿。其实在苹果的发布会上,他们对A15的讨论并没有那么令人印象深刻。最令人失望的方面是缺乏 CPU 增加的评价。尽管如此,这一代芯片还是有很多变化。AnandTech已经对 A15 SOC 进行了初步审查,结合芯片分析,可以收集到许多有趣的细节。(查看anandtech的文章,点击

《苹果A15芯片评测:CPU和GPU提升惊人》

查看》。

第一个可以确认的细节是工艺密度没有变化。单个 SRAM 单元保持不变,LPDDR4x PHY 的大小也相同。这可能证实了 Apple 使用的是 N5P 而不是一些推测的 N4 流程。

总芯片面积增加了 22.8%,但不同的 IP 块有所不同。共享级缓存是最大的贡献者。ISP 看起来也经过高度修改,但我们这里没有测量值。NPU 仍然是 16 核,但在架构上对内核和共享逻辑进行了更改,以带来可观的性能提升。尽管大核缺乏IPC收益,但大核还是有一些变化。

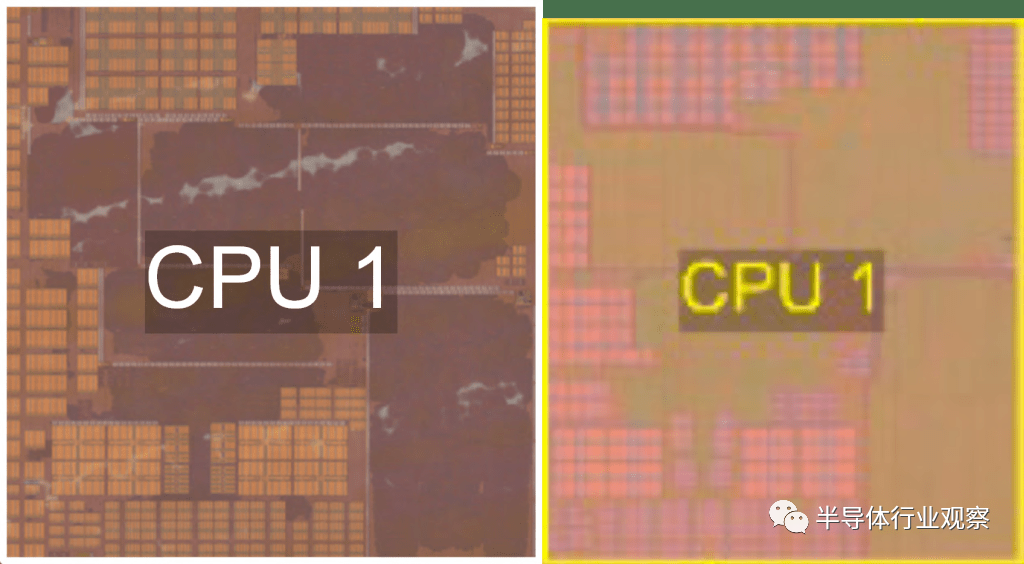

尽管这代芯片是 Apple 产品有史以来最小的 IPC 增益,但其核心显然已重新设计。最大的两个变化与 MMU 和缓存有关。布局明显不同,Core+L1面积增加了15.26%。Anandtech发现 L1 缓存发生了有趣的变化。

在性能核心上,我还看到 L1 速度发生了一些变化,因为它似乎能够对缓存行进行 1 周期访问,只要它们在同一页面中,对缓存行进行相同类型的访问A14 需要 3 个周期。

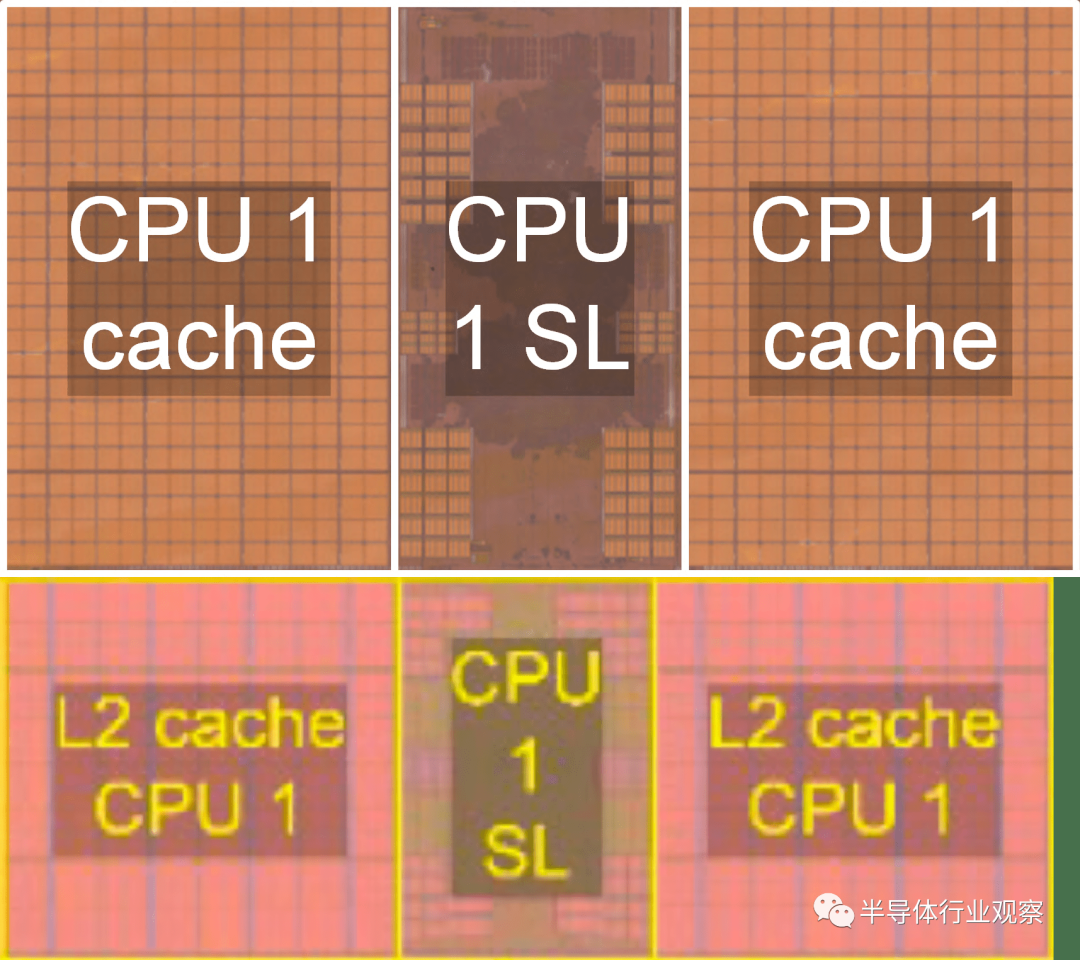

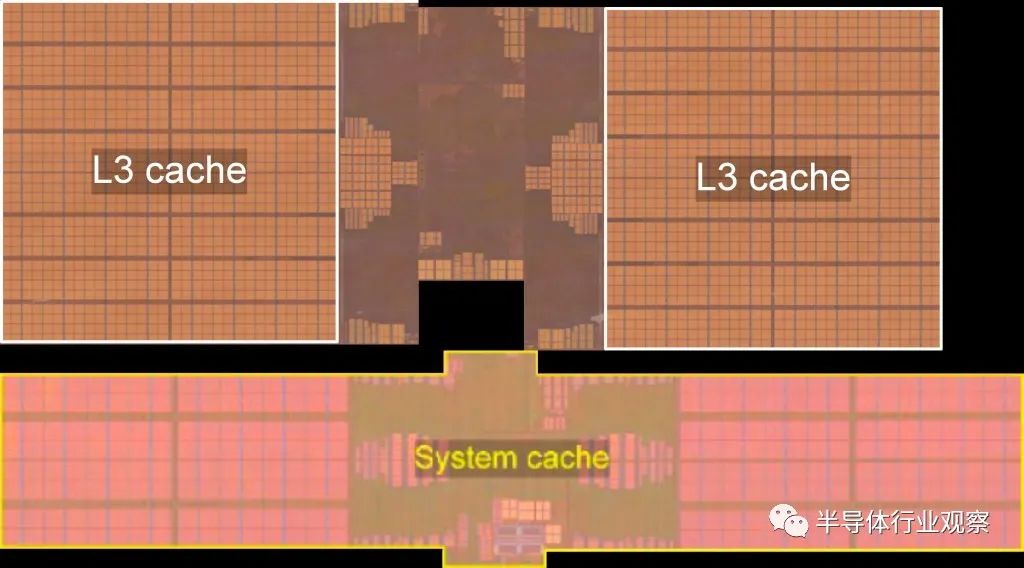

共享 L2 缓存从 8MB 增加到 12MB。尽管有一半的内核,但这与 M1 相同。Anandtech发现访问延迟从 16 个周期增加到 18 个周期。在大小与延迟之间进行权衡似乎非常值得。与 A14 相比,共享 L2 缓存块的大小增加了 52%。

小核心暴雪在规模上增长了18.6%,但性能提升了23%。L2 核心仍为 4MB,但略有增加 2.5%。Apple Blizzard 核心现在的性能与使用 2 年的 Android SOC 中的大型 A76 核心相当。

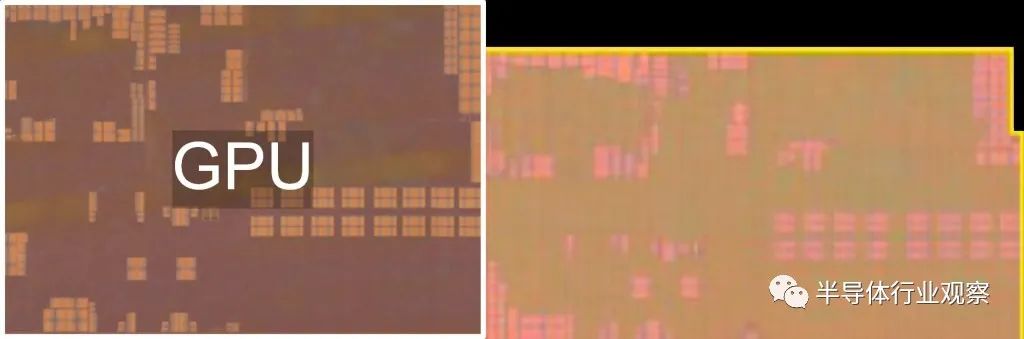

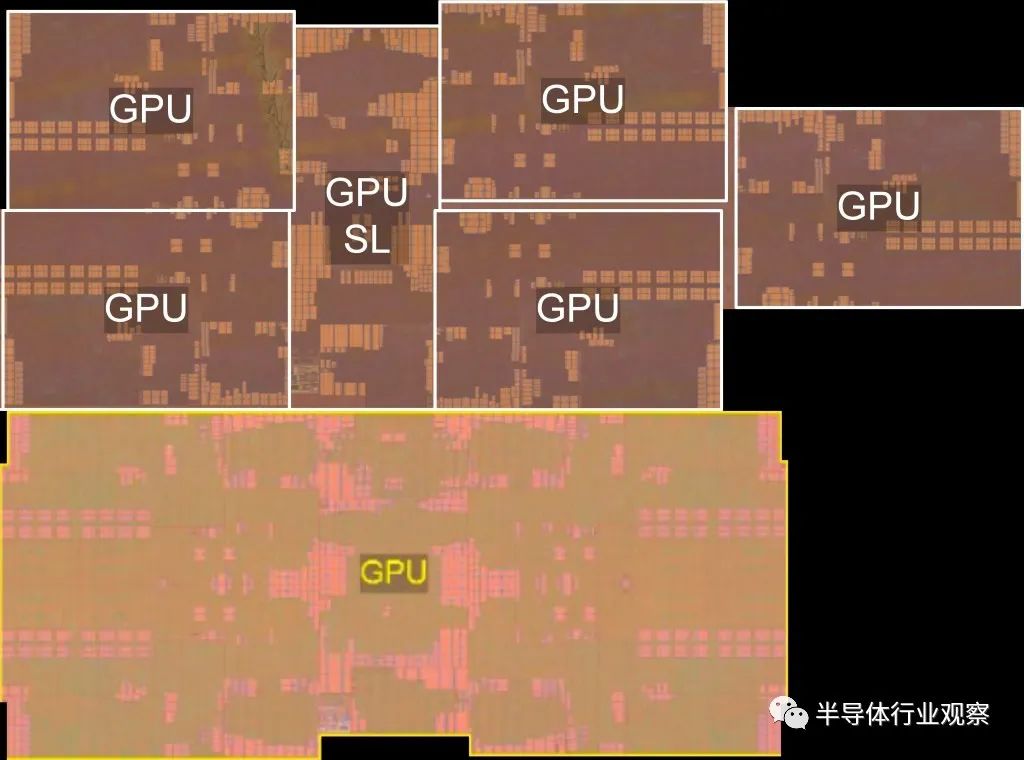

苹果真正专注于 A15 的 GPU。Apple 发布了一下这段视频,其中详细介绍了一些架构变化。其中包括将 M1 GPU 内核中的 FP32 ALU 加倍。Apple 还引入了有损可渲染纹理,可节省内存和带宽,支持稀疏深度和模板纹理,以及新的 SIMD 随机和填充指令。尽管发生了所有这些变化,但内核的大小仅增加了 4.4%。

整个 GPU 的大小增加了 30%。这主要是由于第 5个GPU 核心和对共享逻辑的更改。即使禁用了第5个核心,性能仍然有相当大的提升。尽管内存带宽没有增加,但新的更大的 GPU 实现了巨大的性能提升。苹果似乎正在寻求与 AMD 的 Infinity Cache 类似的策略。

最大的单一区域贡献者是系统缓存。它从 16MB 增加到 32MB。这有助于保持 A15 的各种 IP 块的供给。这篇文章只是 SkyJuice die 分析的一个简短总结。你们还注意到die shot的一部分是什么?请留言讨论!

★ 点击文末

【阅读原文】

,可查看声明原文!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2821内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!