来源:内容由半导体行业观察(ID:icbank)编译自「

designnews

」,谢谢。

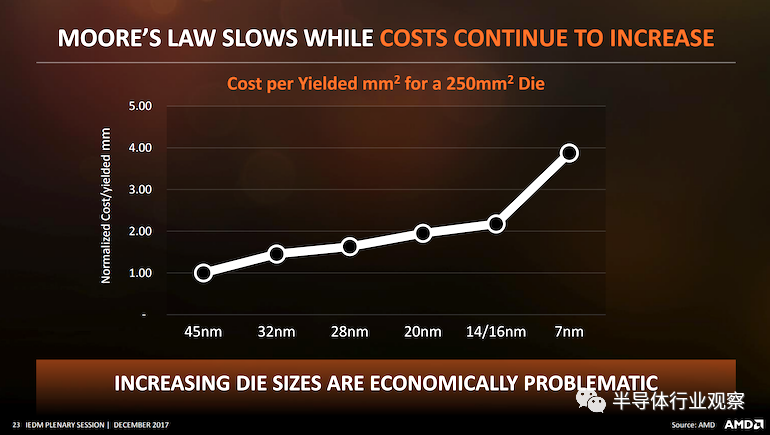

摩尔定律可能还没有死,但它肯定在 28nm 工艺节点之外受到了重大挑战。幸运的是,有一些方法可以扩展摩尔定律的成本、功能和尺寸优势。其中一种方法就是使用chiplet(或模块化管芯),通过将单个硅die替换为多个在统一封装解决方案中协同工作的较小die,从而有效地绕过摩尔定律。

与单片微芯片相比,这种方法提供了更多的硅来添加晶体管。因此,预计小芯片将回到自 1965 年以来一直是半导体业务基石经济的两年翻番周期。

据 Omdia 称,在制造过程中使用小芯片的处理器微芯片的全球市场将在 2024 年扩大到 58 亿美元,比 2018 年的 6.45 亿美元增长九倍。

许多主要的芯片制造商正在将小芯片集成到他们的设计中。例如,

英特尔最近透露了其先进封装战略的新增内容,并推出了两种新的 3D 芯片堆叠技术——Foveros Direct 和 Foveros Omi。到 2023 年,这两种封装技术都将准备好进行大规模生产。前者涉及可以在其上堆叠chiplet的基片。相反,Omni 将允许底部模具与顶部模具的尺寸不同。

小芯片并非没有挑战,但它们确实提供了许多好处。使用小芯片方法,供应商可以从库中的模块化die菜单中进行选择。小芯片可以具有不同的功能和工艺节点,它们可以混合搭配,然后组装在现有的高级封装或新架构中。

是什么推动了小芯片的发展?Kandou创始人兼首席执行官 Amin Shokrollahi博士认为,有五个因素的组合:

1、芯片流片成本上升。mask本身可能价值数百万美元。

2、越来越大的芯片的趋势。一些已经达到了光罩限制,而另一些则刚刚遭受了良率损失。

3、将小芯片绑定在一起的多种技术的可用性,包括精细几何和传统的有机封装基板。

4、需要在特定于该功能的工艺节点和代工厂中拥有每个功能。小芯片允许混合和匹配不同的几何形状和不同的代工厂。

5、需要灵活地提供产品以满足各种市场需求。小芯片使多个产品能够由相同的几个小芯片制成。

芯片设计人员如何为他们的产品利用小芯片封装?虽然重要的半导体 EDA 工具公司提供专有软件,但大多数市场尚无法使用小芯片工具。此外,仍在为这种新兴技术制定标准。但是有一些关键的考虑将有助于今天的设计师。

Shokrollahi 解释说,重要的是要意识到在小芯片之间使用精细几何互连会导致一些产量损失、制造复杂性和整体问题。

“有一些方法可以有效集成小芯片,完全避免使用精细几何互连,”Shokrollahi 说。“使用 SerDes 连接安装在传统有机封装基板上的小芯片可以避免这些问题。低功耗、超短距离 USR/XSR SerDes 是小芯片之间高速互连的首选解决方案。”

仔细地将大芯片细分为tile是一门艺术。做得好,收益会很大。一个常见的错误是拥有一个只有 SerDes 的 I/O 小芯片,这导致该 I/O 小芯片太小,浪费了缩小较大主处理块的机会。Shokrollahi 说,更好的方法是将尽可能多的 I/O 子系统放在 I/O 小芯片上。这可以包括 TCP 卸载、数据包分段、信用管理、前向纠错和成帧块,以及 SerDes。该解决方案需要一个通向 I/O 小芯片的管道,而不仅仅是 SerDes。

处理小芯片通常可以以平铺形式复制。这些tile使不同的产品具有不同数量的小芯片tile。在这个 tile 解决方案中只需要两种类型的小芯片,一种是 tile 小芯片,一种是 I/O 小芯片。路由器结构或环面网络通常被设计为管理彼此不相连的tile之间的连接。

Shokrollahi 指出,OIF(Optical Internetworking Forum ) 的两个项目将为连接小芯片的 SerDes 制定互操作性协议 (IA)。第一个是CEI-112G-MCM(多芯片模块)项目,第二个是CEI-112-XSR项目。MCM项目使用CNRZ-5调制;XSR 项目使用 PAM-4 调制。这两个正在进行的项目具有不同的特性,并以不同的方式进行了优化。基于 MCM IA 的 SerDes 可能具有较低的功率,并且在粗管应用中很有用。基于 XSR IA 的 SerDes 在细管应用中很有用,并且与现有系统更兼容。

使用 SerDes 与这两个 IA 中的任何一个来连接 MCM 内的小芯片可以简化开发,因为它们避免了精细几何互连,例如芯片上晶圆基板 ( CoWoS ) 或 INFO,Shokrollahi 表示。SerDes 实现的延迟比在细间距interposer上使用导线的延迟略高。然而,低速互连的慢时钟速率意味着这些解决方案可能具有至少两个慢时钟的延迟。SerDes 解决方案还具有必须解决的错误率。XSR PAM-4 SerDes 实现旨在通过传统的前向纠错 (FEC) 块提高 1E-9 的原始错误率。MCM CNRZ-5 SerDes 实现旨在通过最小的低延迟 FEC 将原始错误率提高到 1E-15。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2806内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!