[原创] 高级封装将成为“芯”救世主?

2021-09-13

14:00:03

来源: 半导体行业观察

在今年芯片工业界最重要的会议之一HOTCHIPS上,高级封装成为了最热门的议程之一,Intel、TSMC、AMD等业界巨头都纷纷亮相。事实上,高级封装正在逐渐取代晶体管特征尺寸缩小,而在成为新的芯片进步的驱动力。

在过去的数十年中,半导体业界公认的主要技术进步推动力是摩尔定律,即周期性地缩小半导体工艺的特征尺寸,从而提升芯片集成度,降低成本,并且提高芯片性能。值得注意的是,降低特征尺寸能降低整体成本是摩尔定律能维持的首要经济学逻辑,正是它推动了半导体行业几十年来的高速发展。

然而,在近几年中,随着半导体工艺的特征尺寸缩小逐渐接近饱和,再进一步缩小半导体特征尺寸在降低成本方面的获益已经越来越小(新工艺研发成本极高,导致mask一次性NRE成本过高,仅仅只有极少数芯片公司能从新工艺中获取成本收益),同时在性能提升方面的收益也越来越小。这个时候,高级封装就成了延续半导体进步的新驱动力。

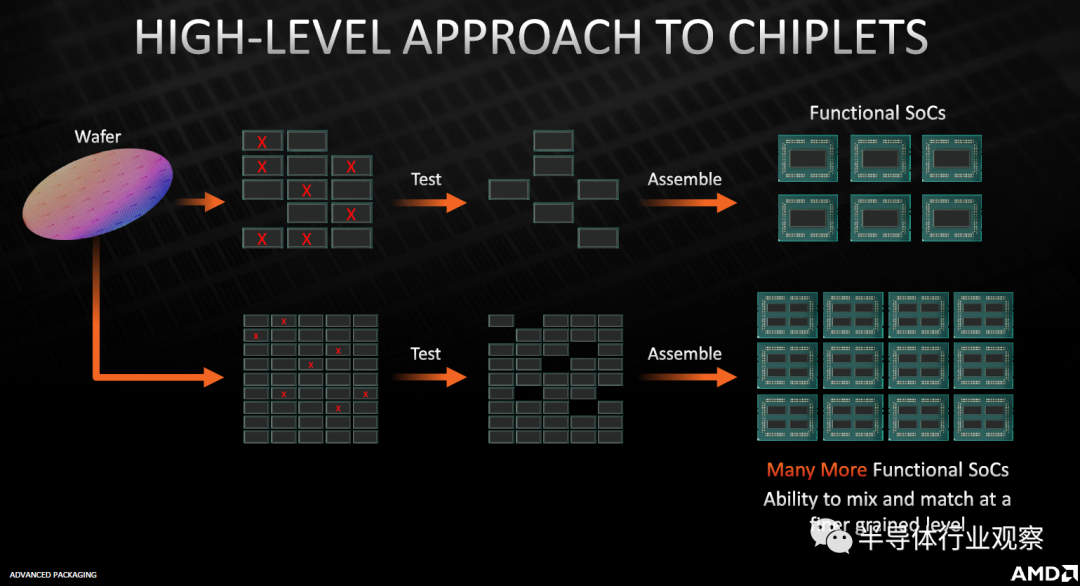

高级封装最关键的能力在于提供了一条进一步提升芯片集成度并且降低成本的技术路径。与摩尔定律试图缩小晶体管体征尺寸以提升芯片上晶体管数量并提升集成度不同,高级封装技术使用封装的形式来提升集成度,并不需要缩小晶体管特征尺寸,因此避开了半导体工艺上一些最难啃的骨头。除此之外,高级封装还通过chiplet(芯片粒)的方式进一步提升先进工艺下的芯片良率并降低成本,这一点更进一步地强化了高级封装技术演进背后的经济学动力。在传统的SoC中,如果由于半导体工艺导致的某一个地方出现了瑕疵,那么整个SoC芯片就无法使用。举例来说,如果整个晶圆上一次能生产10块大型SoC,同时在成产过程中出现了两个瑕疵分布在两块不同的SoC上,那么就只剩下8块SoC可以用了,良率为80%。这个良率问题在最新半导体工艺中尤其严重。另一方面,如果我们把SoC拆成很多面积较小的chiplet(例如一块晶圆上可以生产20个这样的chiplet),那么扣除两个因瑕疵无法使用的chiplet之后,仍然有18个chiplet可以使用,良率就提升到了90%。在之后,可以使用高级封装技术把多个chiplet互联并封装到一起,能实现和大型SoC一样的集成度和性能。从这个例子中我们可以看出,高级封装技术能够在提升集成度的同时降低成本,从而维护了摩尔定律的基本逻辑。

除了提升集成度和降低成本之外,高级封装还能提供更高的性能。在人工智能和高性能计算成为半导体市场主要引擎的时代,我们认为IO密度,尤其是计算逻辑和存储单元之间的IO密度和通信带宽,已经成为了决定计算性能的主要因素。在这样的情况下,高级封装能提供远超传统方式的IO密度和通信带宽,从而能进一步驱动芯片系统的性能。

如上所述,在今天,高级封装已经能完全实现当年摩尔定律背后的几大要素:提升集成度,降低成本,以及提升性能,因此它在今天已经成为半导体行业公认的新驱动力。最积极推动高级封装的厂商包括Intel,以及AMD和TSMC的联盟,而Intel和AMD恰恰是目前高性能计算的最主流厂商,这也和符合我们之前分析的高级封装带来的芯片系统性能提升对于高性能计算应用获益最大。

高级封装的“摩尔定律”

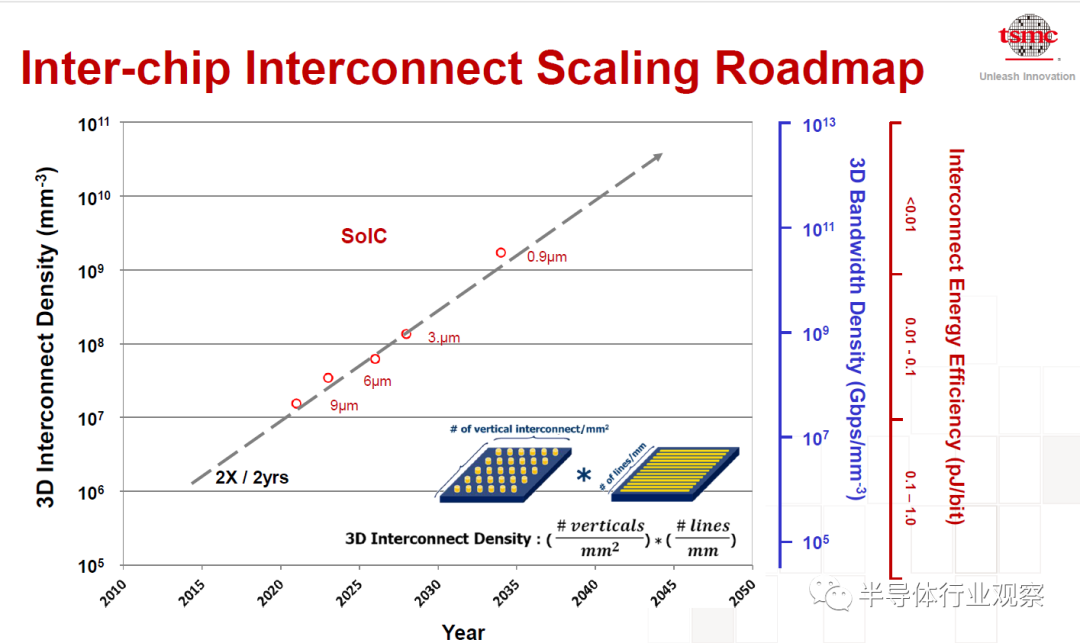

在上一代摩尔定律中,集成度、成本、性能等多个因素最后都转换成了一个指标即特征尺寸,那么在高级封装领域有没有类似的单一代表性指标呢?我们认为,在高级封装领域,这个指标就是芯片间互联的间距。

随着芯片间互联间距的降低,芯片间的IO密度提升,同时芯片间通信的带宽也相应提升。在高级封装时代,由于主要的推动力和推动厂商来自于高性能计算领域,因此高级封装对于芯片系统性能带来的提升得到了更多关注。而如前所述,IO密度和通信带宽恰恰是高级封装给芯片系统带来性能提升的关键,而这样的性能提升都可以归结到芯片间互联的间距这个指标上。

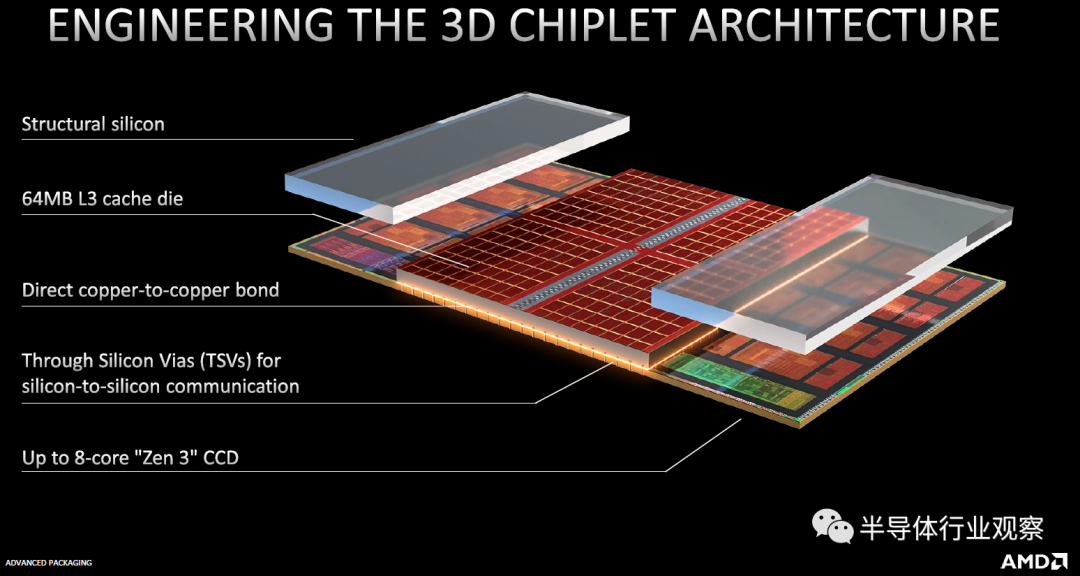

除此之外,芯片间互联还将影响高级封装系统的集成度和集成颗粒度。AMD在今年的HOTCHIPS上的演讲中,提出了随着芯片间互联间距的减小,高级封装之间芯片堆叠的颗粒度也会越来越细,从之前的处理器核之间的堆叠,逐渐继续细化到IP和IP之间的堆叠,以及更进一步把单个IP拆到不同的堆叠芯片间,直至实现晶体管颗粒度的堆叠。这样的进一步细分可以拥有传统2D集成电路无法实现的能力(例如不同IP之间通过3D堆叠可以大大降低走线长度),从而最终实现传统2D电路无法实现的集成度。

而高级封装中芯片间互联间距的路线图,TSMC也在今年的HOTCHIPS上给出了规划,即满足互联密度每两年翻一倍。这样一来,高级封装的摩尔定律的所有要素都已经齐全:半导体芯片进化的方向,背后的经济学逻辑,关键指标,以及技术演进时间规律(两年翻一番)。我们认为,高级封装的摩尔定律将会在芯片集成度和性能方面慢慢获得更多的权重,最终实现和半导体器件特征尺寸的摩尔定律一起成为下一代半导体行业的演进规律。

高级封装的竞争格局

如前所述,目前高级封装的市场上,高性能计算处理器芯片厂商是主要的玩家,其中就包括了负责芯片、工艺和封装设计的Intel,而另一方面AMD则和TSMC结成了联盟,共同开发高级封装技术以及相关的芯片设计。

目前,Intel和AMD+TSMC的技术路线基本都已经到了2.5D+3D混合系统集成的阶段。所谓的2.5D+3D混合集成,首先使用3D堆叠技术实现多个chiplet的纵向堆叠,之后再把多个经过纵向堆叠的chiplet再使用2.5D封装技术集成在一起。

AMD通过与TSMC合作,早在几年前就实现了基于2.5D封装的chiplet技术(Zepplin),而在今年早些时候更是发布了基于2.5D+3D混合系统集成的3D Chiplet技术,实现了大容量缓存和处理器芯片粒的3D+2.5D集成,其原型芯片在游戏等高性能应用中获得了显著的性能增益。TSMC无论是2.5D封装(InFO和CoWoS)还是3D堆叠技术(SOIC)都处于领先地位,而AMD通过与TSMC的深度合作可望也能实现芯片性能的领先地位。

Intel方面,其2.5D技术是EMIB,通过把互联优化集中在芯片互联边缘处以优化成本,而其3D堆叠技术则是Foveros。今年Intel也公布了其下一代混合2.5D+3D的芯片Ponte Vecchio,通过集成近50个芯片粒,实现超1000亿晶体管的超高集成度。

Ponte Vecchio计划可谓是雄心勃勃,但是如果我们量化比较AMD+TSMC和Intel的高级封装技术,尤其是比较两者最关键的指标——互联间距,我们仍然可以看出AMD+TSMC领先一些。在AMD+TSMC已经完成的3D Chiplet原型芯片中,其芯片互联间隔仅为9um;相对而言,Ponte Vecchio中使用的芯片互连间距为36um。Intel预计在其下一代Foveros Omni中把互联间距减小到25um,而到达9um则要在更下一代的Foveros Direct。由此,我们认为在未来几年内,AMD和TSMC的高级封装技术仍将保持领先状态,而在这之后的竞争格局,我们还需拭目以待。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2796内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|台积电|AI|封装

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie