谈谈LDO,如何延长电池寿命?

来源:内容由半导体行业观察(ID:icbank)编译自「

IEEE

spectrum

」,谢谢。

您可能已经在智能手机上播放了数百个甚至数千个视频。但是你有没有想过按下“播放”会发生什么?

当你触摸那个小三角形的那一刻,很多事情同时发生。在几微秒内,手机 处理器 上空闲的计算核心就会 恢复生机。当他们这样做时,他们的电压和时钟频率会上升,以确保视频解压缩和显示没有延迟。同时,在后台运行任务的其他内核会降低速度。电荷涌入活动内核的数百万个晶体管,并在新闲置的晶体管中缓慢流淌。

这种称为 动态电压和频率缩放 (DVFS) 的舞蹈 在称为片上系统 (SoC) 的处理器中持续发生,该处理器运行您的手机和笔记本电脑以及支持它们的服务器。这一切都是为了平衡计算性能和功耗,这对智能手机来说尤其具有挑战性。尽管电流激增,协调 DVFS 的电路仍努力确保稳定的时钟和坚如磐石的电压水平,但它们也是设计中最麻烦的。

这主要是因为时钟生成和电压调节电路是模拟的,与智能手机 SoC 上的几乎所有其他电路不同。由于半导体制造的进步,我们已经习惯于几乎每年都会推出具有更多计算能力的新处理器。将数字设计从旧的半导体工艺“移植”到新的工艺并不是野餐,但与尝试将模拟电路转移到新工艺相比,这不算什么。支持 DVFS 的模拟组件,尤其是一种称为低压降稳压器 (LDO) 的电路,不会像数字电路那样按比例缩小,而且基本上每代产品都必须从头开始重新设计。

如果我们可以用数字元件构建 LDO——或许还有其他模拟电路——它们的移植难度将远低于处理器的任何其他部分,从而显着节省设计成本,并使工程师能够解决尖端芯片设计等其他问题有在商店。更重要的是,由此产生的数字 LDO 可能比模拟 LDO 小得多,并且在某些方面表现更好。在过去的几年里,工业界和学术界的研究小组至少测试了十几种设计,尽管存在一些缺陷,但商业上有用的数字 LDO 可能很快就会实现。

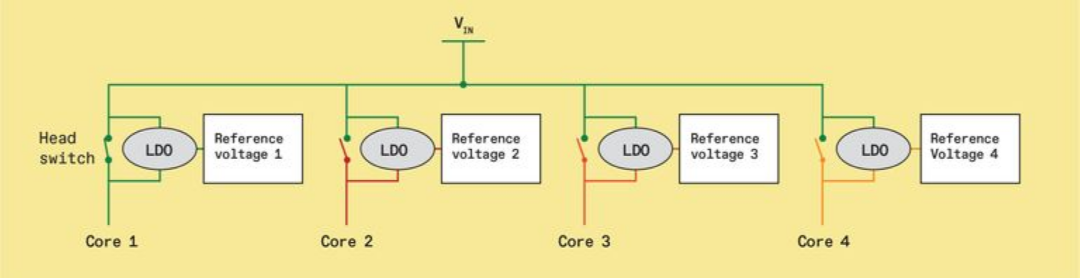

低压降稳压器 (LDO) 允许同一输入电压轨 (V IN )上的多个处理器内核根据其工作负载在不同电压下运行。在这种情况下,Core 1 具有最高的性能要求。它的头部开关,实际上是一组并联的晶体管,关闭,绕过 LDO 并将 Core 1 直接连接到 V IN,该V IN由外部电源管理 IC 供电。但是,内核 2 到 4 的工作负载要求较低。它们的 LDO 用于为内核提供电压以节省功耗。

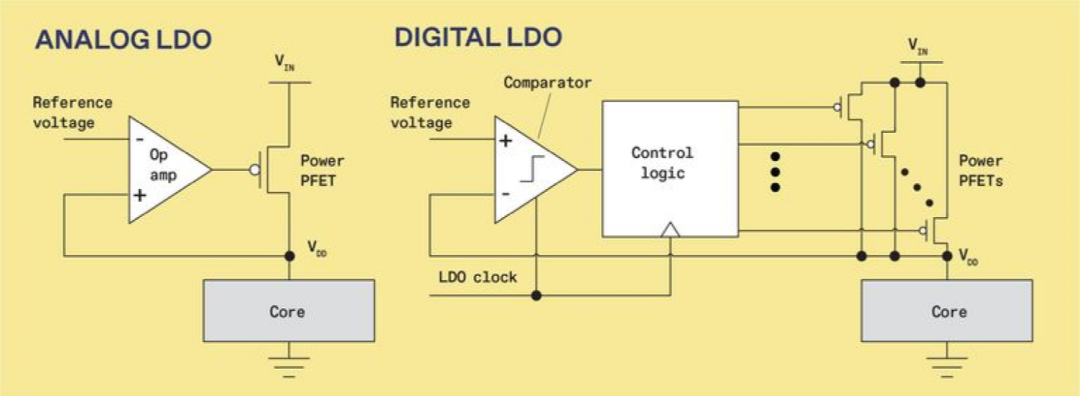

基本模拟低压降稳压器 [左] 通过反馈回路控制电压。它试图通过控制通过功率 PFET 的电流使输出电压 (V DD ) 等于参考电压。在基本数字设计 [右] 中,独立时钟触发比较器 [三角形],将参考电压与 V DD进行比较。结果告诉控制逻辑要激活多少个功率 PFET。

用于智能手机的典型片上系统是 集成 的奇迹. 它在单片硅片上集成了多个 CPU 内核、图形处理单元、数字信号处理器、神经处理单元、图像信号处理器以及调制解调器和其他专用逻辑块。自然地,提高驱动这些逻辑块的时钟频率会增加它们完成工作的速度。但要以更高的频率运行,它们还需要更高的电压。否则,晶体管无法在处理器时钟的下一个滴答声之前打开或关闭。当然,更高的频率和电压是以功耗为代价的。因此,这些内核和逻辑单元会动态地改变它们的时钟频率和电源电压——通常在 0.95 到 0 的范围内。

通常,外部电源管理 IC 会为手机的 SoC生成多个输入电压 (V IN ) 值。这些电压沿着称为轨道的宽互连传送到 SoC 芯片的区域。但是电源管理芯片和 SoC 之间的连接数量是有限的。因此,SoC 上的多个内核必须共享相同的 V IN轨。

但由于低压差稳压器,它们不必都获得相同的电压。LDO 和专用时钟发生器允许共享轨道上的每个内核以独特的电源电压和时钟频率运行。需要最高电源电压的内核决定了共享的 V IN值。电源管理芯片将 V IN设置为该值,该内核通过称为头部开关的晶体管完全绕过 LDO。

为了将功耗降至最低,其他内核可以在较低的电源电压下运行。软件确定该电压应该是多少,模拟 LDO 在提供它方面做得非常好。它们结构紧凑、构建成本低,并且集成在芯片上相对简单,因为它们不需要大型电感器或电容器。

但是这些 LDO 只能在特定的电压窗口中运行。在高端,目标电压必须低于 V IN与 LDO 本身的压降(同名的“压降”电压)之间的差值。例如,如果内核最有效的电源电压为 0.85 V,但 V IN为 0.95 V 且 LDO 的压差为 0.15 V,则该内核无法使用 LDO 达到 0.85 V,必须在相反,0.95 V,浪费了一些电力。同样,如果 V IN已经设置在某个电压限制以下,LDO 的模拟组件将无法正常工作,并且电路无法进一步降低内核电源电压。

迄今为止,限制使用数字 LDO 的主要障碍是缓慢的瞬态响应。

但是,如果所需电压落在 LDO 的窗口内,软件会启用电路并激活一个等于目标电源电压的参考电压。

LDO 如何提供正确的电压?在基本的模拟 LDO 设计中,它是通过运算放大器、反馈和专用功率p沟道场效应晶体管 (PFET) 实现的。后者是一种晶体管,随着其栅极电压的增加而降低其电流。该功率 PFET 的栅极电压是来自运算放大器的模拟信号,范围从 0 伏到 V IN。运算放大器不断将电路的输出电压(内核的电源电压或 V DD)与目标参考电压进行比较。

如果 LDO 的输出电压低于参考电压——就像当新的活动逻辑突然需要更多电流时一样——运算放大器会降低功率 PFET 的栅极电压,增加电流并提升 V DD向参考电压值。相反,如果输出电压上升到高于参考电压——就像当内核逻辑不太活跃时一样——那么运算放大器会增加晶体管的栅极电压以减少电流并降低 V DD。

另一方面, 基本 数字LDO 由电压比较器、控制逻辑和多个并联功率 PFET 组成。(LDO 也有自己的时钟电路,与处理器内核使用的时钟电路分开。)在数字 LDO 中,电源 PFET 的栅极电压是二进制值,而不是模拟值,0 V 或 V IN。

每次时钟滴答时,比较器都会测量输出电压是低于还是高于参考源提供的目标电压。比较器输出指导控制逻辑确定要激活多少个功率 PFET。如果 LDO 的输出低于目标,控制逻辑将激活更多功率 PFET。它们的组合电流支持内核的电源电压,该值反馈到比较器以使其保持目标。如果它过冲,比较器会向控制逻辑发送信号以关闭一些 PFET。

当然,模拟和数字 LDO 都不是理想的。模拟设计的主要优势在于它可以快速响应电源电压的瞬态下降和过冲,这在这些事件涉及急剧变化时尤为重要。这些瞬变的发生是因为内核对电流的需求可以在几纳秒内大幅上升或下降。除了快速响应之外,模拟 LDO 还非常擅长抑制可能来自电源轨上其他内核的V IN变化。最后,当电流需求变化不大时,它会严格控制输出,而不会以在 V DD中引入纹波的方式不断地过冲和下冲目标。

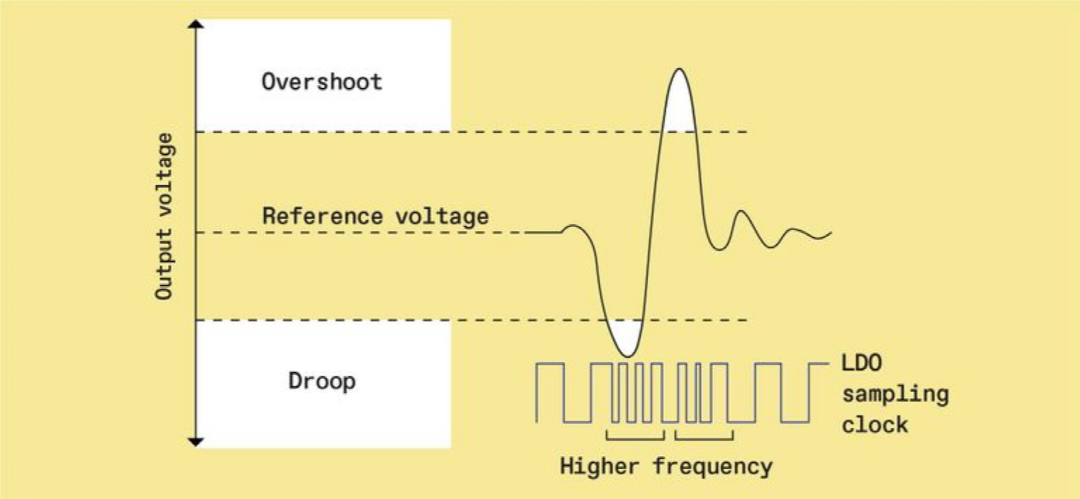

当内核的电流需求突然变化时,可能会导致 LDO 的输出电压过冲或下降 [top]。基本的数字 LDO 设计不能很好地处理这个问题 [左下]。然而,一种称为动态稳定性降低的自适应采样方案 [右下] 可以减少电压偏移的程度。当下降过大时,它通过提高 LDO 的采样频率来实现这一点,从而使电路响应更快。 来源: SB NASIR 等人,IEEE 国际固态电路会议 (ISSCC),2015 年 2 月,第 98-99 页 。

这些特性使模拟 LDO 不仅对为处理器内核供电,而且对几乎所有需要安静、稳定电源电压的电路都具有吸引力。然而,有一些关键挑战限制了这些设计的有效性。第一个模拟组件比数字逻辑复杂得多,需要很长的设计时间才能在先进的技术节点中实现它们。其次,当 V IN低时,它们无法正常运行,从而限制了它们可以提供给内核的VDD多低。最后,模拟 LDO 的压降并不像设计人员希望的那么小。

综合考虑最后几点,模拟 LDO 提供了一个有限的电压窗口,它们可以在其中运行。这意味着错失了启用 LDO 以实现节能的机会——大到足以显着改善智能手机电池寿命的机会。

数字 LDO 消除了许多这些弱点:由于没有复杂的模拟组件,它们允许设计人员利用大量工具和其他资源进行数字设计。因此,为新工艺技术缩小电路将需要更少的努力。数字 LDO 还将在更宽的电压范围内工作。在低电压端,数字组件可以在 V IN值下运行,这是模拟组件的禁区。在更高的范围内,数字 LDO 的压差会更小,从而显着节省内核功耗。

但没有什么是免费的,而且数字 LDO 有一些严重的缺点。其中大部分是因为电路仅在离散时间而不是连续时间测量和改变其输出。这意味着电路对电源电压下降和过冲的响应相对较慢。它对 V IN 的变化也更敏感,并且往往会在输出电压中产生小的纹波,这两种情况都会降低内核的性能。

其中,迄今为止限制使用数字 LDO 的主要障碍是它们缓慢的瞬态响应。当它们汲取的电流响应其工作负载的变化而突然变化时,核心会经历下垂和过冲。

LDO 对下降事件的响应时间对于限制电压下降的程度以及这种情况持续的时间至关重要。传统内核为电源电压增加了一个安全裕度,以确保在下降期间正确运行。更大的预期下降意味着余量必须更大,从而降低 LDO 的能效优势。因此,加快数字 LDO 对下垂和过冲的响应是该领域前沿研究的主要焦点。

最近的一些进展有助于加快电路对下垂和过冲的响应。一种方法使用数字 LDO 的时钟频率作为控制旋钮,以牺牲稳定性和功率效率来换取响应时间。

较低的频率可提高 LDO 稳定性,这仅仅是因为输出不会经常变化。它还降低了 LDO 的功耗,因为构成 LDO 的晶体管的开关频率较低。但这是以对来自处理器内核的瞬态电流需求的响应较慢为代价的。如果您考虑到如果频率太低,很多瞬态事件可能会在单个时钟周期内发生,您就会明白为什么会这样。

相反,高 LDO 时钟频率会减少瞬态响应时间,因为比较器对输出进行采样的频率足以在瞬态事件中更早地改变 LDO 的输出电流。但是,这种恒定采样会降低输出的稳定性并消耗更多功率。

这种方法的要点是引入一个频率适应情况的时钟,一种称为动态稳定性降低的自适应采样频率的方案。当电压下降或过冲超过一定水平时,时钟频率增加以更快地降低瞬态效应。然后它会减慢速度以消耗更少的功率并保持输出电压稳定。这个技巧是通过添加一对额外的比较器来检测过冲和下降条件并触发时钟来实现的。在使用这种技术的测试芯片的测量中,V DD压降从 210 毫伏降低到 90 毫伏——与标准数字 LDO 设计相比降低了 57%。电压稳定到稳态所需的时间从 5.8 µs 缩短到 1.1 微秒,提高了 81%。

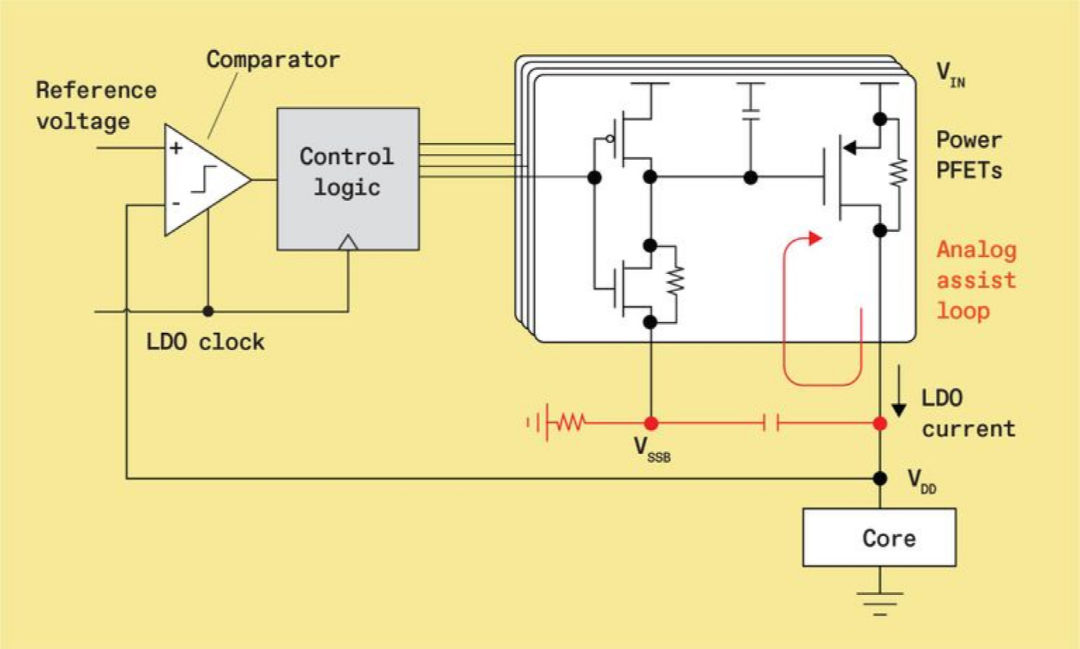

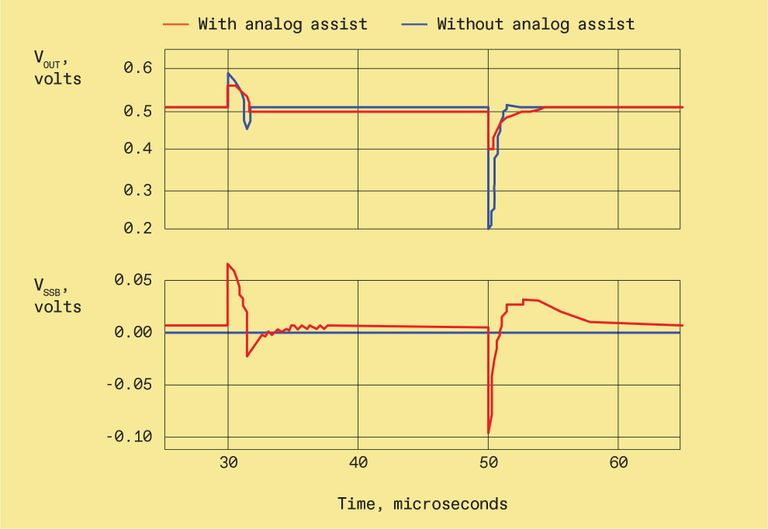

改善瞬态响应时间的另一种方法是使数字 LDO 有点模拟。该设计集成了一个独立的模拟辅助环路,可立即响应负载电流瞬变。模拟辅助环路通过一个电容器将 LDO 的输出电压耦合到 LDO 的并联 PFET,从而形成一个仅在输出电压发生急剧变化时才起作用的反馈环路。

因此,当输出电压下降时,它会降低激活的 PFET 栅极上的电压并立即增加流向内核的电流以降低下降幅度。这种模拟辅助环路已被证明可以将下降从 300 mV 降低到 106 mV,提高 65%,并将过冲从 80 mV 降低到 70 mV(13%)。

使数字 LDO 更快响应压降的另一种方法是在电路的功率 PFET 部分添加一个模拟反馈回路 [顶部]。当输出电压下降或过冲时,模拟回路会起作用以支撑它[底部],从而减少偏移的范围。 资料来源: M. HUANG 等人,IEEE 固态电路杂志,2018 年 1 月,第 20-34 页 。

当然,这两种技术都有其缺点。一方面,两者都无法真正匹配当今模拟 LDO 的响应时间。此外,自适应采样频率技术需要两个额外的比较器以及下垂和过冲参考电压的生成和校准,因此电路知道何时使用更高的频率。模拟辅助回路包括一些模拟组件,降低了全数字系统的设计时间优势。

商业 SoC 处理器的发展可能有助于使数字 LDO 更加成功,即使它们不能完全匹配模拟性能。今天,商用 SoC 处理器集成了全数字自适应电路,旨在缓解出现下降时的性能问题。例如,这些电路会临时延长内核的时钟周期以防止时序错误。这种缓解技术可以放宽瞬态响应时间限制,允许使用数字 LDO 并提高处理器效率。如果发生这种情况,我们可以期待更高效的智能手机和其他计算机,同时使设计过程变得更加容易。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2780内容,欢迎关注。

推荐阅读

★ 台积电的另一面

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|MLCC|英伟达|模拟芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!