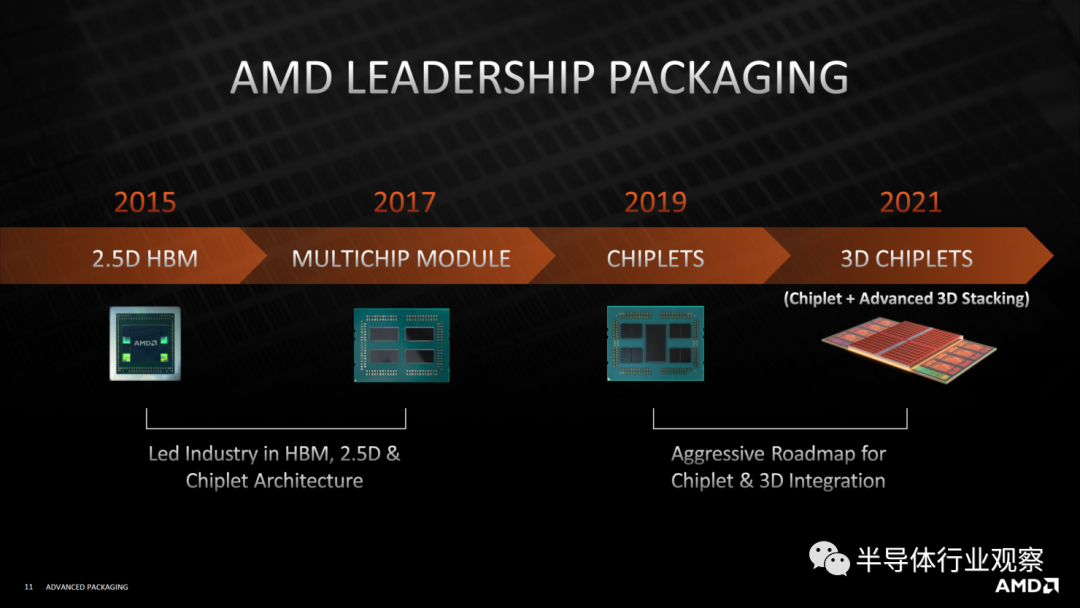

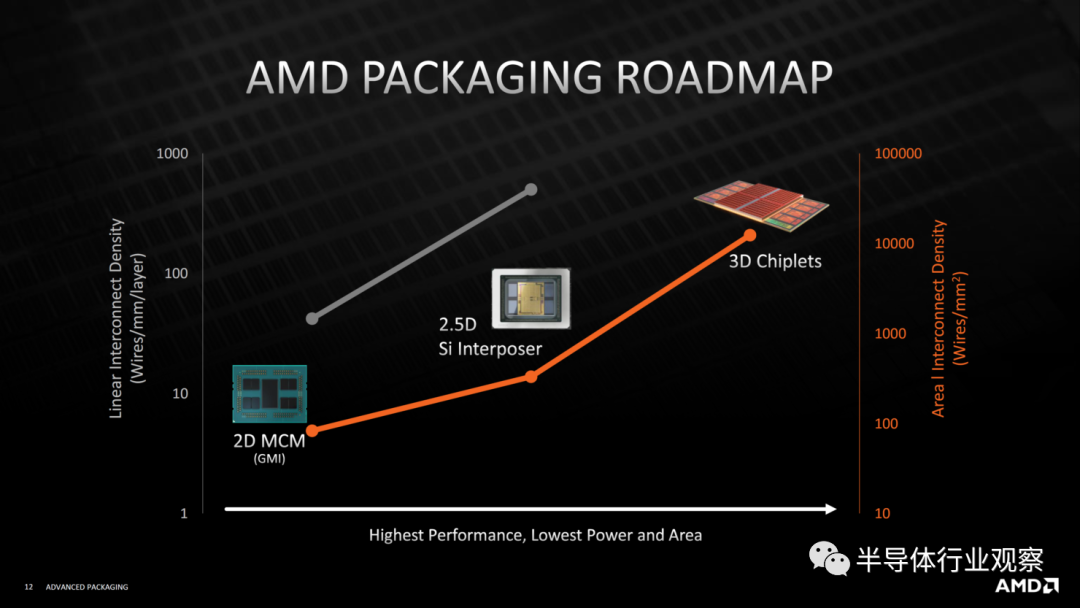

AMD全面进入3D Chiplet时代

来源:内容由半导体行业观察(ID:icbank)编译自「 wccftech 」,谢谢。

★ 点击文末 【阅读原文】 ,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2775内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|MLCC|英伟达|模拟芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 MediaTek 发布天玑 8400 移动芯片,开启高阶智能手机全大核计算时代

- 2 探索智慧实践,洞见AI未来!星宸科技2024开发者大会暨产品发布会成功举办

- 3 国产EDA突破,关键一步

- 4 共筑国产汽车芯片未来,中国汽车芯片联盟全体大会即将开启