来源:内容由半导体行业观察(ID:icbank)编译自「

semiwiki

」,谢谢。

在今年的VLSI研讨会上,一个引人注目的短期课程是:“面向 2nm-CMOS 和新兴存储器的先进工艺和器件技术”。本文重点介绍了台积电研发团队在题为“未来十年的 CMOS 器件技术”的短期课程中介绍的材料。

连续几代 FinFET 工艺技术的发展导致鳍片间距更小,鳍片更高,鳍片侧壁轮廓越来越垂直。并且已经实现了单位面积驱动电流的显着改进。垂直鳍片三个表面上栅极输入的静电控制也改善了亚阈值漏电流。

然而,台积电的Jin 强调说,“垂直鳍中的自由载流子迁移率会因鳍厚度变小而受到不利影响。TSMC 在 N5 节点引入了 SiGe(用于 pFET),以提高迁移率。应变工程仍然是 FinFET 制造的一个关键方面。”

(nFET:拉伸应变;pFET:压缩应变)

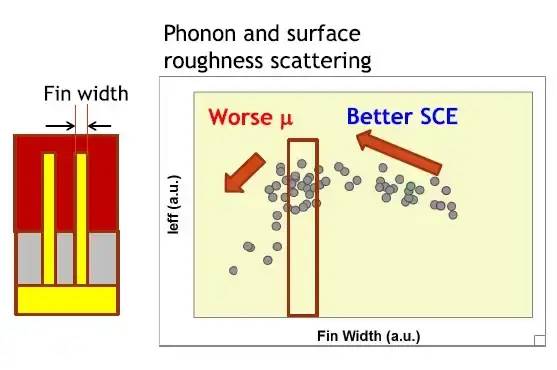

下图说明了短沟道效应和载流子迁移率与鳍宽度的趋势。

Jin 继续说道,“最佳工艺目标是~40-50nm 鳍片高度、~6nm 鳍片厚度和~15nm 栅极长度,或鳍片厚度的 2.5 倍。”

器件缩放的下一步是水平环栅或“纳米片”(NS) 配置。在晶片衬底上制造交替的 Si 和 SiGe 层的超晶格。一组独特的蚀刻/沉积步骤用于去除 NS 层边缘的 SiGe 材料,并在凹陷区域沉积隔离氧化物,使 Si 层侧壁暴露。然后源极/漏极外延从 Si 侧壁向外生长,为 Si 纳米片提供 S/D 掺杂和结构支撑。然后选择性地去除纳米片堆叠中的 SiGe 层,暴露出 Si 通道。随后的原子层沉积 (ALD) 步骤引入了栅极氧化物堆叠,可能具有用于器件 Vt 产品的多种功函数。另一个 ALD 步骤提供栅极材料,完全封装纳米片堆叠。

Jin 专注于基于纳米片的 GAA 器件的载流子迁移率特性,作为性能的代表。(稍后将详细介绍 GAA 寄生电容和电阻。)下图提供了 GAA 器件的晶体取向说明,以优化水平纳米片层通道中的横向迁移率。

Jin 强调了 NS 工艺技术发展面临的一个关键问题——(未优化的)空穴迁移率明显低于 nFET 电子迁移率,如下图所示。

当 CMOS 技术首次被引入时,强反型中的 nFET 电子和 pFET 空穴迁移率存在相当大的差异。通用电路设计目标是提供“平衡”的 RDLY 和 FDLY 延迟(和信号转换)值,这对于时钟分配网络中的任何电路尤其重要。因此,逻辑电路采用了器件尺寸指南,其中 Wp/Wn 与载流子迁移率成反比 - 即 Wp/Wn ~ mu_electron/mu_hole。例如,通常使用大小为 ~2.5 的“beta 比率”的设备。

(Wp 和 Wn 是“有效”设计值——对于具有多个串联器件的逻辑电路分支,要保持相同的有效驱动强度,需要更宽的器件。)

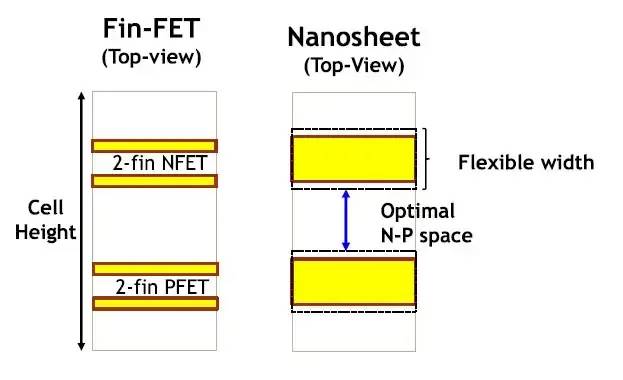

随着工艺技术在氧化物表面下方采用更薄的沟道,以及广泛的通道应变工程,电子和空穴迁移率之间的比率降低,接近统一。事实上,如下图所示,具有量化宽度值的 FinFET 器件的引入取决于载流子迁移率差异的减少。(想象一下,在下面显示的 2+2 鳍标准单元图像中尝试设计具有非整数 Beta 比率的逻辑电路。)

上图描绘了当前 FinFET 和即将推出的纳米片技术的标准单元库图像。与每个鳍的量化宽度(Wfin ~ 2*Hfin + Tfin)不同,纳米片器件宽度是一个连续的设计参数,并且(幸运地)可以更容易地适应独特的 Beta 比率。

请注意,最大纳米片器件宽度会有限制。选择性去除交错的 SiGe 超晶格层以及氧化物和栅极材料的沉积的工艺步骤需要产生高度均匀的表面和尺寸,这对于更宽的纳米片堆叠将更加困难。

说到纳米片堆叠,还应注意布局器件宽度乘以纳米片层数。Jin 介绍了评估潜在层范围的深入分析的结果,如下所示。

更多的层会增加驱动电流,但通过 S/D 区域到较低层的(分布式)接触电阻会降低这种增益。大多数已发表的关于纳米片技术的研究都集中在~3-4 层上,以实现最佳效率。

顺便说一句,也有已发表的研究调查纳米片制造工艺技术,这些技术将在周围氧化物和栅极的 ALD 之前局部去除一个(或多个)纳米片层,用于一组特定的器件。换句话说,一些设备可以包含少于 3 层。考虑弱器件强度最佳的电路应用,例如泄漏节点“保持器”或 6 晶体管 SRAM 位单元中的上拉器件。然而,由此产生的不均匀表面形貌增加了工艺复杂性——即将推出的 GAA 技术可能不会提供可变数量的纳米片层。相同的表面形貌问题将适用于 GAA 工艺,该工艺将尝试从超晶格 Si 层构建 nFET,从超晶格 SiGe 层构建 pFET,

对于设计人员来说,与 FinFET 的量化特性相比,GAA 技术将在设备尺寸方面提供(一些)可变性。由于纳米片通道周围的 GAA 静电,泄漏电流将减少(稍后会详细介绍)。

模拟电路可能更容易优化,而不是严格依赖于鳍片数量的比率。SRAM 单元设计不再局限于 PD:PU:PG = 2:1:1 或 1:1:1 FinFET 尺寸限制。

目前,FinFET 标准单元库提供集成 1X、2X、4X 驱动强度选项的单元,通常具有 3 或 4 个器件 Vt 变体。

由于 GAA 技术具有更大的尺寸自由度(以及可能更少的设备 Vt 替代方案),库设计者可以从中选择一组不同的变量。看看单元库设计者如何利用这种设备灵活性将会很有趣。

Jin 描述了三个积极的工艺研发领域,以获得更优化的纳米片特性。

纳米片 Si 层中较低的空穴迁移率是一个问题。正在进行研究以增加 pFET 纳米片层中的 SiGe 成分(由于上述形貌困难,不采用 SiGe 超晶格堆叠)。一种方法是在超晶格蚀刻后“修整”pFET Si 纳米片的厚度,并在氧化物和栅极沉积之前沉积 SiGe“包覆”层。在修整和 SiGe 包层沉积步骤之后,难点在于保持均匀的纳米片厚度。

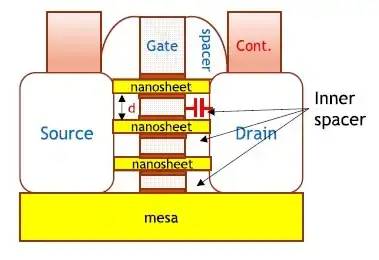

FinFET 在栅极和源极/漏极节点之间具有(相对)高的寄生电容,部分原因是鳍片之间栅极垂直侧壁到 S/D 节点的电容贡献。水平纳米片利用不同的栅极到 S/D 氧化物取向,由在 S/D 外延和 SiGe 蚀刻之前沉积在 SiGe 超晶格层中的内部间隔物产生。Jin 强调,不仅需要针对驱动电流优化纳米片和凹陷氧化物尺寸,还需要优化寄生 Cgs/Cgd 电容,如下图所示。

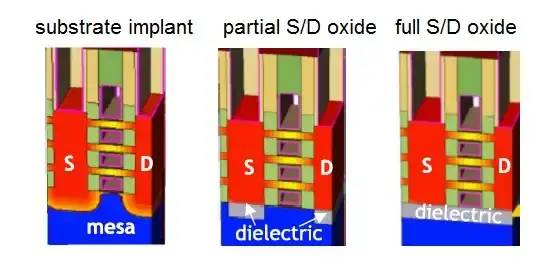

GAA 拓扑改进了(3 面)FinFET 静电,降低了亚阈值器件漏电流。然而,最底部(或“台面”)纳米片层存在寄生泄漏路径。在超晶格蚀刻、氧化物沉积和栅极沉积步骤之后,栅极到衬底的静电提供了(非 GAA)沟道电流路径。

如上所示,Jin 强调了通过以下任一方式减少这种漏电流贡献的研发工作:

-

-

-

衬底、S/D 节点和底层纳米片栅极之间的完全介电隔离

Jin 的演讲对 FinFET 和 GAA 器件的相关特性提供了深刻的见解,因为工艺节点发展到水平纳米片拓扑结构。设计人员将受益于减少的漏电流和设计尺寸的灵活性,尽管纳米片沟道电子和空穴迁移率之间的差异将需要重新考虑电路Belta比。正在进行的工艺研发工作正在寻求减少这种载流子迁移率差异,并优化寄生 Rs、Rd、Cgs 和 Cgd 元素。

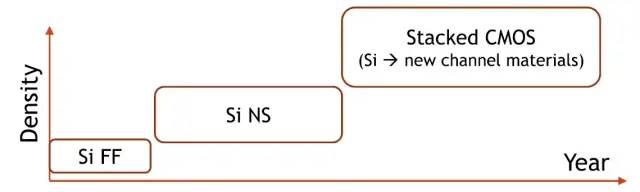

在新的器件配置(例如,3D 硅制造)和非硅材料(例如,2D 半导体)出现之前,Jin 提出了如下所示的粗略时间表,用于引入 GAA 纳米片技术。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2734内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|MLCC|英伟达|模拟芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!