来源:内容由半导体行业观察(ID:icbank)编译自「

semianalysis

」,谢谢。

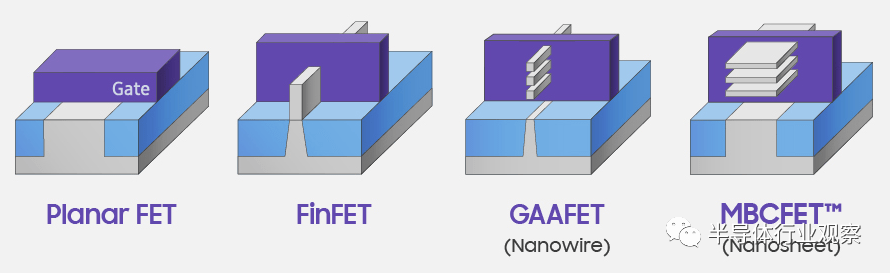

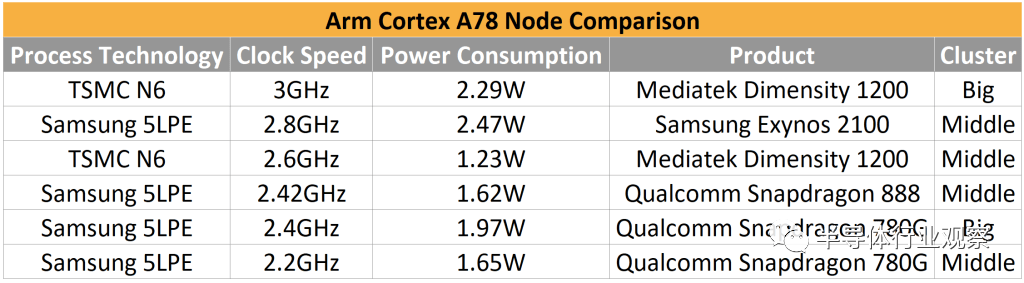

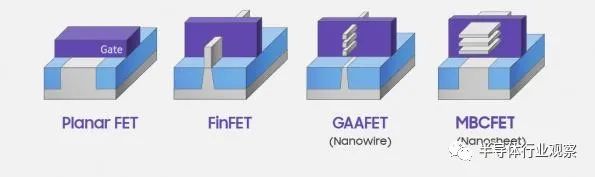

据外媒semianalysis报告,三星长期以来一直在大肆宣传他们的3nm工艺节点。他们称赞他是业界首次将Gate All Around FET用于商业工艺技术。率先改变晶体管架构是半导体界梦寐以求的奖项。英特尔是第一个采用22纳米三栅极技术的公司,该技术实现了从平面 FET 晶体管到 FinFET 的转变。三星希望在GAAFET上夺冠。尽管围绕这个节点进行了大量营销和炒作,但它看起来越来越严峻,因为对于商业代工合作伙伴来说,3nm节点现在看起来像是推迟到 2024年。

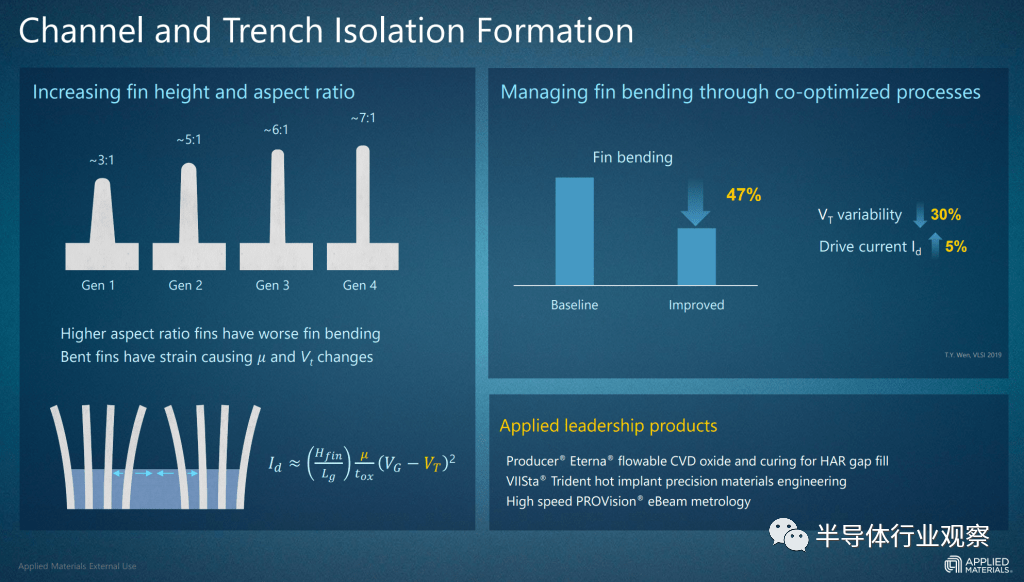

在最近几代 FinFET 中,功率缩放是通过所谓的鳍片减少来实现的。我们已经从四个鳍片器件到三个鳍片器件,再到每个晶体管有两个鳍片。此外,这些鳍变得更高,以增加沟道和栅极之间的接触面积。但现在这些缩放方法已经没有动力了,如果不使用 Co 触点和 SiGe 等特殊材料作为通道,它就已经接近尾声了。更高和更少的鳍也带来了其他问题,这需要在晶体管架构上向前迈进。

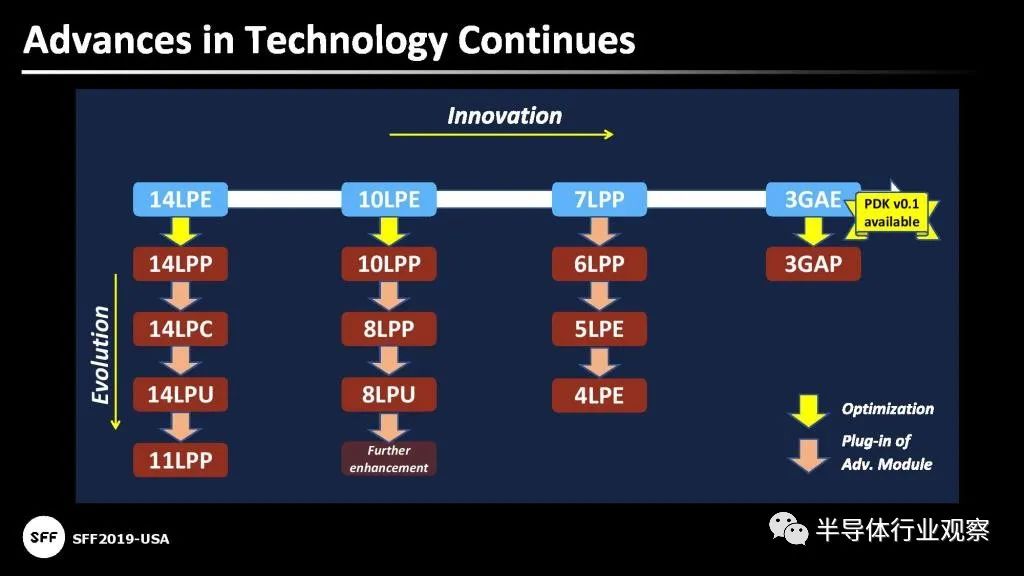

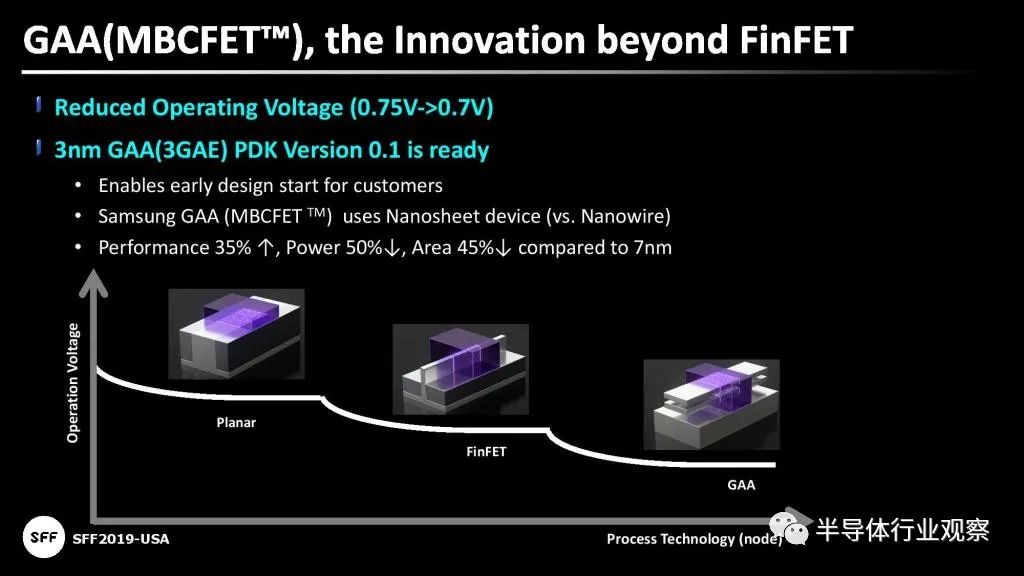

台积电在制程技术上的领先地位一直在快速增长。如果没有非常突破性的项目,三星就没有机会与台积电的无情执行相抗衡。2019 年初,他们宣布了 3GAE 工艺节点以及该技术的早期产品设计套件 (PDK)。他们的 3GAE 工艺技术将利用 MBCFET 架构。本质上,MBCFET 就像是将 FinFET 的鳍片从其侧面翻转,然后将水平鳍片堆叠在一起。沟道和栅极之间的接触面积显着增加,这使得功率和性能获得巨大收益。

与 7nm 技术相比,三星声称性能提升了 35%,功耗增加了 50%,面积增加了 45%。在 2019 年初的这次活动中,三星还声称他们的 3GAE 工艺将在 2020 年提供首批客户流片,并在 2020 年底进行风险生产,并在 2021 年底进行批量生产。

时间快进到 2021 年,三星的3nm GAA没有流片(编者注:貌似这个说法不正确,因为三星昨天已经发布了流片新闻),批量生产离交付还很远。与 7nm FinFET 相比,该工艺的目标似乎也进行了大量修改,性能从 35% 降到 10%。逻辑面积从 45% 减少到 25%,功耗从 50% 减少到 20%。

我们将给予三星毫无疑问的好处,并假设此比较是与他们最先进的 7nm 级节点 (5nm LPP) 版本进行比较。如果是这样,那么这与其说是隐形削弱,不如说是与最新和最先进的三星工艺技术的新比较。无论如何,这些增益甚至可能无法让三星在功耗和性能方面与台积电的 6nm 节点相提并论,更不用说当前 iPhone、iPad 和 Mac 中使用的 5nm 节点了。

三星通过在其路线图中插入新的工艺技术来应对 3GAE 节点的延迟。4LPP节点是7nm家族之外的新节点。这项技术将在高通和三星的各种移动和无线电产品中展示。其中高通的FSM200是最令人兴奋的产品。

当前的 5LPE 节点被 5LPP(以前的 4LPE)和 4LPP 接替,这意味着 3GAE 的进一步延迟。所有迹象都指向 2023 年初的 3GAE 节点,即使是最悲观的行业追随者也是如此。作为三星最大的客户,高通将率先将这些技术与三星内部开发的芯片一起使用。

Chidi Chidambaram 博士是领导公司的工艺技术和晶圆工程团队的工程副总裁,他会对铸造工艺路线图有直接和深入的了解。他最近在重要的半导体资本设备供应商应用材料公司的一次活动上发表了讲话。在这次活动中,他被问到了围绕晶体管技术的栅极产品化时间表。

“我想你知道,'24,'23 制作。最早的可能是 23 年,但我认为 24年的生产是合理的”Chidi Chidambaram 博士说。

Chidi Chidambaram 博士很可能属于流程路线图的保密协议,这将解释为什么他必须含糊其辞。他的团队将直接经历三星在 2019 年大声宣布的 3GAE 节点“2020 年首次客户流片”的失败。他们还评估了台积电和三星的 2022 年和 2023 年设计。他的团队将负责决定将哪种工艺技术用于这些设计。他似乎在押注 2023 年是可能的,但 2024 年是最合理的时间表。

这与三星过去推出工艺节点的方式一致。例如,随着 14 纳米、10 纳米,尤其是 7 纳米的发布,他们的旗舰 Exynos 产品线在任何代工产品上市前至少 6 个月就开始在节点上小批量生产。

考虑到这些意见,最好的情况是,在2023年看半年可能看到基于3nm的Exynos芯片的小批量生产。在最乐观的情况下,这意味着 3GAE 将在2024年成为代工工艺节点!

这将与台积电的 2nm 工艺节点相似,后者将在 2024 年采用全栅极晶体管架构。虽然三星专注于实现晶体管全栅极的先拔头筹,但台积电专注于多种缩放途径,例如钴在触点和互连中的使用、锗掺杂通道、用于 EUV 的内部薄膜以及使用 EUV 进行多重图案化。一直以来,看起来他们将在同一时间范围内将一个更密集的门商业化,围绕工艺节点。

三星和英特尔在领先技术方面继续落后于台积电。他们能赶上吗?

在与处于工艺技术前沿的台积电竞争过程中,三星代工厂终于流片了使用其环栅 (GAA) 晶体管架构的 3nm 芯片。

这需要一套不同于台积电和英特尔使用的 FinFET 晶体管结构的设计和认证工具,因此三星使用了 Synopsys 的 Fusion Design Platform。该工艺的物理设计套件 (PDK) 于 2019 年 5 月发布,并于去年通过了该工艺的认证。

流片是由Synopsys 和三星代工厂合作完成的,旨在加速为 GAA 流程提供高度优化的参考方法。

参考设计流程包括一个集成的、支持golden-signoff的 RTL 到 GDSII 设计流程以及golden-signoff产品。该流程针对的是希望将 3nm GAA 工艺用于高性能计算 (HPC)、5G、移动和高级人工智能 (AI) 应用中的芯片的客户。

三星代工设计技术团队副总裁 Sangyun Kim 表示:“三星代工是推动下一阶段行业创新的核心,我们不断进行基于工艺技术的发展,以满足专业和广泛市场应用不断增长的需求。在三星电子。我们最新的、先进的 3nm GAA 工艺受益于我们与 Synopsys 的广泛合作,Fusion Design Platform 加速准备以有效实现 3nm 工艺的承诺,证明了这些关键联盟的重要性和好处.”

三星表示,GAA 架构改进了静电特性,从而提高了性能并降低了功耗,并带来了基于纳米片宽度控制的额外矢量的新优化机会的额外好处。与完善的电压阈值调谐一起使用,这提供了更多方法来优化功率、性能或面积 (PPA) 的设计。

设计流程还包括对复杂布局方法和布局规划规则、新布线规则和增加的可变性的支持。该流程基于单个数据模型并使用通用优化架构,而不是组合点工具。

Synopsys 数字设计部总经理 Shankar Krishnamoorthy 表示:“GAA 晶体管结构标志着工艺技术进步的一个关键转折点,这对于保持下一波超大规模创新所需的缩放轨迹至关重要。” “我们与三星代工厂的战略合作支持共同交付一流的技术和解决方案,确保这些扩展趋势的延续以及这些为更广泛的半导体行业提供的相关机会。”

Synopsys 技术文件可从三星代工厂获得,用于 3nm GAA 技术工艺。

Fusion 设计平台包括用于数字设计的 Fusion Compiler、IC Compiler II 布局布线和 Design Compiler RTL 综合、PrimeTime 时序签核、StarRC 提取签核、IC Validator 物理签核和 SiliconSmart 库表征。

延伸阅读:三星将在 3nm 引入GA,台积电在2nm?

据报道,3nm 工艺有两种变体——3GAAE 和 3GAAP——代表早期和加号,这是两款基于纳米片结构的设计,在鳍中具有多个横向带状线。这种纳米片设计已被研究机构 IMEC 作为 FinFET 的后续产品进行了大量讨论,并由 IBM 与三星和 Globalfoundries 合作进行了研究。

“将 GAA 结构应用于我们的下一代工艺节点将使我们能够率先打开一个新的智能互联世界,同时也加强我们的技术领先地位,”三星执行副总裁兼代工销售和营销主管 Charlie Bae 说。

所谓Gate-all-around (GAA) ,有时候被称作横向纳米线场效应管。这是一个周边环绕着 gate 的 FinFet 。按照专家的观点, GAA 晶体管能够提供比 FinFet 更好的静电特性,可满足某些栅极宽度的需求,这主要体现在同等尺寸结构下,GAA沟道控制能力增强,因此给尺寸进一步微缩提供了可能;传统Finfet的沟道仅三面被栅极包围,而GAA以纳米线沟道设计为例,沟道的整个外轮廓都被栅极完全包裹住,这就意味着栅极对沟道的控制性能就更好。

三星研究人员将将他们采用全环栅(GAA)晶体管设计的3nm CMOS技术叫做多桥通道(MBC)架构。据介绍,这个由纳米片(nanosheets)的水平层制成的沟道完全被栅极结构包围。

三星声称,这种技术具有高度可制造性。因为它利用了该公司现有的约90%的FinFET制造技术,而只需要少量修改过的光掩模。他们用它构建了一个功能齐全的高密度SRAM宏。他们表示,该工艺具有出色的栅极可控性(65 mV / dec亚阈值摆幅(subthreshold swing)),这比公司的FinFET技术高31%,且因为纳米片通道宽度可通过直接图案化来改变,这就给设计提供了灵活性。

对台积电而言,Gate-all-around FETs(GAAFET)仍是台积电发展路线图的一部分。预计该公司在其“后N3”技术(可能是N2)中使用新型晶体管。实际上,该公司处于下一代材料和晶体管结构的探路模式,这些材料和晶体管结构将在未来的许多年中使用。

该公司在最近的年度报告中说:“对于先进的CMOS逻辑,台积电的3nm和2nm CMOS节点正在顺利进行中。” “此外,台积电加强了探索性的研发工作,重点放在2nm以外的节点以及3D晶体管,新存储器和low-R interconnect等领域,这些领域有望为许多技术平台奠定坚实的基础。

值得注意的是,台积电正在扩大Fab 12的研发运营能力,目前正在研究和开发N3,N2和更高级的节点。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2722内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|MLCC|英伟达|模拟芯片

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!