来源:内容由半导体行业观察(ID:icbank)编译自「

nextplatform」,

谢谢。

很明显,混合内核——用 ARM 的话来说是 big.Little——也将成为主流 x86 CPU 的一个特性。Intel 的 Lakefield 结合了一个 Ice Lake“大核”和四个 Tremont“小”核。其即将推出的 Alder Lake 平台 将扩展该解决方案,(传闻)多达八个低功耗内核(Gracemont)和八个高性能内核(Golden Cove)。

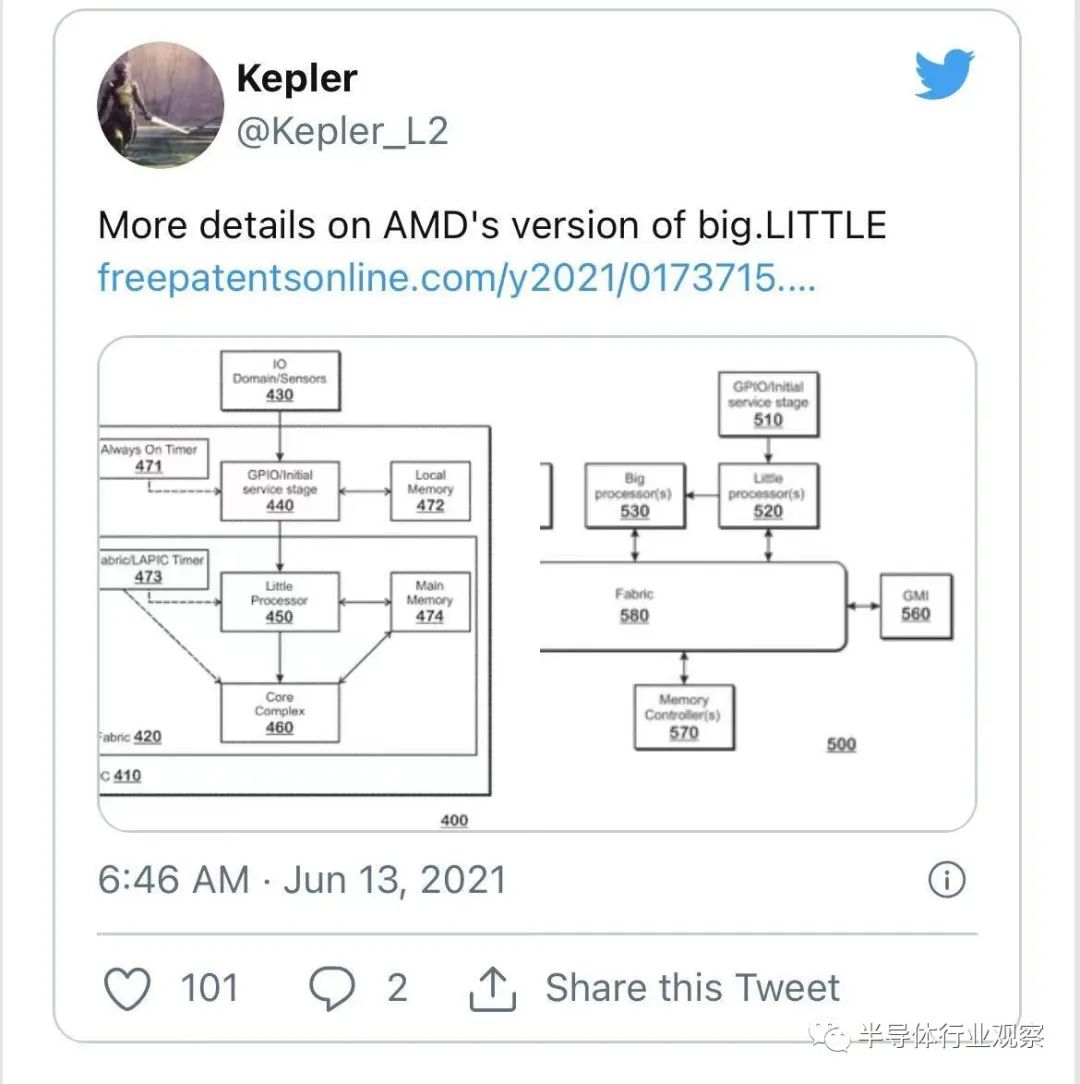

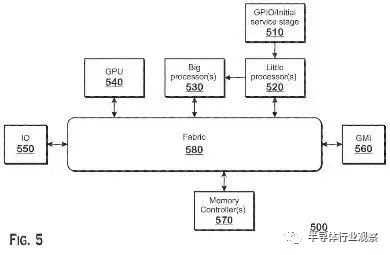

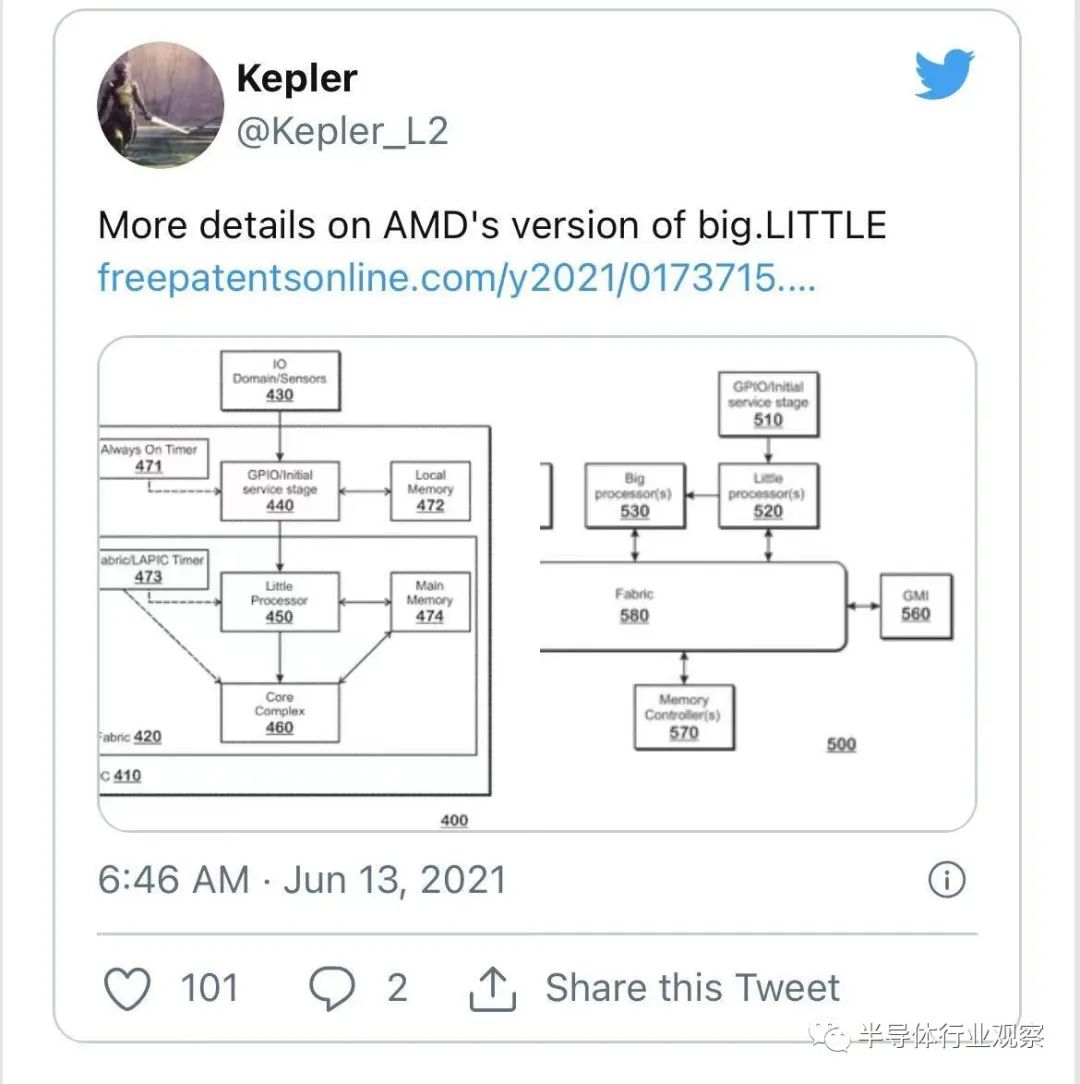

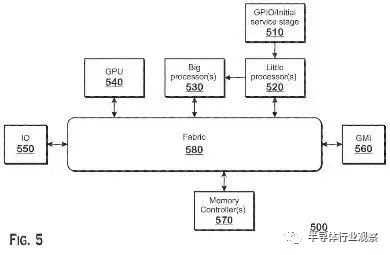

一些迹象表明 ,AMD 有自己的计划进入这个赛道,他们的一项新的专利申请支持了这个想法。据报道,AMD 申请了一项专利,描述了一种 CPU 将工作转移到另一种 CPU 的方法:

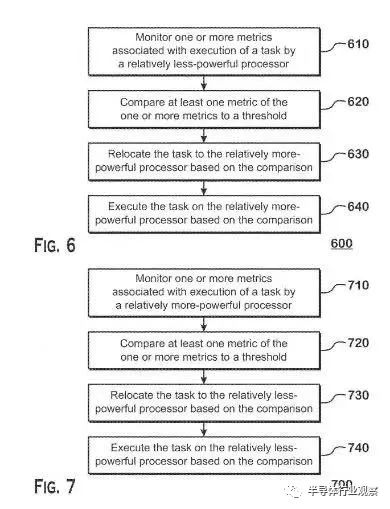

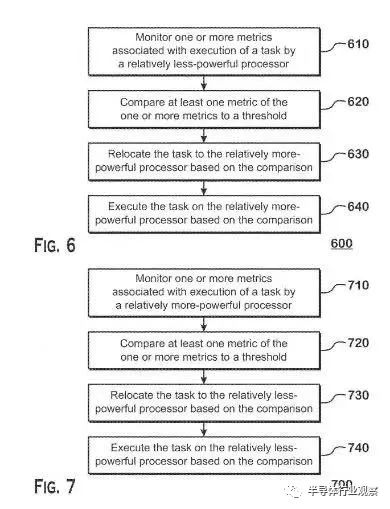

根据该专利,CPU 将依靠核心利用率指标来确定何时适合将工作负载从一种类型的 CPU 转移到另一种类型。建议的指标包括 CPU 以最大速度工作的时间量、CPU 使用最大内存的时间量、一段时间内的平均利用率以及工作负载从一个 CPU 转移的更一般类别另一个基于与任务执行相关的未指定指标。

当 CPU 确定工作负载应从 CPU A 转移到 CPU B 时,当前执行工作的内核(在本例中为 CPU A)将进入空闲或停止状态。CPU A 的架构状态保存到内存并由 CPU B 加载,然后继续该过程。AMD 的专利将这些转移描述为双向——小内核可以将工作转移到大内核,反之亦然。

十年前,我问过英特尔的智能手机 SoC 设计人员,他们为什么要依靠 DVFS(动态电压和频率调节)来保持 Atom 的功耗竞争力而不是大一点。根据英特尔的架构师的说法,当考虑到硅芯片空间要求和整体节能时,DVFS 可以与 big.Little 提供的产品相媲美。

这在当时可能是正确的——Medfield 通常与它打算与之竞争的中端 Cortex-A9 设备竞争——但今天似乎并非如此。当时,Medfield 是建立在 32nm 工艺节点上,而 Cortex-A9 一般建立在 40nm 或 28nm 上。即使我们保守计算,台积电和英特尔也经历过多次全节点微缩。英特尔的 10nm 技术被认为等同于台积电的 7nm 节点。使用混合 x86 内核设计的芯片尺寸损失比以前小得多。

我们认为big.Little 赢得这场战斗的另一个原因是硅设计的不断变化的性质。以高时钟运行 10 纳米 CPU 所需的调整也可能导致 CPU 内核在低时钟下无法像低功耗的专用 CPU 内核那样节省功耗。

AMD 所关心的一个大问题是,该公司是否会从全新的 CPU 内核中构建一个新的内核,或者它是否会回到像 Jaguar 这样的设计并将其用作未来产品的基础。虽然 CPU 需要刷新或更新,但它在新的时候是一个坚固、平衡的设计。AMD、Intel 或 Apple 等公司通常需要 3-5 年时间从头开始构建新内核,因此 AMD 走哪条路可能取决于它何时开始该项目。我们知道它早在 2019 年就申请了这项专利,因此该公司显然已经在这个想法上工作了一段时间。

我们预计 2021 年不会看到 AMD 的混合内核,但 2022-2023 年出现,也不会不合理。既然我们知道 Apple M1 提供的一些省电得益于其操作系统调度,我们希望英特尔和 AMD 都与微软合作,以采用类似的技术。混合内核在满载/时钟下不会对 x86 CPU 功耗产生太大影响,但它们可以显着降低功耗。

当 Joe Macri 在 2020 年末告诉人们 AMD 没有近期推出混合内核的计划时,他表示一个主要的障碍是 Windows 中缺乏调度程序支持。我们现在知道Windows 11即将推出,Alder Lake 正在准备发布。没有人正式表示这种混合调度程序将在 Windows 11 中出现,但它几乎肯定会出现。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2708内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|美国|华为|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!