DDR5有望在2023年超越DDR4

2021-06-15

14:00:51

来源: 半导体行业观察

来源:内容来自半导体行业观察综合

,谢谢。

一份最新报告指出,从 DDR4 到 DDR5 内存的过渡应该是迅速的。

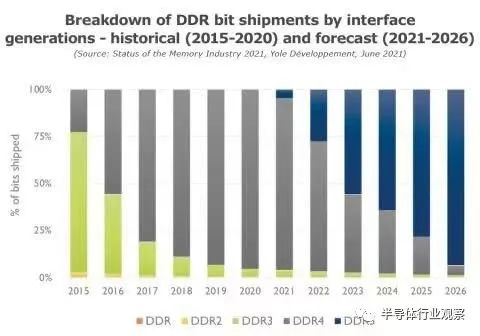

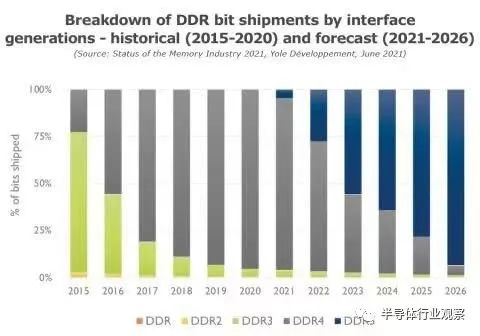

根据行业专家Yole Developpement的一份报告,DDR5 的广泛采用应该会在 2022 年开始,从服务器市场和企业界开始。然后在 2023 年,我们将最终看到主流市场广泛采用 DDR5,手机、笔记本电脑和 PC 将充分利用该技术。事实上,我们应该会在 2023 年看到DDR5 出货量超过 DDR4,这标志着两种技术之间的快速过渡。

更具体地说,据估计,2022 年 DDR5 的采用率将增加 25%(感谢服务器市场),然后在 2023 年实现更大的跃升,达到超过 50% 的市场份额。最后,到 2024 年至 2026 年,我们应该预计其他市场将效仿 DDR5 的采用,使 DDR4 仅占市场的 5%。

巨大的需求应该会加速向 DDR5 的迁移,需求已经显着回升(尽管 2019 年存在供过于求的问题)。事实上,该公司预测DRAM市场价值 1200亿美元,NAND 市场价值 680亿美元,创历史新高。这种趋势应该会持续到 2026 年,届时内存市场的价值应该会超过 2000 亿美元。

DDR5是对当前 DDR4 内存架构的重大升级。DDR5 的带宽将是 DDR4 的两倍,以及芯片密度的四倍。这将允许显着更高容量的 DIMM,同时以较低的工作电压运行。DDR5 还具有内置 ECC 支持以提高可靠性,但这是一种芯片级技术,不符合保护传输中数据的成熟 ECC 内存技术的要求。因此,我们也将看到 DDR5 内存的标准和 ECC 风格。

作DDR4 的后继者,DDR5 是下一代同步动态随机存取存储器 (SDRAM)。DDR 存储器可在单个时钟周期内发送和接收两次数据信号,并允许更快的传输速率和更高的容量。

虽然 DDR 内存中的大多数开发都是适度的增量,重点是性能改进以满足服务器和个人计算机应用程序要求,但从 DDR4 到 DDR5 的跨越是一个更大的飞跃。在需要更多带宽的驱动下,DDR5 在强大的封装中带来了全新的架构。

计算能力的迅速发展使中央处理器制造商努力提供尽可能多的核心数量。不久前,个人计算机用户只能期待 4 核芯片。现在,大多数中央处理器制造商会提供 6 核中端芯片和 12 核高端芯片。对于服务器解决方案,制造商们提供多达 64 内核。当前服务器内存解决方案(如 DDR4)不能满足这些高核计数中央处理器的带宽需求。

信号完整性、电源传输和布局复杂性限制了每个内核的内存带宽进度。要释放下一代中央处理器的强大功能,需要新的内存架构,以符合其更高的每核带宽要求。这是开发 DDR5 SDRAM 解决方案的主要驱动力。

为满足下一代中央处理器的需求,DDR5 带来了更高的数据速率、更低的能耗和更高的密度。DDR5 发布后的最大数据速率为 4800MT/s(百万次/秒),而 DDR4 为 3200MT/s。系统级仿真中的并行比较显示,DDR5 的有效带宽约为 DDR4 的 1.87 倍。

DDR5 将突发长度增加到 BL16,约为 DDR4 的两倍,提高了命令/地址和数据总线效率。相同的读取或写入事务现在提供数据总线上两倍的数据,同时限制同一存储库内输入输出/阵列计时约束的风险。此外,DDR5 使存储组数量翻倍,这是通过在任意给定时间打开更多页面来提高整体系统效率的关键因素。所有这些因素都意味着更快、更高效的内存以满足下一代计算的需求。但是,DDR5 不仅提高了性能,还提高了可扩展性。

经过优化的 DRAM 核心计时和芯片内纠错码是提高 DDR5 可扩展性的两个主要因素。虽然内存架构逐年扩展,但它的代价是 DRAM 单元电容的下降和位线接触电阻的增加。DDR5 解决了这些缺点,并允许通过优化的核心计时进行更可靠的扩展,这对于确保有足够的时间在 DRAM 单元中写入、存储和检测电荷至关重要。

芯片内纠错码 (ECC) 通过输出数据之前在读取命令期间执行更正,提高了数据完整性并减少了系统纠错负担。DDR5 还引入了错误检查清理,其中 DRAM 将在发生错误时读取内部数据并写回已更正的数据。

为了提高记忆体的存取效能,DDR8采用由8个Bank Group组成的32 Bank(可以单独启用/停用的存储单元)架构,比DDR4由4个Bank Group组成的16 Bank架构,多出1倍的存取可用性(Access Availability)。而DDR5的Burst Length(DRAM单个读/写指令可以存取的资料量)从DDR4的8增加到16,也是增加效能的关键功能。

不同于DDR4在更新(Refresh)时无法执行其他操作,DDR5则透过Same Bank Refresh功能,让系统可以在更新某些Bank的时候,存取其他Bank的资料,另一方面DDR5也透过决策回馈等化器(Decision Feedback Equalization,DFE)消除杂讯,以增加整体效能表现。

在电力消耗部分,DDR5的工作电压为1.1V,低于DDR4的1.2V,能降低单位频宽的功耗达20%以上。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2707内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|美国|华为|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie