来源:内容由半导体行业观察(ID:icbank)编译自「

pc.watch

」,

作者:笠原 一辉

,谢谢。

AMD的CEO一一Lisa Su在5月31日召开的“COMPUTEX TAIPEI Virtual”上做了基础演讲,同时介绍了AMD的最新产品、技术。本文,笔者就AMD发布的“3D Chiplet Technology”展开叙述。

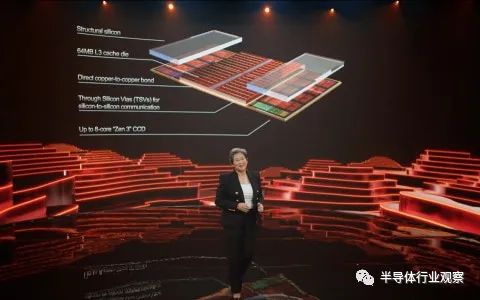

AMD的CEO一一Lisa Su公布了采用了3D Chiplet Technology的“Ryzen 5000 Series 3D Chiplet Prototype”。(图片出自:pc.watch)

“3D Chiplet Technology”是通过应用于客户端PC的“Ryzen”或者应用于服务器方向的“EPYC”导入2D芯片混搭技术的3D 版本的“Chiplet Technology”。以往是在Package的横方向搭载数个芯片,而3D Chiplet Technology采用的是一种被称为CDD的技术,即在CPU芯片上纵向搭载SRAM的“芯片堆叠(Die Stacking)”技术。

英特尔也于2018年12月发布了被称为“Foveros”的3D 堆叠技术,已于2020年作为“Intel Core processors with Intel Hybrid Technology”(研发代码:Lakefield)而投产。

由上可知,封装技术(即将芯片封装在基板上)是继处理器架构、制造技术之后的第三个竞争核心。

英特尔最大40核、AMD为64核,秘密在于Chiplet

第三代Xeon SP (Xeon Platinum 8830,40核)、第三代EPYC(EPYC 7763,64核,右侧)、EC站点服务器的基准数据。Lisa Su称,第三代EPYC的性能提高了50%。(图片出自:pc.watch)

在此次的COMPUTEX TAIPEI Virtual上的基础演讲中,,AMD的CEO一一Lisa Su对AMD三月份发布的第三代EPYC处理器(以下简称为第三代:EPYC,研发代码:Milan)和英特尔四月份发布的第三代Xeon Scalable Processors(以下简称为:第三代Xeon SP,研发代码:Ice Lake)进行了比较。

前者为64核的EPYC 7633,后者为40核的Xeon Platinum8380。Lisa Su表示,如果是用于EC(电子商务)的服务器的话,EPYC7763的性能要高出50%。

服务器的工作负荷(Workload)极其复杂,也并不是由一个应用发挥其他多个应用的性能,因此,此处暂时不做叙述。

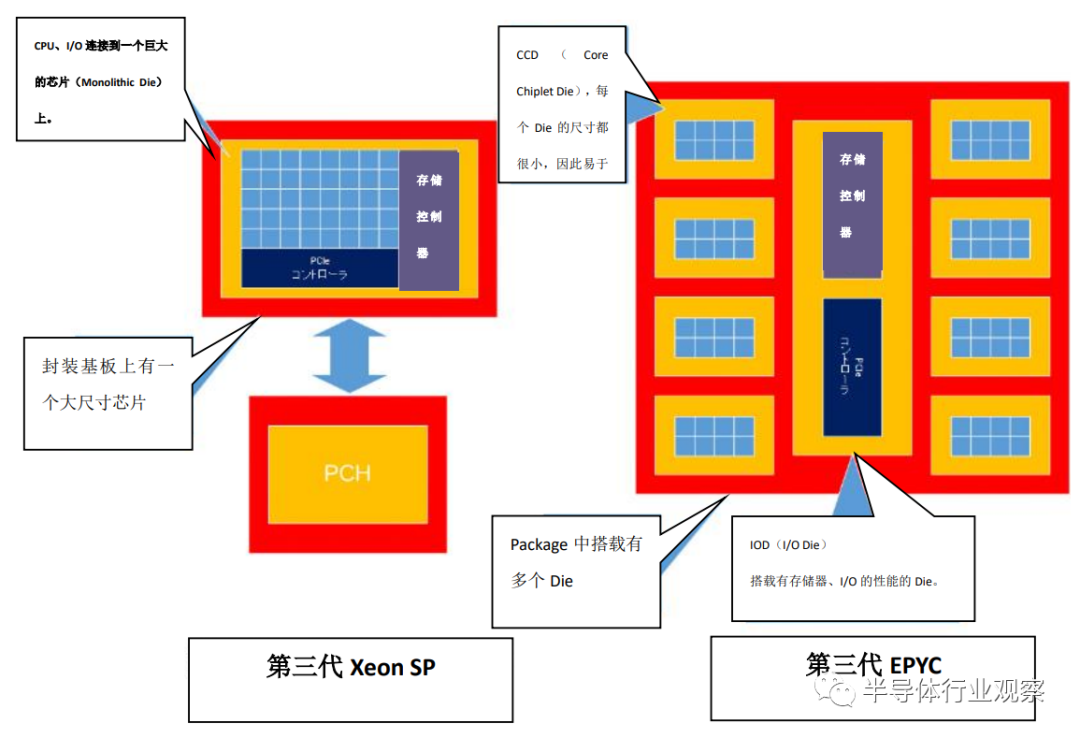

AMD的处理器在性能上远远超过英特尔的最大理由是,CPU核数多于英特尔。当我们比较一个封装基板的时候,AMD的最高核数为64,英特尔为40。

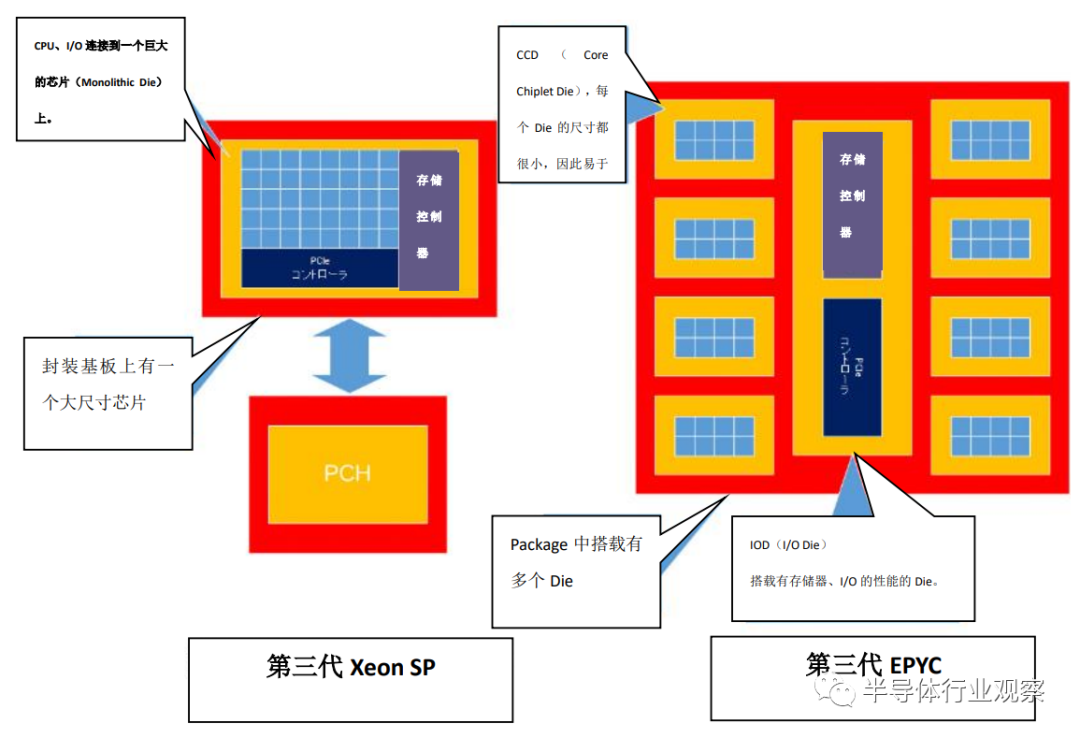

英特尔的第三代Xeon SP与第三代的EPYC的差异。

(图片出自:pc.watch)

那么,为什么AMD的CPU核数多呢?其答案在于“封装技术”。

就英特尔的第三代Xeon XP而言,在被称为“传统的单一芯片(Traditional Monolithic Die )”的Package中有一个芯片(Die)。而40个CPU核被封装在一个芯片(Die)里,不仅很难生产单个的芯片,而且很难提高良率(可采用的芯片数量占总生产数量的比例)。

与此相对,AMD的EPYC采用的是被称为“Chiplet Technology”的封装技术。Chiplet上混搭有被称为CCD(Core Chiplet Die)的CPU核的芯片和IOD(I/O Die)。

CCD上的一个芯片由8核的CPU构成,与用于客户端PC的Ryzen等一样,如果是台式PC的话,由1个CCD1和IOD组成的八核产品可更改为由2个CCD和IOD组成的16核产品。如果是服务器的话,组成结构为8个CCD、1个IOD(为最大限度),即可组成的产品为:8核x8=64核。

结果就在Lisa Su讲的产品性能比较表中,用于台式PC的Ryzen的核数之所以超过英特尔的用于台式PC的核处理器,也是一样的道理,可以说,近几年来AMD获得飞跃式进步的最大的理由也在于Chiplet的应用。

将Chiplet以3D方向扩张的“3D Chiplet Technology”,在一个CCD上搭载64MB的SRAM

3D Chiplet Technology的构造。

(图片出自:pc.watch)

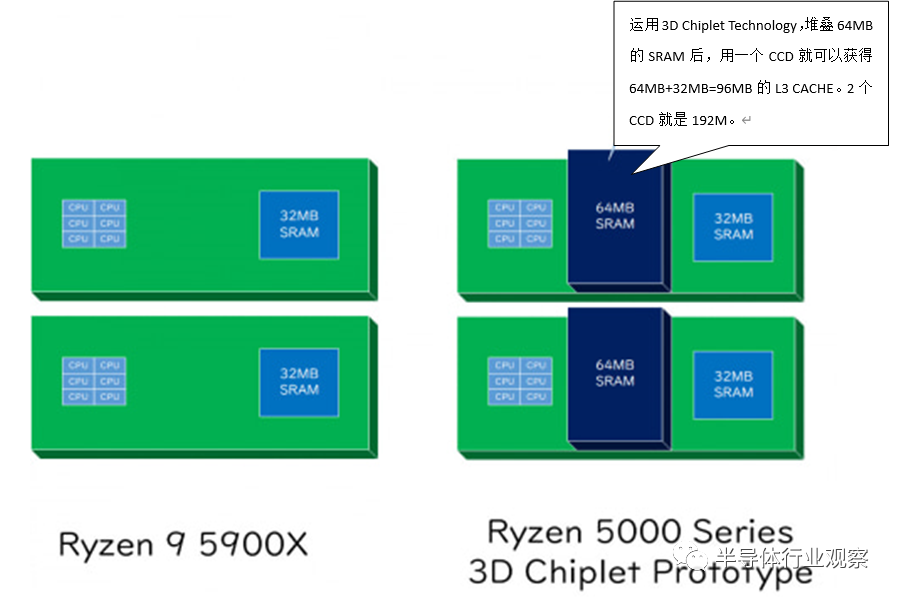

如果说AMD的Chiplet是在Package内部横向展开的话,那么,在COMPUTEX TAIPEI上发布的“3D Chiplet Technology”就是在Package的纵向堆叠芯片。

AMD此次发布的产品如下,在CCD的芯片上,堆叠由7纳米工艺制造的SRAM,将64MB的SRAM芯片堆叠在Zen 3基的CPU核上,SRAM的左右两边用硅填充。

芯片和芯片之间采用TSV(Through Silicon Via)技术,穿透CPU芯片上的孔后,与CPU的中介层(Interposer)直接连接。因此,不需要在中间插入基板,可直接将芯片连接,且CPU和SRAM之间可以进行高速通信。

Lisa Su表示,SRAM 是作为L3 CACHE来工作的(此外,On-die的SRAM也可继续作为L3 CACHE来使用)。当然,On-die的SRAM可以高速工作、且可以减少内存延迟(Memory Latency),但是像这次的Off-die的话,内存延迟会增加。但是,由于容量增加了,也可以提高性能。

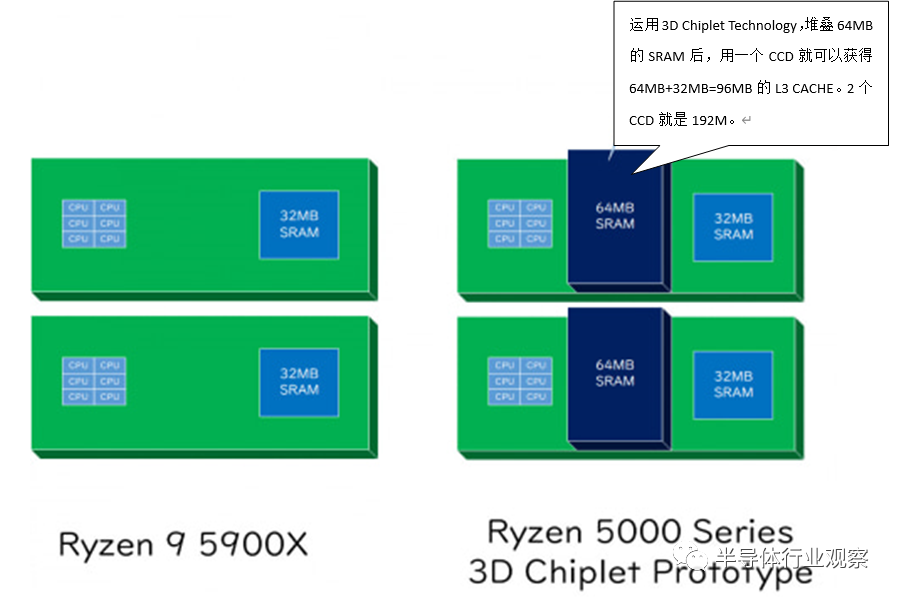

Ryzen 9 5900X和Ryzen 5000 Series 3D Chiplet Prototype的区别,此图为笔者制作。(图片出自:pc.watch)

此次Lisa Su展示的样品有以下,Ryze 9 5900 X以及采用了被称为“Ryzen 5000 Series 3D Chiplet Prototype”的3D Chiplet Technology的产品。

Ryzen 9 5900X内置了两个CCD(CPU的核数为12,1个CCD 有六个核,所以6核X2个CCD),搭载64MB的L3 CACHE。5900X中,8核的CCD有两个,每个CCD的L3 CACHE为32MB。

即,整个封装为192MB,搭载有现有产品(64MB)三倍的L3 CACHE。

Ryzen 9 5900X和Ryzen 5000 系列3D Chiplet Technology的性能比较、平均可以提高15%的性能。(图片出自:pc.watch)

从Lisa Su公开的资料来看,比较了Ryzen 9 5900 X(12 核、L3 CACHE 、64MB)和Ryzen 5000 系列3D Chiplet Technology(12核,192MB)在游戏时的帧速率, 发现后者高出前者12%。放入其他游戏中比较后发现,性能高出约15%。

L3 CACHE的容量增加即意味着内存延迟(CPU读取到存储器数据的延迟)的减少,出现这样的效果的原因在Lisa Su的演讲中。

Lisa Su明确表示,3D压层的SRAM 会在今年(2021年)年末发布。由于名称不是“Ryzen 6000 系列”,而是“Ryzen 5000 系列3D Chiplet Technology”,因此,会作为Ryzen 5000系列的追加SKU投入。

此外,Lisa Su还表示,5纳米的“Zen 4”世代的产品在明年(2022年)投入。由于TSMC的5纳米工艺已经用于生产苹果的M1,因此生产技术已经十分成熟。

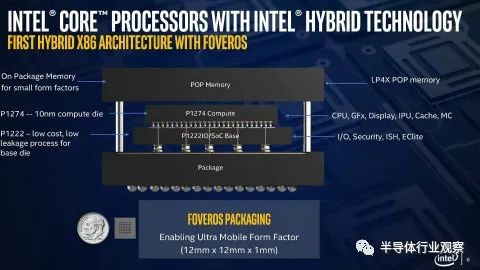

英特尔计划在未来的产品中使用3D 堆叠技术一一“Foveros”

英特尔去年(2020年)发布的“Intel processors with Intel Hybrid Technology(研发代码:Lakefield)”的结构。基底(Substrate)上有I/O芯片、CPU/GPU芯片、DRAM,三层结构。(图片出自:pc.watch)

但是,这种单层构造并不是AMD的专利,英特尔也在将同样的技术应用于产品。在2018年的Intel Architecture Day上,公布的“Foveros”即为3D压层技术。

后来,Foveros作为2020年投产的“Intel Core processors with Intel Hybrid Technology(研发代码:Lakefield)”的芯片压层技术,而被应用。就Lakefield的芯片压层而言,将由10纳米工艺生产的CPU/GPU芯片、22纳米工艺生产的PCH按照3D方向封装,虽然与AMD(以SRAM为压层对象)的应用不同,但是基本思想是一致的。

★ 点击文末

【阅读原文】

,可查看本文原文链接!

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2703内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|美国|华为|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!