[原创] AMD的3D Chiplet处理器:先进封装的胜利

2021-06-07

14:00:11

来源: 半导体行业观察

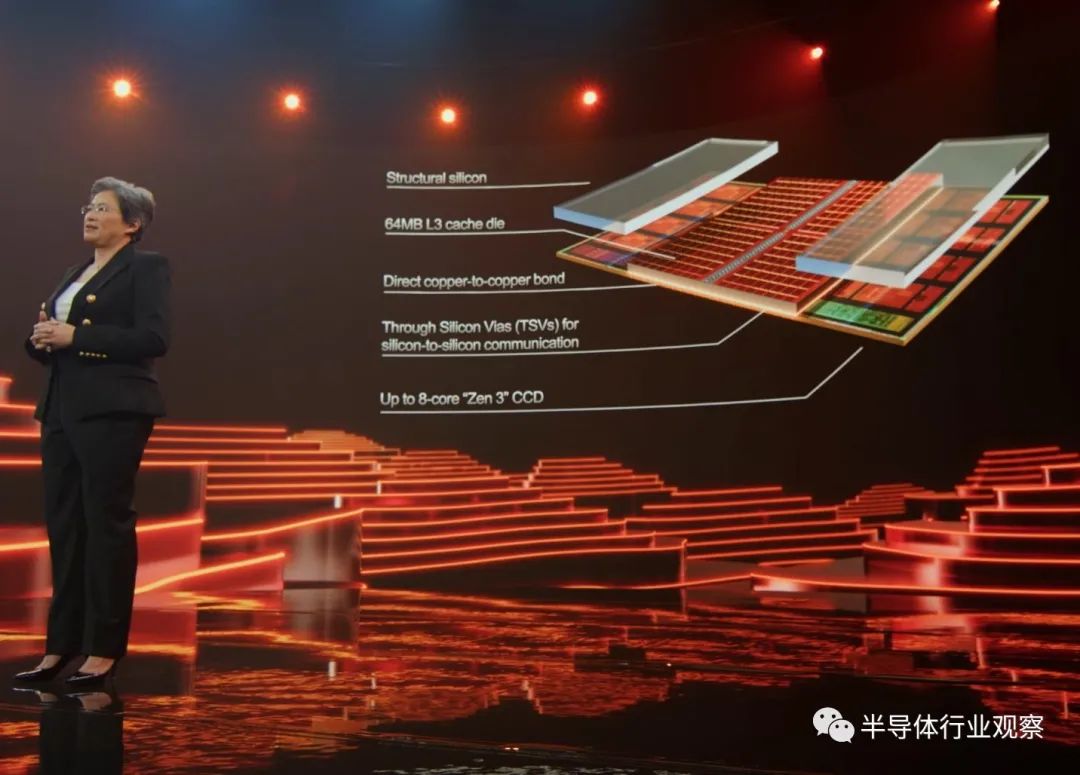

在上周举办的Computex上,AMD发布了其实验性的产品,即基于3D Chiplet技术的3D V-Cache。该技术使用台积电的3D Fabric先进封装技术,成功地将包含有64MB L3 Cache的chiplet以3D堆叠的形式与处理器封装在了一起。

在AMD展示的概念芯片中,处理器芯片是Ryzen 5000,其原本的处理器Chiplet中就带有32 MB L3 Cache,而在和64 MB的3D V-Cache做3D封装后,每个Ryzen 5000 Chiplet可以访问总共96 MB的L3 Cache。而在每个包含多个Ryzen 5000 Chiplet的处理器中,则最多可以访问高达192MB的L3 Cache。

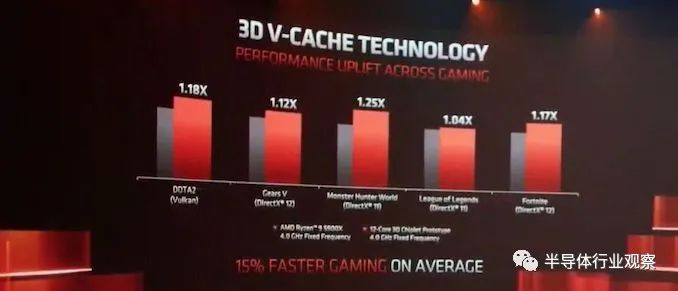

随着半导体工艺节点越来越接近物理极限,每一代半导体工艺节点提升对于芯片性能带来的收益也越来越小,通常在15%左右。而在AMD发布的带有3D V-Cache的处理器则在工艺不变(仍然使用7nm台积电工艺)的情况下,在3D游戏等对于处理器性能有高需求的应用场景中实现了约15%的性能提升。这一点说明先进封装在今天已经能实现原来需要半导体工艺节点前进整整一代才能实现的性能提升;而在未来随着半导体工艺越来越接近极限,每一代工艺带来的性能增益越来越小,先进封装可望取代半导体工艺成为芯片性能提升的主要推动力。

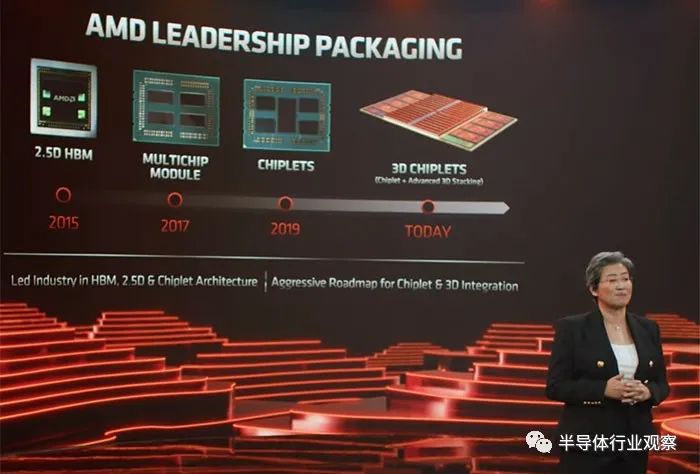

而在先进封装领域,AMD已经有了多年的积累,从2015年开始使用HBM技术,到2019年推出使用chiplet的产品,到今天推出3D chiplet,每一步都可以看见AMD对于先进封装领域投入的决心。

在先进封装领域,有两条由应用驱动的技术路径。一条的主要诉求是提升互联密度,从而解决芯片之间的通信带宽,其代表产品就是基于2.5D/3D高级封装的HBM DRAM接口标准,使用HBM可以将DRAM和处理器(CPU,GPU以及其他ASIC)之间的通信带宽大大提升,从而缓解这些处理器的内存墙问题。目前,HBM已经成为高端GPU的标配,同时也应用于不少针对云端处理的AI芯片(例如谷歌的TPU)中。

除此之外,另一条技术路径是chiplet,即在封装系统里面不再使用少量的大芯片做集成,而是改用数量更多但是尺寸更小的芯片粒(chiplet)作为基本单位。使用chiplet的第一个优点是提升了良率,如果使用大芯片的话,如果在芯片的晶圆面积上出现瑕疵,那么整个芯片就有了瑕疵,无法作为良品使用;但是如果把同样面积的芯片拆分为多个chiplet,那么出现瑕疵的话就仅仅是瑕疵出现的那个chiplet无法使用,而其他chiplet则不受影响,这样就提升了良率,而这对于良率存在挑战的先进半导体工艺至关重要。Chiplet另外的潜力在于可以实现更灵活的异构集成,在同一封装系统中不同的chiplet可以使用不同的半导体工艺实现,从而进一步降低成本(例如某些对于逻辑性能需求不高的模组可以使用成熟工艺)并提升性能。

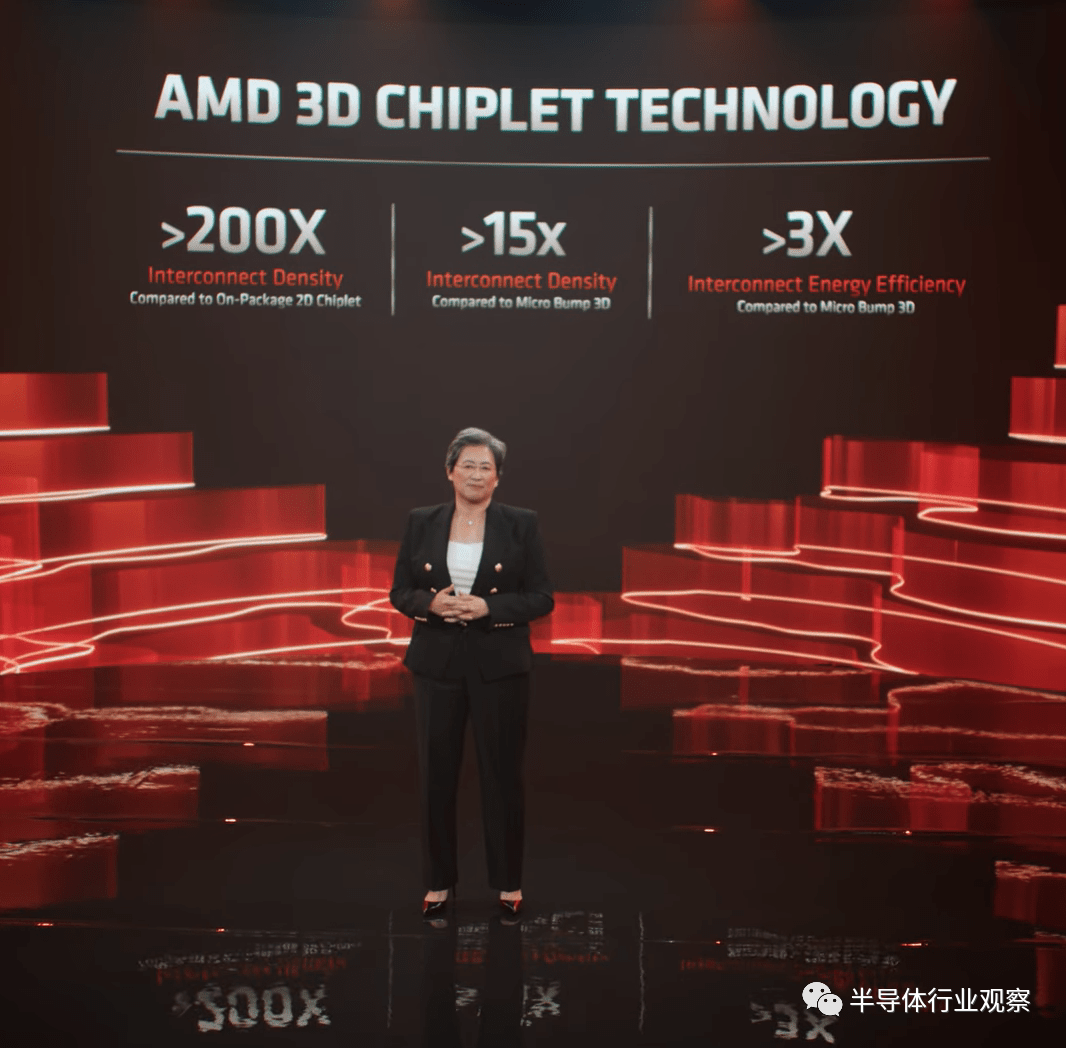

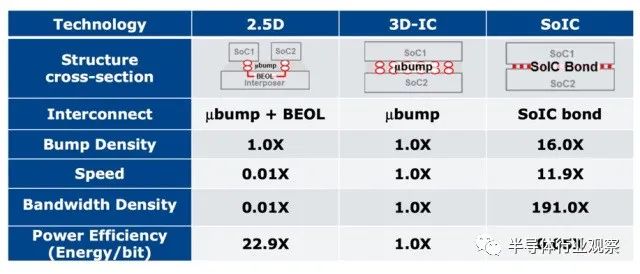

而这次AMD的3D Chiplet则是把两条先进封装的技术路线汇合到了一起。AMD发布的3D V-Cache中,首先处理器和堆叠的L3 Cache都使用了chiplet,另外在3D V-Cache和处理器chiplet之间,也使用了先进封装带来的高密度互联,其互联密度较2D chiplet高两百多倍,相比传统的3DIC技术也能提高15倍。我们认为,AMD将3D Chiplet投入商用对于先进封装领域来说,将是类似HBM进入GPU这样的里程碑式事件。

在AMD发布的3D chiplet背后,是台积电的先进半导体工艺技术和先进封装技术。台积电作为同时掌握了最先进半导体工艺和封装技术的代工厂,其全球最顶尖代工厂的地位得到了巩固,同时其在先进技术领域也将变得更加强势。

早在2019年的VLSI Symposium中,台积电就发表了类似这次AMD 3D Chiplet的技术。台积电把这个技术System on Integrated Chips(SOIC),其主要解决的就是进一步提升3D封装中的互联密度。传统3DIC技术的连线密度受到bump尺寸的限制,从而限制了集成总线的带宽和互联成本。而台积电SoIC技术一个关键优势就是无须bump,只要将两块要堆叠的芯片的铜互联做部分裸露并对准,之后即可通过热处理工艺完成两块芯片的电路连接。这样一来,两块堆叠芯片之间的走线密度以及信号传输功耗都可以大大改善。在今年的ISSCC中,台积电又一次展示了SOIC技术,这次台积电为该技术商用起了一个正式的名字(3DFabric),并且公布了更多互联密度相关的数据,其互联密度相比传统的基于bump的3DIC技术可以提升16倍,该数据与AMD这次在Computex发布的相关数字(相比3DIC互联密度提升15倍)也大体相符。

如前所述,随着摩尔定律的半导体工艺节点提升接近极限,先进封装技术将会慢慢接班半导体工艺节点而成为芯片性能提升的推动力。台积电在拥有最先进半导体工艺的同时,也在先进封装领域领跑全球,其在半导体代工领域的领导者地位将延续下去。于此同时,在AMD首发基于3DFabric的产品之后,预计在未来会有更多芯片设计公司跟进使用3DFabric来实现高性能芯片,从而进一步推广下一代先进封装技术的应用。

我们认为,类似3D Chiplet的技术在AI时代将会有广泛应用。

目前,人工智能已经成为推动半导体行业市场收入的重要引擎。基于神经网络的人工智能需要强大的算力支撑其模型训练和部署,因此高性能计算芯片在AI时代至关重要,这也是全球范围内出现了不少AI芯片初创公司的原因。对于AI计算来说,内存访问已经越来越成为性能的瓶颈,因此如何提升处理器(AI芯片)与存储器之间的内存访问速度和效率变得越来越重要。为了解决这个问题,目前云端AI芯片使用HBM DRAM配合大容量的片上SRAM已经成为标配(例如谷歌的TPU)。HBM DRAM和大容量SRAM缺一不可,其中HBM DRAM容量大,但是存取需要较大的延迟,因此常用来存储系统调度算法中在未来可能会用到的数据;而SRAM的带宽大于HBM,延时也较小,但是容量也远小于DRAM,常用来存取在当前立即需要用到的数据。在人工智能领域,随着GPT-3这样的巨型模型越来越多,对于DRAM和SRAM容量的需求都越来越大,而SRAM扩容目前看来最有希望的方法之一就是使用类似3D Chiplet的技术,使用3D堆叠的方式来获得更大的容量(如这次AMD在使用3D V-Cache后SRAM容量就扩大到了三倍),因此我们认为随着台积电的3DFabric技术进一步成熟,AI芯片很可能是下一个使用该技术的产品,并且随着人工智能市场越来越大,AI芯片也将进一步将3D Chiplet带向主流,同时使用HBM加3D Chiplet技术的芯片产品将会进入更多产品中获得使用。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2699内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|美国|华为|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie