[原创] 八英寸晶圆厂的“问题”

保守来讲,当下8英寸(200mm)晶圆的供应链情况相当严峻!

然而,这绝不是新问题。中国台湾的市场调查公司一一TrendForce于2020年11月发布新闻称:“就8英寸晶圆的产能而言,自2019年下半年以来一直持续在严重的供给不足问题”。

此外,雪上加霜的是2021年3月瑞萨电子那珂工厂发生了火灾。由于瑞萨的此处工厂为诸多车型供货,因此导致问题更加恶化。

基于以上背景,导致诸多因素“纠缠”在一起。但是,不言而喻,最大的原因还是在于新冠疫情(COVID-19)。由于新冠疫情的发生,耳机、电脑、电视、显示屏、手机等各种电子产品的需求猛增。

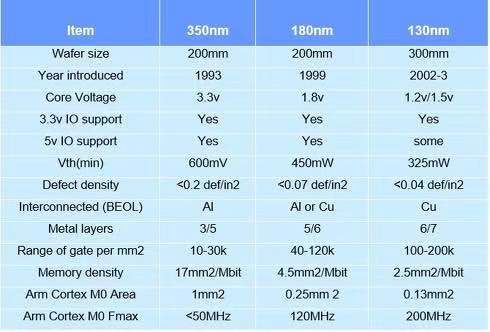

虽然汽车也属于以上范畴,但人们还是希望汽车市场会在2021年内从新冠疫情的阴影中恢复。如今各种产品都在推广将多种功能汇集于一体的SoC(System on Chip)模式,因此很多产品都需要搭载多个具备数模混合信号(Mixed Signal Chip)的IC。以上产品的用途方向主要有以下:PMIC(Power Management IC)、CMOS图像传感器、指纹识别传感器、汽车发动机/底盘控制、显示屏驱动IC、Sub Giga Hertz的无线通信芯片等。一般情况下,以上这些都适用180纳米、350纳米工艺,用8英寸晶圆生产。

即,用于这种数模混合信号芯片(Mixed Signal Chip)、功率半导体的产品需求不断增长,这导致了8英寸晶圆的产能不足。

受到8英寸晶圆的供给达到极限的影响,代工厂(Foundry)很有可能会扩大产能。代工厂可能会收购垂直统筹型厂家(IDM:Integrated Device Manufacturer)的8英寸晶圆生产设备和产线。可列举的事例如下:最近有报道指出,中国台湾的UMC正在讨论收购Japan Semiconductor(原东芝的半导体制造公司) 的8英寸产线。

用于Mixed Signal ASIC等产品的主要节点技术比较图。(图片出自:eetimes)

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2691内容,欢迎关注。

推荐阅读

★ 韩国半导体的反击

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备 |汽车芯片|存储|美国|华为|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 共筑国产汽车芯片未来,中国汽车芯片联盟全体大会即将开启

- 2 国产EDA突破,关键一步

- 3 摩尔斯微电子推出突破性物联网连接平台 新型 MM6108-EKH05 评估套件助力开发人员创建下一代物联网解决方案

- 4 芯片老化测试插座,这家公司享誉盛名