AMD全面拥抱Chiplet技术

2021-05-26

14:00:45

来源: 半导体行业观察

来源:内容来自

半导体行业观察综合

,谢谢。

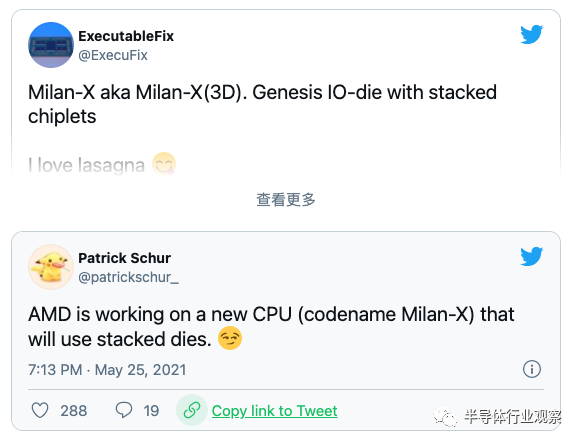

在之前的报道中,我们已经报道了AMD在产品中对chiplet的关注。而根据硬件爱好者ExecutableFix和Patrick Schur的新推文,我们对AMD即将面世的3D芯片堆叠技术有了更多了解。因为这些推文声称,我们可以首先期望在EPYC Milan-X系列数据中心处理器中看到这项技术。

一年前,AMD在其2020年金融分析师日活动中透露,公司正在研究一种将利用其X3D芯片封装技术的新型处理器。AMD的X3D混合技术基于2.5D封装和3D堆叠。用通俗易懂的话说,它允许AMD在芯片制造商的多芯片模块(MCM)内彼此堆叠各种管芯。考虑到相似性,X3D基本上是AMD对Intel Foveros 3D堆栈技术的回应。

最新的谣言称,Milan-X将是采用X3D芯片封装的第一批芯片。给定代号后,可以合理地假设Milan-X由Zen 3内核组成,就像EPYC 7003(米兰)部件一样。ExecutableFix声称Milan-X基于Genesis IO-die,暗示Zen 3 EPYC芯片中具有相同的I / O裸片。

但是,我们不希望AMD突破Milan-X的核心壁垒。该公司在演讲中解释说,X3D的目标是提供高达10倍的更高带宽。但是,该公司从未透露过计划进行的堆叠。ExecutableFix认为AMD正在堆叠小芯片(chiplet),但考虑到它们所需的散热能力,似乎不太可能使用复杂的核心芯片(CCD)。

因此,AMD很可能在Milan-X上堆叠内存,而不是在计算芯片上堆叠内存。此外,在AMD的2020年金融分析师日上共享的图表显示2x2布局,其中四个互连小芯片和四个堆叠裸片在一个较大的中介层上方。这四个小芯片可能是计算芯片,我们怀疑AMD在Milan-X上堆叠了HBM封装。显然,每个小芯片都有一个堆叠的芯片。HBM内存的存在会在EPYC处理器上产生奇迹,尤其是在对带宽敏感的工作负载繁重的数据中心环境中。

即使在AMD的路线图上,X3D处理器也被标记为“未来”。直到今天我们还没有听到有关Milan-X的任何消息。但是,AMD总裁兼首席执行官苏丽莎博士计划在Computex 2021上发表名为“ AMD加速–高性能计算生态系统”的主题演讲,因此我们可能很快会听到有关Milan-X的更多信息。

Chiplet走向GPU? AMD 正式提交专利申请

随着半导体的制程发展越来越精细,芯片规模的限制亦越来越大。传统的单个大芯片策略已经行不通,而Chiplet 小芯片将成为新的的发展方向,AMD 的Ryzen、Threadripper、EPYC 三大产品线皆在这个方向发展,且取得了不俗的成果。

而最新消息指AMD 要将这个策略延续到GPU 上了。在2020 年的最后一天,AMD 向美国专利商标局提交了一项新专利,描述了未来的GPU 小芯片设计。

AMD 首先指出传统的多GPU 设计存在不少问题(包括自家的CrossFire 技术),包括某些GPU 编程模型不适合多路GPU、很难在多GPU 间并行分配负载、多GPU间快取内容同步亦极为复杂等等。AMD 目前是利用high bandwidth passive crosslink 来解决这些难题,将第一个GPU 小芯片与CPU 直接耦合在一起(communicably coupled),而其他GPU 小芯片均通过被动交联与第一个GPU 小芯片重组,而所有的GPU 小芯片都放置在同一个中介层(interposer) 上。

这样整个GPU 阵列就被认为单一SoC,然后划分成不同功能的子芯片。而传统的GPU 设计中,每个GPU 都有自己的末级快取,不过为避免同步难题,AMD 也重新设计了快取体系,每个GPU 依然有自己的末级快取,但是这些快取与物理资源替换在一起,因此所有快取在所有GPU 间依然是统一、一致的。

听上去好像很高深? 毕竟一般在专利文件中,厂商经常故意隐藏具体的设计细节,甚至可能故意放一些难以理解、甚至误导的描述。AMD 并无透露是否正在进行实际的GPU 小芯片设计,但早前已有传闻指其全新的RDNA3 架构将采用多芯片,而这份专利正提供了更多佐证。

由此可以预料到RDNA3 架构若果真的用上小芯片设计,核心规模必然会急剧膨胀,一、两万个流处理器数目也是小意思。

小芯片技术(Chiplet)被视为延缓半导体摩尔定律的解方。当摩尔定律趋向3纳米、1纳米的物理极限之际,chiplet成为后摩尔定律时代的新机会,小芯片技术可能带给从上游IC设计、EDA Tools、制造、先进封测等各个产业链环节颠覆式的改变。目前,已有很多公司创建了自己的chiplet生态系统,包括Marvell的MoChi、英特尔的EMIB以及新创公司zGlue提供的产品。

所谓Chiplet小芯片技术将一个芯片组成的处理器划分为多个芯片,例如分别是:数据存储、计算、信号处理、数据流管理等功能,然后再将它们连接在一起形成一个「小芯片」的芯片网络。也就是说,未来的电脑系统结构,可能只包含一个CPU芯片和几个GPU,而这些GPU都连接到这些Chiplet芯片上,形成芯片网络。换言之,未来计算机的系统结构,可能不是由单独封装的芯片制造的,而是由IC制造在一块较大的矽片上并产生互连而成芯片网络。

从ISSCC 2020研讨会议上,可以发现许多半导体研究集中在小芯片技术上,该技术可以克服微处理的许多限制,包括芯片架构设计和封装技术将在未来获得新发展。尤其,AMD建构自己的chiplet生态系统,生产了Ryzen和Epyc x86处理器。AMD自2019年以来投入Zen2 CPU内核和小技术生产。Zen2技术首次引入7nm制程制造,这项创新使性能比以前制程提高了15%,与原始电路的10轨单元库相比,Zen2使用了6轨单元库,这是很大变化在减少逻辑半导体设计中的单元库轨道数量,是最大难度的成就。

AMD从2019年起全面采用小芯片技术而获得了技术优势,也就是Zen2体系结构中采用的小芯片技术称为Core Complex Die(CCD),使用7nm制程制造与CPU内核相对应的CCD,并以14nm制造外围管芯。Chiplet这种方法降低了制造芯片所支援的零组件生产成本,而不仅仅针对7nm支援的零组件。AMD通过将管芯与一种称为Infinity Fabric On-Package(IFOP)的技术连接来解决管芯到管芯连接的性能损失。

AMD的Zen2架构处理器,在原来MCM(Multi-Chip Module)多芯片模组设计再进一步,改用chiplets小芯片设计。简单来说就是将CPU核心与I/O核心分离,分别使用不同的制程技术,CPU使用的是台积电7纳米制程技术,I/O是格芯14 / 12纳米。

根据AMD在ISSCC公布成本分析,对比7纳米Zen2在不同核心配置下的成本状况。在桌上型处理器的部分,如果将16核心32执行序的Ryzen 3代做为100%标准,那么采用原生核心的16核心处理器的成本将超过2,也就是至少是两倍的成本。而如果是EPYC伺服器处理器,则核心数越多,成本优势就越明显。其中以64核心的7纳米制程Ryzen为标准,则48核心的成本就是0.9,而原生48核设计的成本至少是1.9,也就是同样几乎为两倍的成本。

小芯片技术的主要用于逻辑芯片制程转移放缓下来,降低每一次制程缩减所需要的成本和开发时间。它仅在最新制程中引入必要的零组件,而在旧式制程制造时对不必要的零件则藉由小芯片技术进行连接,从而实现高效能。由此可见,展望未来,在架构设计、后端和封装流程的重要性,将比前端流程的开发更为重要。

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2687内容,欢迎关注。

『

半导体第一垂直媒体

』

实时 专业 原创 深度

识别二维码

,回复下方关键词,阅读更多

晶圆|集成电路|设备

|汽车芯片|存储|美国|华为|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复

搜索

,还能轻松找到其他你感兴趣的文章!

责任编辑:Sophie