英特尔EMIB封装深度解读

来源: 本文内容编译自semiwiki,谢谢。

-

晶圆级扇出重新分布,使用模塑料的重构晶圆基板作为裸片之间互连的表面(2D)

-

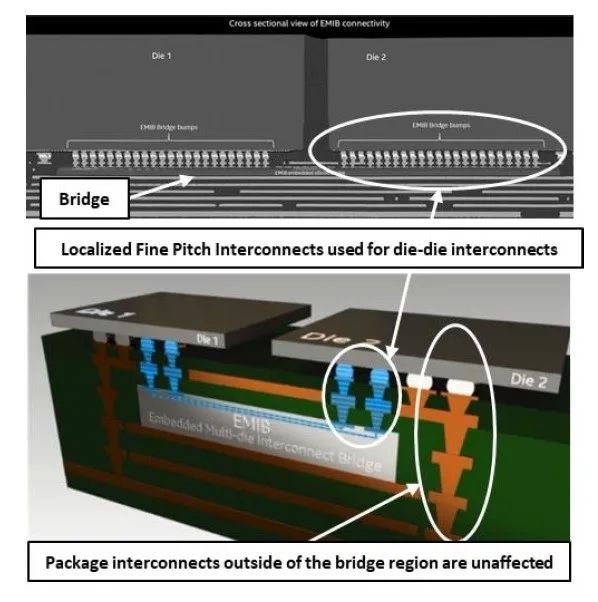

用于重新分配的单独的基于硅的互连层,可以是嵌入有机封装(2.5D)中的全尺寸硅中介层或die到die的硅桥

-

垂直堆叠的面对面或背对背芯片,利用芯片焊盘的混合键合和直通孔(3D)

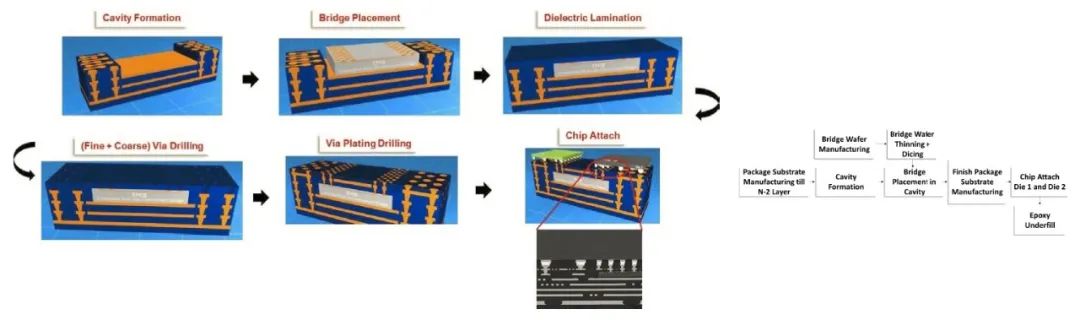

EMIB的制造

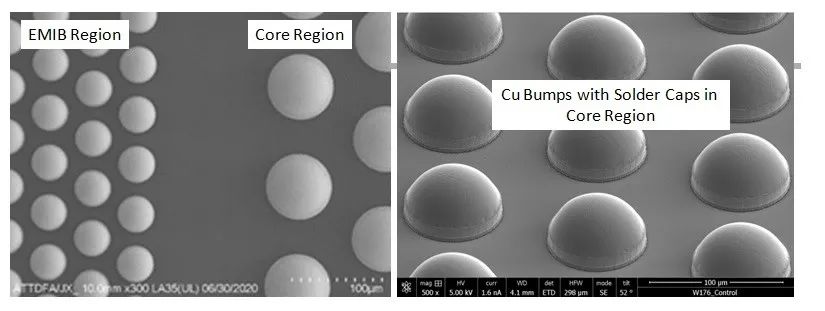

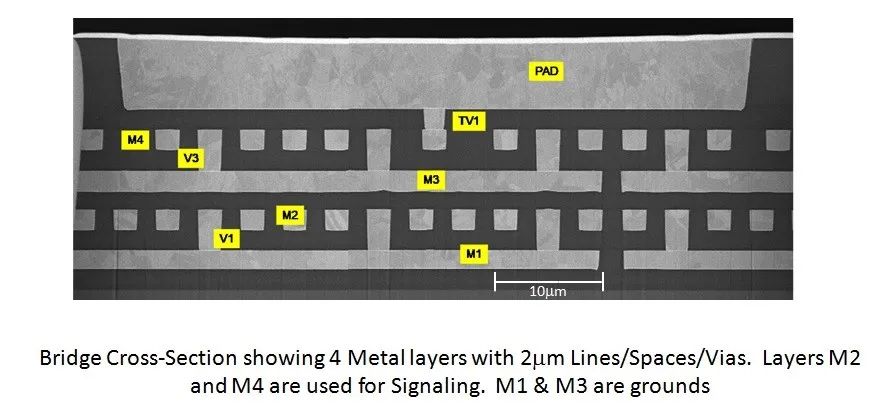

EMIB物理实施

-

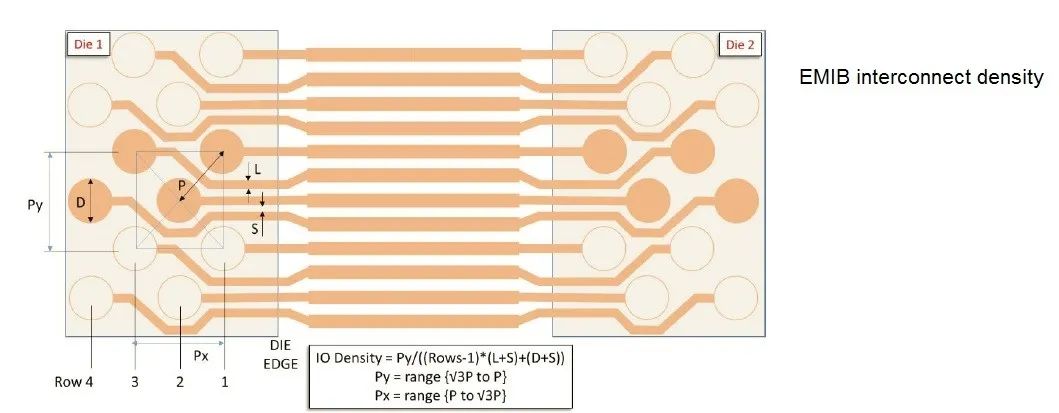

到裸片的凸点间距为55um

-

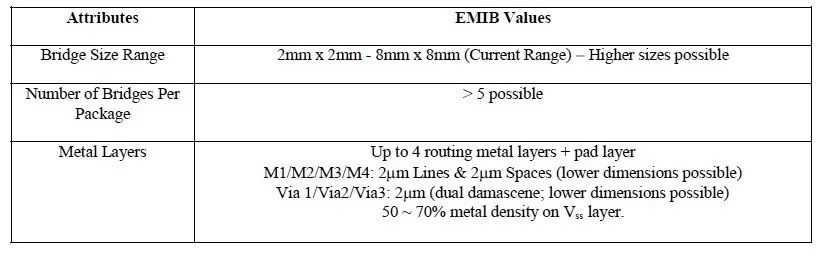

2um线+ 2um间距,金属厚度为2um

-

4um间距,每毫米“ beachfront”具有250根导线

-

每个EMIB金属层之间的电介质厚度为2um

-

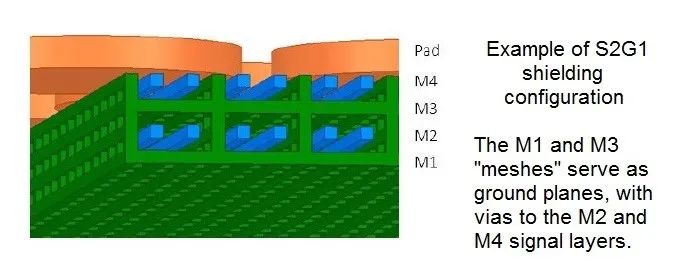

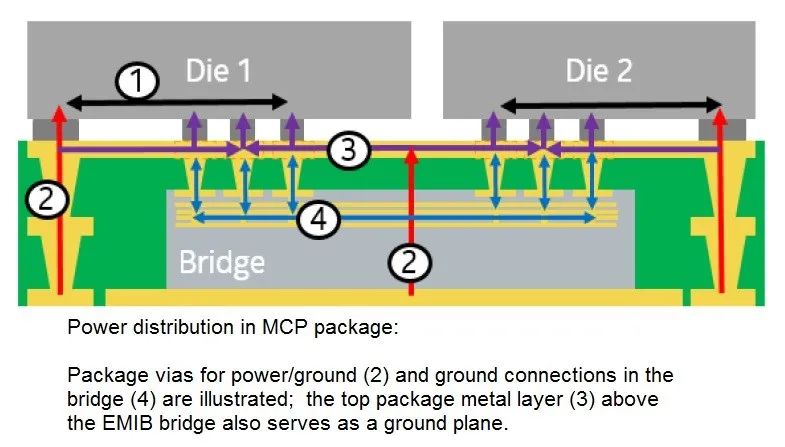

EMIB桥上的4个金属层M1和M3专用于GND平面

-

通常在M2和M4上利用3信号+ 1接地屏蔽图案的信号层

EMIB电气特性

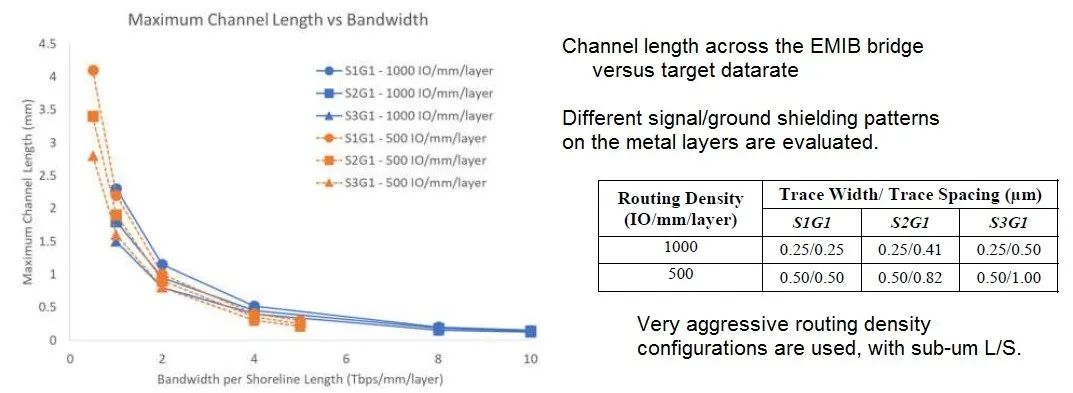

英特尔针对EMIB互连发布了详细的电气分析,评估了各种信号接地屏蔽组合和导线长度的插入损耗和串扰。

-

一个简单的输出驱动器(R = 50ohms,C = 0.5pF)

-

无端接的接收器(C = 0.5pF)

-

四层EMIB金属叠层,介电常数= 4.0

-

嵌入式桥上方的顶部封装金属平面

-

1V信号摆幅,具有200mV垂直睁开的接收器灵敏度(为无端接的电容式接收器合并了近端和远端串扰)

EMIB设计服务

EMIB未来发展

总结

•现有有机包装技术的扩展

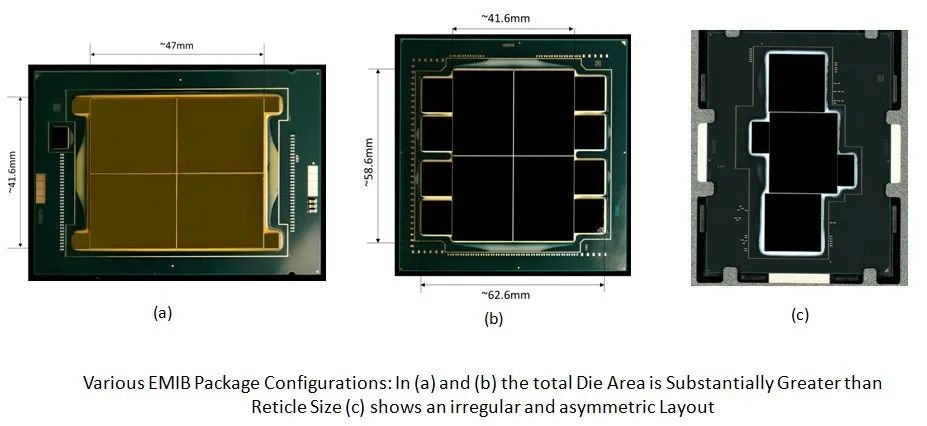

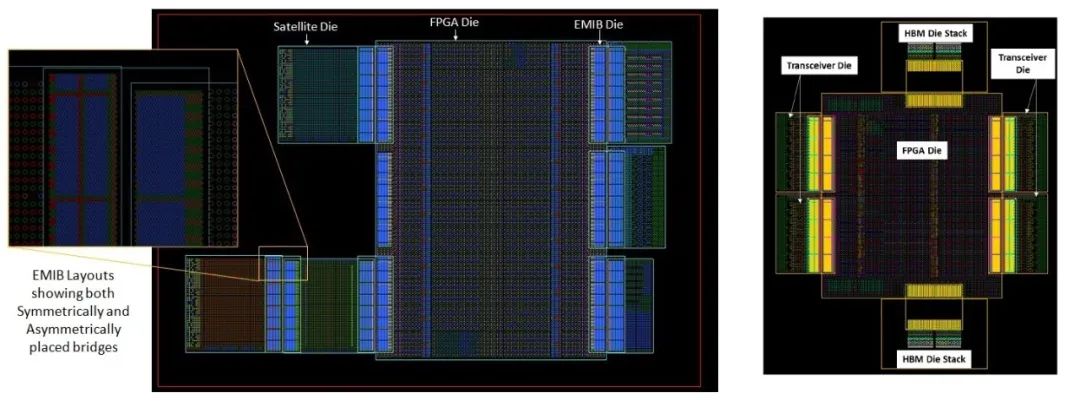

•支持大芯片数和大封装配置

•比全尺寸硅中介层的成本更低

•使用简单的驱动器/接收器电路,支持相邻芯片之间的高数据速率信令

•通过为该链接定制桥来分别优化每个冲模-骰子链接的能力

•芯片凸块和封装组装过程中的额外复杂性

•封装,die和EMIB桥之间的热膨胀系数(CTE)系数不同

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2666内容,欢迎关注。

推荐阅读

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|集成电路|设备|封测 |射频|存储|美国|台积电

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 国产EDA突破,关键一步

- 2 思尔芯第八代原型验证S8-100全系已获客户部署,双倍容量加速创新

- 3 在这个平台上,硬件创新跑出了“中国速度”

- 4 Ampere 年度展望:2025年重塑IT格局的四大关键趋势