FinFET的继任者:详解GAA晶体管

来源:内容来自「 知乎 」,作者:浅醉闲眠,谢谢。

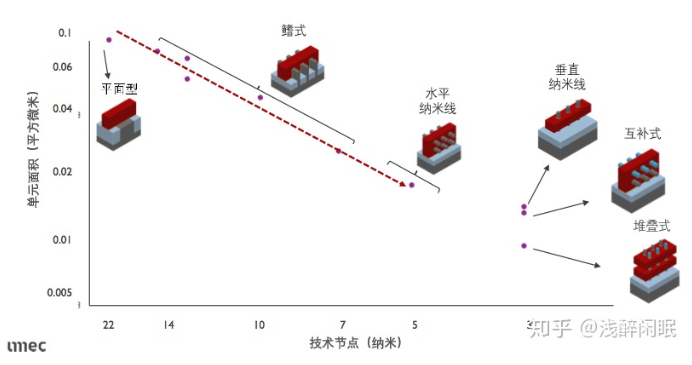

半导体技术发展史的本质就是晶体管尺寸的缩小史。从上世纪七十年代的10微米节点开始,遵循着摩尔定律一步一步走到了今天的5纳米。在这一过程中,每当摩尔定律遭遇困境,总会有新的技术及时出现并引领着摩尔定律继续前行。自22纳米节点上被英特尔首次采用,鳍式场效应晶体管(FinFET)在过去的十年里成了成为了半导体器件的主流结构。然而到了5纳米节点之后,鳍式结构已经很难满足晶体管所需的静电控制。其漏电现象在尺寸进一步缩小的情况下急剧恶化。因此,半导体行业急切需要一个新的解决方案在未来节点中替代鳍式晶体管结构。

尽管各种新型晶体管方案不断地被提出,然而工业界真正青睐的是能够允许他们继续使用现有设备以及技术成果的方案。正是基于这一原因,全环绕栅极晶体管(Gate-All-Around FET)被广泛认为是鳍式结构的下一代接任者。在2019年的三星晶圆制造论坛(Samsung Foundry Forum)上,三星明确表示将会在3纳米节点放弃鳍式结构,转向全环绕栅极技术。在刚刚过去的台积电第26届技术研讨会上,台积电也正式宣布将在2纳米节点引入全环绕栅极技术。目前英特尔仍然受困于7纳米技术难产,尚未给出具体的计划何时引入全环绕栅极技术。但英特尔的首席技术官麦克迈克· 梅伯里博士也在今年的国际VLSI会议上称希望英特尔能在五年之内实现全环绕栅极晶体管的量产。那么这样一个备受各大半导体厂商青睐的晶体管结构究竟是什么样的呢?

平面型晶体管到鳍式结构的转变

要搞清全环绕栅极技术,我们首先要从场效应晶体管(Field Effect Transistor)说起。所谓的晶体管,是指一种等效于水龙头作用的电子器件。水龙头可以用来控制水流的大小以及开关,与之类似晶体管的作用是控制电流的大小与开关。这里面另外一个关键词是场效应,指的是这种对电流的控制是通过施加一个电场来实现的。如下图所示的晶体管结构中,我们可以 通过对栅极施加一个电压从而在通道内部产生一个电场。这个电场的大小可以被用来调节源极和漏记之间电流的大小。也由此可见,决定场效应晶体管效率的一个重要因素就是栅极对通道的控制能力。

平面型场效应晶体管的结构

根据电阻的定义

,我们可以简单估算出源极到漏极之间电阻的大小是和栅极的长度成正比的。栅极越小,在同样的电压下能实现的电流也越大。这是决定晶体管性能的一个关键参数,也因此早期的技术节点往往是根据栅极的长度来命名的。所谓的10微米节点,指的就是栅极的长度最小为10微米。自从引入鳍式晶体管结构之后,技术节点中的数字仅仅是一个营销代号,已经不再和晶体管的任何尺寸直接对应。

上图中另外一个值得注意的地方是通道的长度并不等于栅极的长度。这是因为源极和漏极是通过离子注入(ion-implantation)实现的。在离子注入的过程中,会有离子扩散到栅极下方,形成所谓的扩散层。扩散层的存在,导致了在32纳米节点之后,栅极长度无法进一步缩小(避免漏极和源极之间直接短路)。英特尔也因此在之后的22纳米节点引入了鳍式晶体管。

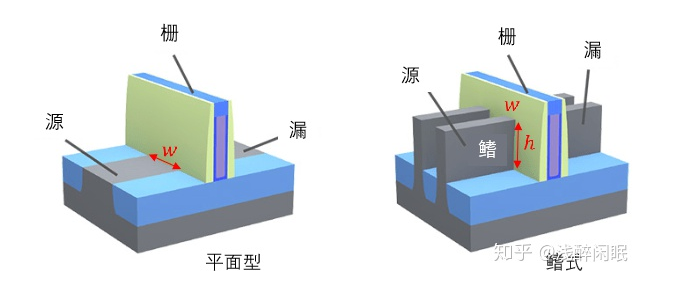

平面型与鳍式晶体管的结构对比(图片来源:Lam Research)

从平面型晶体管过渡到鳍式晶体管,栅极对通道内电场的控制能力大幅提升。原先栅极与通道的接触面积仅仅是由通道的宽度

决定的,而在鳍式晶体管中则是由

决定。更大的接触面积导致了通道内电流传输的横截面积更大,因而对应的电阻更小电流更高。

鳍式晶体管除了实现对通道更好的控制,另一个重要改进是允许栅极的长度进一步缩小。在平面型晶体管中,源极和漏极的生产是通过离子注入实现的。而在鳍式晶体管中,源极和漏极的则是在栅极做好之后直接在鳍上外延生长(Source-Drain Epitaxy)。此时由于栅极的阻断,不会出现扩散层,也因此不会有短沟效应的问题。

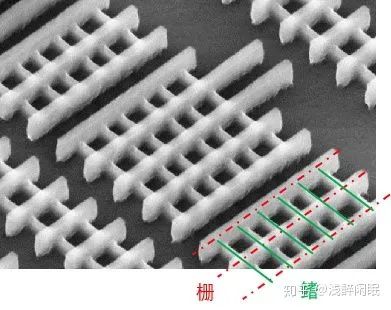

下图是英特尔在22纳米节点首次引入鳍式晶体管时给出的扫描电子显微镜照片。从图中我们可以看到,每一个单元都包含着两组鳍,每组内部各三个。在另外一个方向上,更高的线则是栅线。鳍式晶体管的尺寸缩小的一个重要衡量参数就是鳍线(Fin Line)和栅线(Gate Line)的重复周期。其中鳍线的周期是半导体器件中所有结构中最小的周期,而栅线的周期对整个晶体管的性能有决定性的影响。在22纳米节点,鳍线和栅线的周期分别为60,90纳米。而到了5纳米节点,鳍线和栅线的周期仅为27,54纳米。

鳍式晶体管的栅线和鳍线(图片来源:Intel)

5纳米之后,鳍式晶体管将会面临一系列的问题。首先随着栅线之间的间距进一步减小,很难再像之前那样在一个单元内填充多个鳍线。而如果只做一个鳍线的话,生产工艺又很难保证不同器件之间性能一致。因为控制多个鳍线的平均尺寸要远比控制单个鳍线的尺寸容易得多。其次也是更为致命的问题是,随着栅线之间的间距进一步减小,鳍式晶体管的静电问题急速加剧并直接制约晶体管性能的进一步提升。这里所说的静电问题是指鳍式晶体管本身的结构带来的一系列寄生电容以及电阻的问题。例如栅极与栅极之间的寄生电容,栅极与通道之间的寄生电容,栅极与金属电极之间的寄生电容,以及源极与漏极之间的寄生电阻等问题。IMEC之前的模拟表明,当栅线之间的间距缩小至40纳米之后,鳍式晶体管的性能将会趋于饱和。因此,在5纳米之后,工业界迫切需要一个新的结构来替代鳍式晶体管结构,这就带来了全环绕栅极晶体管。

全环绕栅极晶体管

前文中我们提到,工业界迫切需要一个新的晶体管结构来需要满足以下几个需求:

1. 新的结构所需的生产工艺应该与鳍式晶体管相似,可以继续使用现有的设备以及技术成果;

2. 新的结构应实现对通道更好的控制,例如栅极与通道之前的接触面积更大;

3. 新的结构带来的寄生电容和电阻问题应得到显著改善;

全环绕栅极晶体管的出现满足了以上所有需求,从而允许摩尔定律在5纳米之后进一步前进。首先其生产工艺与鳍式晶体管相似,关键工艺步骤几乎一样(这点我们会在之后的文章中进一步讲解)。其次,全环绕栅极晶体管实现了栅极对通道之间的四面环绕,接触面积由

提升到了

。最后由于源极与漏极之间的通道横截面积显著缩小,对应的寄生电容显著降低,而寄生电阻显著增大。

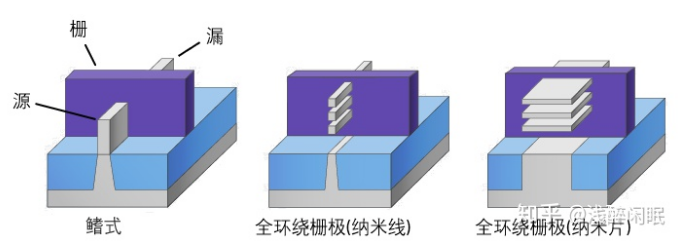

全环绕栅极晶体管的结构如下图所示,根据源极与漏极之间通道的长宽比不同,分为纳米线结构(中图)以及纳米片结构(右图)两种。在早期的研发中,包括IMEC和IBM等机构的早期工艺均采用的是纳米线结构。这是因为较高的长宽比很难控制纳米线与纳米线之间的刻蚀与薄膜生长。随着工艺的逐渐进步,在即将到来的2纳米与3纳米节点,台积电三星等众多厂商将会采用纳米片结构来实现更大的接触面积。而在纳米片之后,工业界可能会重新回到纳米线,因为纳米线可以允许更小间距以及更大的表面积/体积比。

鳍式晶体管与全环绕栅极的结构对比(图片来源:Samsung)

全环绕栅极之后晶体管的发展

根据当前的估计,水平方向上的全环绕栅极晶体管足以维持栅线的周期从54纳米缩减到30~40纳米左右(2~3代节点)。在此之后晶体管的发展,则充满了挑战与不确定性。在当前已知的几种备选方案中,垂直纳米线结构将会把纳米线调整为垂直方向;互补式结构将会把N型晶体管和P型晶体管沿着垂直方向进行堆叠;而堆叠式结构则会把多个栅极在垂直方向上经行堆叠。这些新型的结构理论上均会表现出比水平纳米线/片更加优越的性能,但是他们也需要更为先进的工艺水平才能实现商业化生产。从目前的信息来看,互补式结构最有可能是全环绕栅极晶体管之后的选择。但至于未来究竟会走向何种结构,我们将拭目以待!

下一代晶体管结构发展(图片来自IMEC)

如何生产3纳米以下全环绕栅极(Gate-All-Around)晶体管?

在前面我们探讨了工业界是如何从平面型晶体管过度到鳍式,再过度到全环绕栅极晶体管的。我们提到工业界青睐全环绕栅极晶体管的一个重要原因是这种新的结构所需的生产工艺与鳍式晶体管非常相似,可以继续使用现有的设备以及技术成果。那么全环绕栅极晶体管究竟是如何生产出来的呢?在本期文章中,我们将会详细介绍其生产工艺。在10纳米以下的先进制程中,生产一颗芯片通常需要几千道工序,因此我们没法详细地介绍每一步工艺。这里我们将重点放在那些和鳍式晶体管不同的步骤进行讨论。

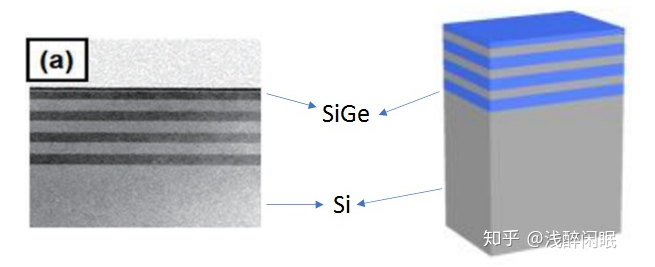

超晶格外延生长(Superlattice Epitaxy)

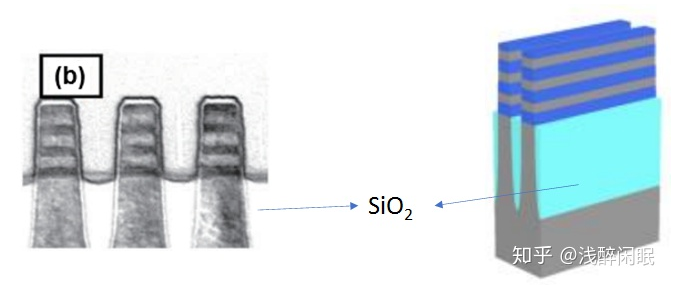

第一步:超晶格外延生长的电子显微镜图像(左)及结构示意图(右)。

全环绕栅极晶体管的生产从硅(Si)片基底开始,第一步在Si上外延生长出三个Si-SiGe超晶格结构。这一步在鳍式晶体管的生产工艺中是不需要的。如上图所示,左图中浅色的薄膜以及右图中灰色的薄膜为Si,而深色及蓝色的薄膜则为SiGe。超晶格结构中的每一层厚度均在10纳米以下,最终生产出的厚度会直接决定纳米片通道的高度以及静电性能。

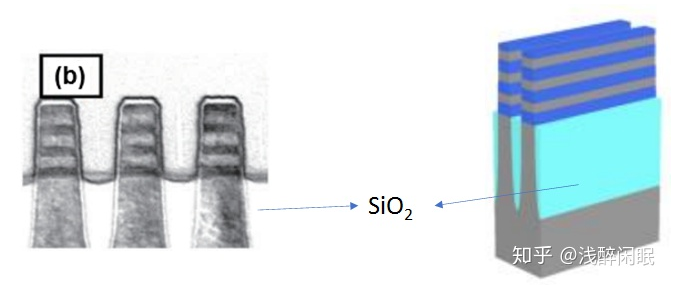

鳍式结构成型(Fin Formation)

第二步:鳍式结构成型的电子显微镜图像(左)及结构示意图(右)。

在这一步中,我们通过光刻把前一步外延生产的超晶格薄膜做成一个一个周期分布的鳍。上图中新出现的浅蓝色材料是SiO2, 它的作用是隔开相邻的两个晶体管(鳍),因此也被称作浅沟隔绝(STI Shallow Trench Isolation)。这一步工艺最早是从250纳米节点开始引入的,在鳍式晶体管中也有完全一样的生产步骤。通常鳍的周期是芯片所有结构中最小的周期,在5纳米制程中相邻的两个鳍间距已经低至30纳米,是通过自对齐四重曝光实现的(SAQP Self-Aligned Quadruple Patterning)。预计从3纳米开始,这一步将使用EUV单次曝光实现。

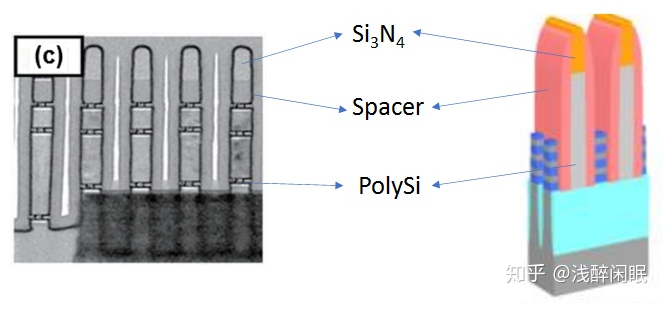

栅极成型(Gate Formation)

第三步:栅极成型的电子显微镜图像(左)及结构示意图(右)。

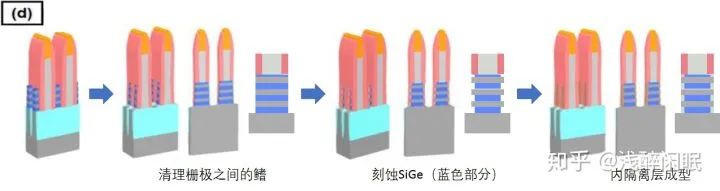

内隔离层成型(Inner Spacer Formation)

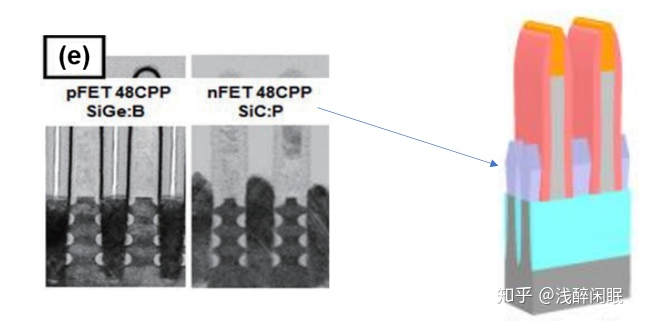

源极漏极的外延生长(Source Drain Epitaxy)

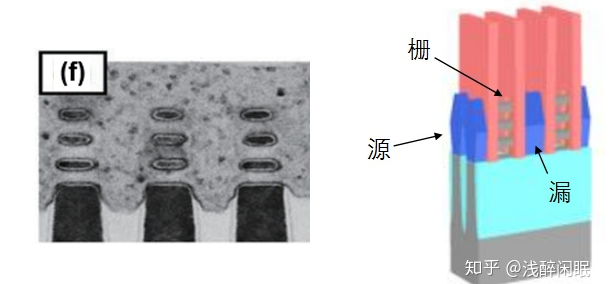

通道释放(Channel Release)

*免责声明:本文由作者原创。文章内容系作者个人观点,半导体行业观察转载仅为了传达一种不同的观点,不代表半导体行业观察对该观点赞同或支持,如果有任何异议,欢迎联系半导体行业观察。

今天是《半导体行业观察》为您分享的第2447期内容,欢迎关注。

推荐阅读

★ 半导体并购的池子

半导体行业观察

『 半导体第一垂直媒体 』

实时 专业 原创 深度

识别二维码 ,回复下方关键词,阅读更多

晶圆|IP| SiC|并购|射频|台积电|Nvidia|苹果

回复

投稿

,看《如何成为“半导体行业观察”的一员 》

回复 搜索 ,还能轻松找到其他你感兴趣的文章!

-

- 半导体行业观察

-

- 摩尔芯闻