关于RISC-V,大家都是怎么想的?

2019-05-17

16:22:23

来源: 李寿鹏

点击

最近几年的芯片领域,RISC-V是一个绝对绕不过的关键词。

和X86和Arm不一样,指令集架构RISC-V因为拥有开放性,先进性,模块化和可扩展等特点,尤其是本身的开源属性,使得它不会受到任何单一公司的沉浮或者一时兴起的决定的影响。在这些多种因素的推动下,这个指令集从2011年开始走热,过去两年更吸引了国内芯片创业者的狂热追捧。

为了指导 RISC-V 指令集架构的未来发展并推动其应用,非营利性组织RISC-V 基金会于2015年成立,经过近四年的发展,目前成员数量已达到235家。日前,基金会首次在中国五座城市组织了路演,来自RISC-V领域的多个企业讲述了他们在这个领域布局和想法。

RISC-V可以怎么玩?

据网上资料显示,RISC-V是一个典型三操作数,加载-存储形式的 RISC 架构,拥有 3 个

基本指令集和 6 个扩展指令集。其中基本整数指令集体系结构 ISA 能够通过添加一个或者多个可选的指令集扩展来进行功能的增强。这种灵活性就能给开发者带来了太多的选择和玩法:

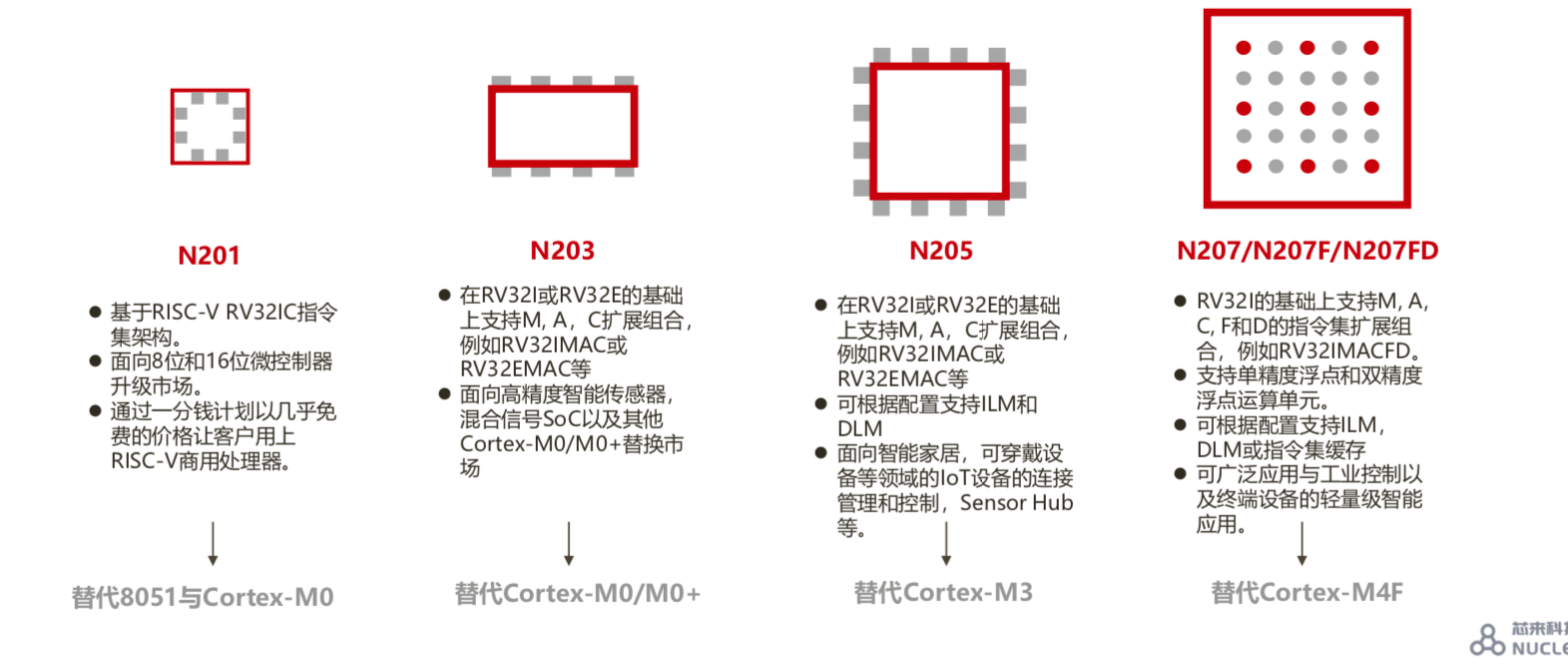

首先看专注于RISC-V处理器内核IP与解决方案的芯来科技,据该公司创始人胡振波先生介绍,他们已经目前已经发布了面向AIoT的超低功耗产品线N200系列,这系列32位超低功耗RISC-V处理器是他们专为物联网IoT终端设备的感知,连接,控制以及轻量级智能应用而设计的,从性能上看,可以直接替代arm 的Cortex-M系列。

芯来科技的N200系列

与此同时,他们还在研发面向边缘计算的嵌入式高性能产品线N900系列。其中N900系列32位处理器在功耗和性能上具有极佳的平衡性面向民用边缘计算领域,R900系 列32位处理器面向高可靠性和实时控制领域,U900系列32位和X900系列64位处理器,配合多核支持,矢量加速,以及可扩展特性,以及对Linux的支持,主要面向5G和数据中心网络通讯领域,以及多媒体,嵌入式AI等。这同样可以找到arm领域内的匹配者。

芯来科技目前的产品线

胡振波指出,芯来的目标是以处理器为平台,和客户深度合作,从客户业务需 求出发提供处理器定制服务。他们同事还推出了一项RISC-V处理器内核IP普惠计划——一分钱计划。据介绍,参与这个计划的开发者,可以从芯来科技轻松免费获取商用的RISC-V处理器内核N201,而在大规模量产时,芯来科技也仅向每颗芯片收取人民币一分钱的版税(Royalty),相对于开发者来说,这也是他们进入相关领域的一个捷径。

其次看阿里巴巴旗下的平头哥半导体。作为RISC-V基金会的铂金会员,他们除了推出了世界傻姑娘首个带有TEE的嵌入式RISC-V内核902外,他们还规划了903、905、907、910和960等多代RISC-V处理器。他们也针对不同的应用领域,规划了多个系列的产品线。公司也正在积极参与RISC-V的生态建设中去。

平头哥的RISC-V产品线

源自中科院、专注于嵌入式AI解决方案的团队澎峰科技则推做了一个名为“Perf“的开发版。据该公司张先轶先生介绍,他们认为RISC-V是体系结构领域的“Linux”,而RISC-V+AI则能爆发出巨大的应用潜力。

澎峰科技的Perf-v开发板

按照他的设想,他们以FPGA为主芯片,加入多种RISC-V软核的Perf-v开发板拥有配套工具成熟,外设借口丰富、性价比高,且还有医用、案例丰富等特性,能够为开发者提供多样化的服务。

成立于2014年的法国GreenWaves Technologies则将RISC-V核心应用到其高集成度的新型智能MCU GAP8中。据GreenWaves 张垚先生介绍,他们的物联网应用处理器可以分为两部分。其中微控制器部分使用了一颗经扩展的RISC-V内核,而计算加速部分使用了8颗基于RISC-V的扩展内核。在这个基础上加上各种外设、I/O,加上其高能效平衡的并行架构、共享指令集、硬件卷积加速引擎和快速的能源状态切换支持,这就给GAP8带来了极致的能耗,为使用电池的应用场景带来高能耗的端侧AI计算能力。

GreenWaves Technologies的GAP 8

作为最早涉足RISC-V的厂商之一,SiFive则推出了2系列、3/5系列和7系列这几个针对不同应用场景的RISC-V产品线。在他们看来,这些产品能够为存储、5G/网络、AR/VR/传感器融合、企业级SSD、边缘人工智能、可穿戴AI等应用和市场提供支持。

SiFive的产品线

台湾IP供应傻晶心科技则凭借著超过14年的商用CPU开发经验、全球累积超过160家客户以及35亿颗的量产纪录,加上自家开发环境IDE(AndeSight)和既有的DSP & ACE所拥有的优势让Andes在RISC-V市场有一席之地。从2017年推出N25/NX25开始,到2018年发布A25/AX25,再到今年的N22 & D25和接下来即将推出的A25MP/AX25MP,RISC-V正在一步步完善其产品布局,未来甚至还会推出更多级流水线高性能RISC-V CPU,满足市场的需求。

解决现有的问题方法?

在和很多RISC-V从业者交流的时候,他们都无一例外的告诉半导体行业观察记者,RISC-V面临的一个最大挑战就是生态问题或者工具问题,但其实也有很多厂商投入其中。

例如在RISC-V的一大特点指令客制方面化,过去这些操作需要开发者拥有丰富CPU专业知识及大量人力来修改既有的处理器硬件和相关软件工具,并确认其功能无误,因此加入客制化指令对许多SoC设计团队来说并不容易。但透过晶心科技的ACE设计环境,即可大幅简化加入客制化指令的步骤。

据介绍,ACE最强大的功能是能以高阶语法来描述指令,并自动产生RTL电路。例如,向量语法让开发者能像设计纯量指令一样轻鬆设计出向量指令,背景语法则能让需较长时间执行的ACE指令持续在背景同步执行,工程师亦能利用自订暂存器及自订记忆体能设定任意位元宽度的特点,让ACE指令执行宽位元的输入和输出,而这些ACE功能都有助处理器效能大幅提升。另外,COPILOT除了能容易地产生工具链,也能自动产生测试向量和交叉验证环境,帮工程师验证所设计的指令是否正确,让设计验证更为容易。

晶心科技方面强调,COPILOT设计环境是自动产生ACE指令的关键,能帮助SoC设计团队省去许多底层RTL设计工作,例如运算码选取、指令解码、运算元参照、输入运算元存取、资料相依性检查及结果彙整。ACE相当易于使用,不需熟悉处理器管线设计也能快速上手,这让工程师能专注于利用ACE强大的功能,而不是花费时间摸索CPU管线的运作方式。

那就意味着工程师只须建立一个ACE描述档来定义输入/输出介面及以C语言描述的指令意涵,再加上一个相对应的精简Verilog档来描述其逻辑电路,即可利用Custom-OPtimized Instruction deveLOpment Tools™ (COPILOT) 工具于短短数分钟内产生具扩充指令的CPU和相关软件工具链。

为SoC提供部分析及监测技术的先锋企业UltraSoC则为RISC-V设计带来了更多的支持。

2018年初,该公司宣布推出业界第一款也是唯一一款专为RISC-V设计的商用追踪编码器IP,提供了一种实时监控CPU程序执行的机制。 它对指令执行和数据内存访问进行编码(可选),并输出一种高度压缩的追踪格式。 外部软件可以随后获取此数据并使用它来重建程序执行流程。 UltraSoC方面表示,他们的RISC-V追踪编码器是为符合RISC-V标准而开发的,同时提供许多强大的功能,如数据和指令追踪、一系列计数器和定时器以及快速分析描绘工具,使其与实现基线RISC-V标准要求的开源代替产品明显不同。

“RISC-V Trace Encoder追踪编码器支持32位和64位RISC-V设计,该IP块可与UltraSoC产品组合的其他部分顺利集成,支持开放式和行业标准架构,以将自分析功能置于SoC的核心”,Ultra SoC方面补充说。

在2019年嵌入式世界展上,Ultra SoC宣布,他们的UltraDevelop 2集成开发环境(IDE)可用于beta测试。据了解,这个发布于2018年10月的产品集成了调试、运行控制和性能调优功能,可为硬件、固件和软件的运行提供集成化的视图,以及高级异常检测、可视化和数据科学等功能。利用UltraSoC系统级的片上监控和分析基础架构的巨大潜力,为SoC设计人员在选择开发平台时提供功能和灵活性的最佳组合,并且有能力对来自RISC-V等供应商的20多种处理器架构进行实时运行控制,帮助芯片和系统开发人员提供可操作的洞察力,从而大幅降低开发成本和缩短产品上市时间,并改善最终产品的整体质量。

从整个处理器架构市场来看,RISC-V相对还是比较薄弱,但相信在RISC-V 基金会的推动、以及各大企业的支持下,我们很快就能看到这个全新的架构在各个领域大放异彩,这个产品届时也必将给中国芯片产业带来全新的局面。

和X86和Arm不一样,指令集架构RISC-V因为拥有开放性,先进性,模块化和可扩展等特点,尤其是本身的开源属性,使得它不会受到任何单一公司的沉浮或者一时兴起的决定的影响。在这些多种因素的推动下,这个指令集从2011年开始走热,过去两年更吸引了国内芯片创业者的狂热追捧。

为了指导 RISC-V 指令集架构的未来发展并推动其应用,非营利性组织RISC-V 基金会于2015年成立,经过近四年的发展,目前成员数量已达到235家。日前,基金会首次在中国五座城市组织了路演,来自RISC-V领域的多个企业讲述了他们在这个领域布局和想法。

RISC-V可以怎么玩?

据网上资料显示,RISC-V是一个典型三操作数,加载-存储形式的 RISC 架构,拥有 3 个

基本指令集和 6 个扩展指令集。其中基本整数指令集体系结构 ISA 能够通过添加一个或者多个可选的指令集扩展来进行功能的增强。这种灵活性就能给开发者带来了太多的选择和玩法:

首先看专注于RISC-V处理器内核IP与解决方案的芯来科技,据该公司创始人胡振波先生介绍,他们已经目前已经发布了面向AIoT的超低功耗产品线N200系列,这系列32位超低功耗RISC-V处理器是他们专为物联网IoT终端设备的感知,连接,控制以及轻量级智能应用而设计的,从性能上看,可以直接替代arm 的Cortex-M系列。

芯来科技的N200系列

与此同时,他们还在研发面向边缘计算的嵌入式高性能产品线N900系列。其中N900系列32位处理器在功耗和性能上具有极佳的平衡性面向民用边缘计算领域,R900系 列32位处理器面向高可靠性和实时控制领域,U900系列32位和X900系列64位处理器,配合多核支持,矢量加速,以及可扩展特性,以及对Linux的支持,主要面向5G和数据中心网络通讯领域,以及多媒体,嵌入式AI等。这同样可以找到arm领域内的匹配者。

芯来科技目前的产品线

胡振波指出,芯来的目标是以处理器为平台,和客户深度合作,从客户业务需 求出发提供处理器定制服务。他们同事还推出了一项RISC-V处理器内核IP普惠计划——一分钱计划。据介绍,参与这个计划的开发者,可以从芯来科技轻松免费获取商用的RISC-V处理器内核N201,而在大规模量产时,芯来科技也仅向每颗芯片收取人民币一分钱的版税(Royalty),相对于开发者来说,这也是他们进入相关领域的一个捷径。

其次看阿里巴巴旗下的平头哥半导体。作为RISC-V基金会的铂金会员,他们除了推出了世界傻姑娘首个带有TEE的嵌入式RISC-V内核902外,他们还规划了903、905、907、910和960等多代RISC-V处理器。他们也针对不同的应用领域,规划了多个系列的产品线。公司也正在积极参与RISC-V的生态建设中去。

平头哥的RISC-V产品线

源自中科院、专注于嵌入式AI解决方案的团队澎峰科技则推做了一个名为“Perf“的开发版。据该公司张先轶先生介绍,他们认为RISC-V是体系结构领域的“Linux”,而RISC-V+AI则能爆发出巨大的应用潜力。

澎峰科技的Perf-v开发板

按照他的设想,他们以FPGA为主芯片,加入多种RISC-V软核的Perf-v开发板拥有配套工具成熟,外设借口丰富、性价比高,且还有医用、案例丰富等特性,能够为开发者提供多样化的服务。

成立于2014年的法国GreenWaves Technologies则将RISC-V核心应用到其高集成度的新型智能MCU GAP8中。据GreenWaves 张垚先生介绍,他们的物联网应用处理器可以分为两部分。其中微控制器部分使用了一颗经扩展的RISC-V内核,而计算加速部分使用了8颗基于RISC-V的扩展内核。在这个基础上加上各种外设、I/O,加上其高能效平衡的并行架构、共享指令集、硬件卷积加速引擎和快速的能源状态切换支持,这就给GAP8带来了极致的能耗,为使用电池的应用场景带来高能耗的端侧AI计算能力。

GreenWaves Technologies的GAP 8

作为最早涉足RISC-V的厂商之一,SiFive则推出了2系列、3/5系列和7系列这几个针对不同应用场景的RISC-V产品线。在他们看来,这些产品能够为存储、5G/网络、AR/VR/传感器融合、企业级SSD、边缘人工智能、可穿戴AI等应用和市场提供支持。

SiFive的产品线

台湾IP供应傻晶心科技则凭借著超过14年的商用CPU开发经验、全球累积超过160家客户以及35亿颗的量产纪录,加上自家开发环境IDE(AndeSight)和既有的DSP & ACE所拥有的优势让Andes在RISC-V市场有一席之地。从2017年推出N25/NX25开始,到2018年发布A25/AX25,再到今年的N22 & D25和接下来即将推出的A25MP/AX25MP,RISC-V正在一步步完善其产品布局,未来甚至还会推出更多级流水线高性能RISC-V CPU,满足市场的需求。

解决现有的问题方法?

在和很多RISC-V从业者交流的时候,他们都无一例外的告诉半导体行业观察记者,RISC-V面临的一个最大挑战就是生态问题或者工具问题,但其实也有很多厂商投入其中。

例如在RISC-V的一大特点指令客制方面化,过去这些操作需要开发者拥有丰富CPU专业知识及大量人力来修改既有的处理器硬件和相关软件工具,并确认其功能无误,因此加入客制化指令对许多SoC设计团队来说并不容易。但透过晶心科技的ACE设计环境,即可大幅简化加入客制化指令的步骤。

据介绍,ACE最强大的功能是能以高阶语法来描述指令,并自动产生RTL电路。例如,向量语法让开发者能像设计纯量指令一样轻鬆设计出向量指令,背景语法则能让需较长时间执行的ACE指令持续在背景同步执行,工程师亦能利用自订暂存器及自订记忆体能设定任意位元宽度的特点,让ACE指令执行宽位元的输入和输出,而这些ACE功能都有助处理器效能大幅提升。另外,COPILOT除了能容易地产生工具链,也能自动产生测试向量和交叉验证环境,帮工程师验证所设计的指令是否正确,让设计验证更为容易。

晶心科技方面强调,COPILOT设计环境是自动产生ACE指令的关键,能帮助SoC设计团队省去许多底层RTL设计工作,例如运算码选取、指令解码、运算元参照、输入运算元存取、资料相依性检查及结果彙整。ACE相当易于使用,不需熟悉处理器管线设计也能快速上手,这让工程师能专注于利用ACE强大的功能,而不是花费时间摸索CPU管线的运作方式。

那就意味着工程师只须建立一个ACE描述档来定义输入/输出介面及以C语言描述的指令意涵,再加上一个相对应的精简Verilog档来描述其逻辑电路,即可利用Custom-OPtimized Instruction deveLOpment Tools™ (COPILOT) 工具于短短数分钟内产生具扩充指令的CPU和相关软件工具链。

为SoC提供部分析及监测技术的先锋企业UltraSoC则为RISC-V设计带来了更多的支持。

2018年初,该公司宣布推出业界第一款也是唯一一款专为RISC-V设计的商用追踪编码器IP,提供了一种实时监控CPU程序执行的机制。 它对指令执行和数据内存访问进行编码(可选),并输出一种高度压缩的追踪格式。 外部软件可以随后获取此数据并使用它来重建程序执行流程。 UltraSoC方面表示,他们的RISC-V追踪编码器是为符合RISC-V标准而开发的,同时提供许多强大的功能,如数据和指令追踪、一系列计数器和定时器以及快速分析描绘工具,使其与实现基线RISC-V标准要求的开源代替产品明显不同。

“RISC-V Trace Encoder追踪编码器支持32位和64位RISC-V设计,该IP块可与UltraSoC产品组合的其他部分顺利集成,支持开放式和行业标准架构,以将自分析功能置于SoC的核心”,Ultra SoC方面补充说。

在2019年嵌入式世界展上,Ultra SoC宣布,他们的UltraDevelop 2集成开发环境(IDE)可用于beta测试。据了解,这个发布于2018年10月的产品集成了调试、运行控制和性能调优功能,可为硬件、固件和软件的运行提供集成化的视图,以及高级异常检测、可视化和数据科学等功能。利用UltraSoC系统级的片上监控和分析基础架构的巨大潜力,为SoC设计人员在选择开发平台时提供功能和灵活性的最佳组合,并且有能力对来自RISC-V等供应商的20多种处理器架构进行实时运行控制,帮助芯片和系统开发人员提供可操作的洞察力,从而大幅降低开发成本和缩短产品上市时间,并改善最终产品的整体质量。

从整个处理器架构市场来看,RISC-V相对还是比较薄弱,但相信在RISC-V 基金会的推动、以及各大企业的支持下,我们很快就能看到这个全新的架构在各个领域大放异彩,这个产品届时也必将给中国芯片产业带来全新的局面。

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 全球首款NFC PSSD亮相CES 2025,江波龙创新产品备受业界瞩目

- 2 英特尔发布两款芯片,发力软件定义汽车

- 3 合见工软,完成近10亿元新融资

- 4 ASML的投资者日,透露了哪些行业发展趋势?