重磅发布:日观芯设IC设计全流程管理软件RigorFlow 2.0

2024-05-13

15:49:00

来源: 互联网

点击

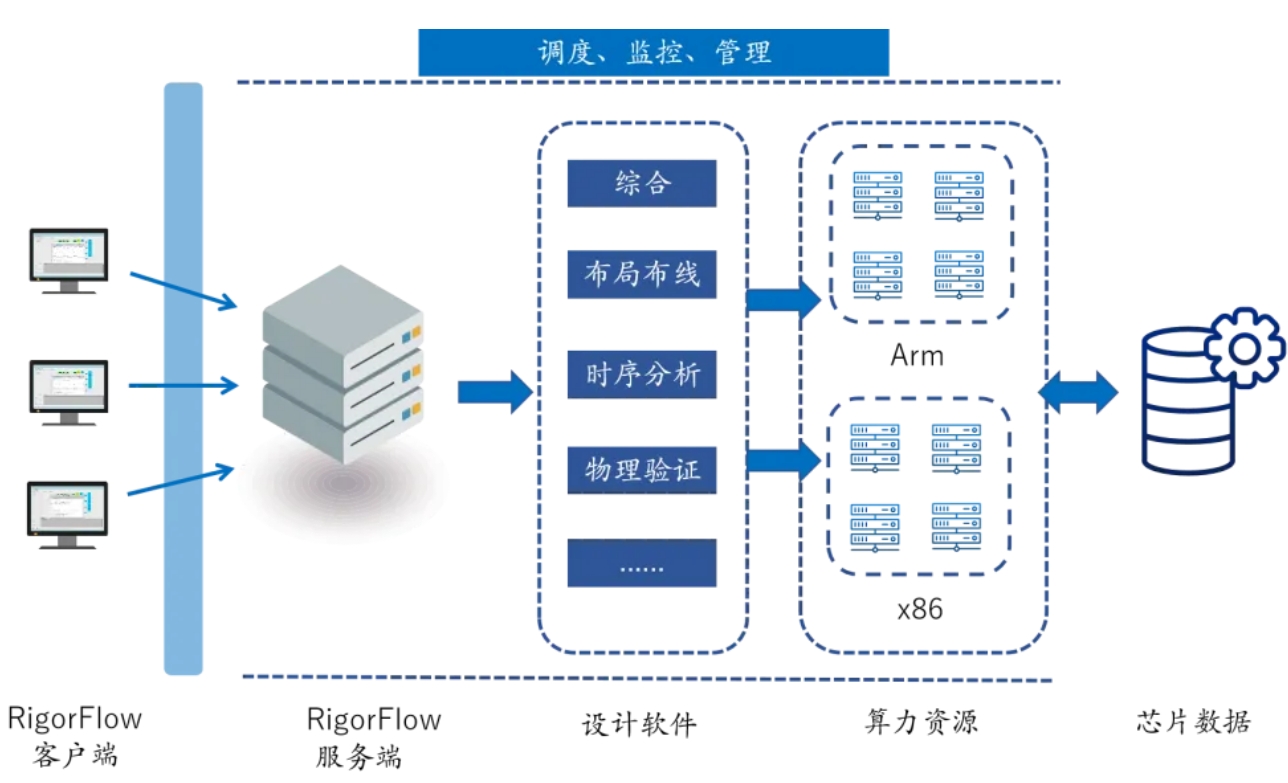

RigorFlow是上海日观芯设自动化有限公司旗下一款创新的管理芯片设计全流程的EDA/CAD软件,旨在解决集成电路(IC)设计流程中多种难题与痛点,并大幅提升IC设计工程师的工作效率以及开发团队整体管理效率。

此前RigorFlow 1.0版本通过其自定义流程管理器、运行状态监控管理器和关键日志数据提取器,有效推进了IC设计流程的自动化、提供了实时监控,并解决了数据提取的难题。这不仅极大的提升了设计效率和增加了流程透明度,还使团队能够第一时间发现并解决问题,优化资源分配,从而降低错误率和模块间的迭代困难度,最终加快产品的开发上市进程。

经过过去一年国内某头部设计公司芯片开发CAD团队的打磨,以及国内某头部ASIC团队在超大规模算力芯片、车规芯片以及AI芯片等复杂SOC芯片上全流程的配合,日观芯设全流程管理产品得到了进一步升级与优化,RigorFlow2.0版本基于市场的反馈应运而生。

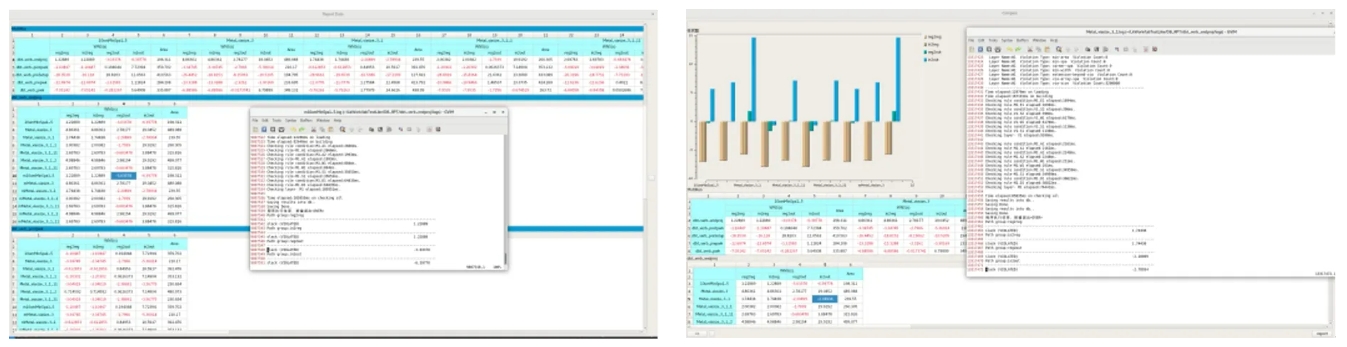

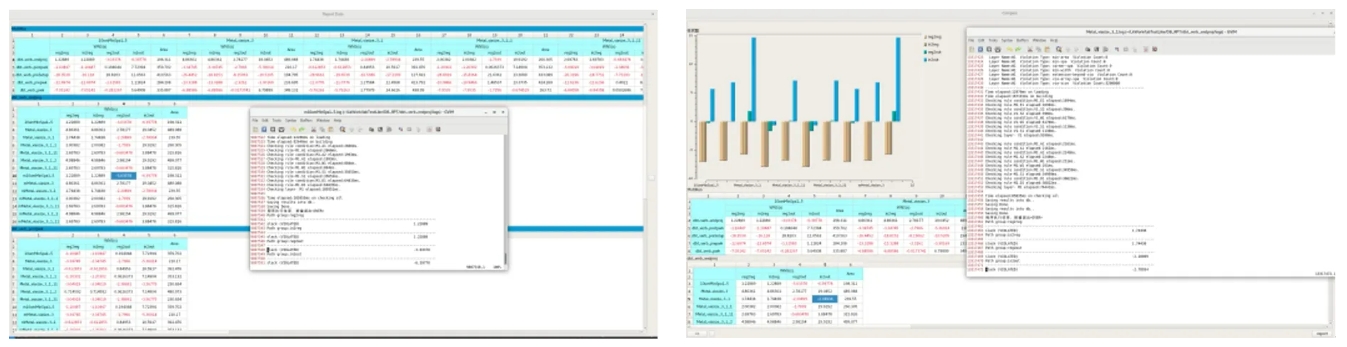

具体来说,RigorFlow 2.0在其前身1.0版本的基础上,进行了全面升级,特别是强化了实时数据存储与可视化统计分析功能。这一新功能使用户能够直观地比较不同设计方案的性能和效率,进而制定出更加科学、高效的设计决策,显著提升项目成功率。

图1:数据对比与可视化统计分析

此外,RigorFlow2.0还为复杂的工作流程管理提供一整套完备系统,它包括了以下方面:

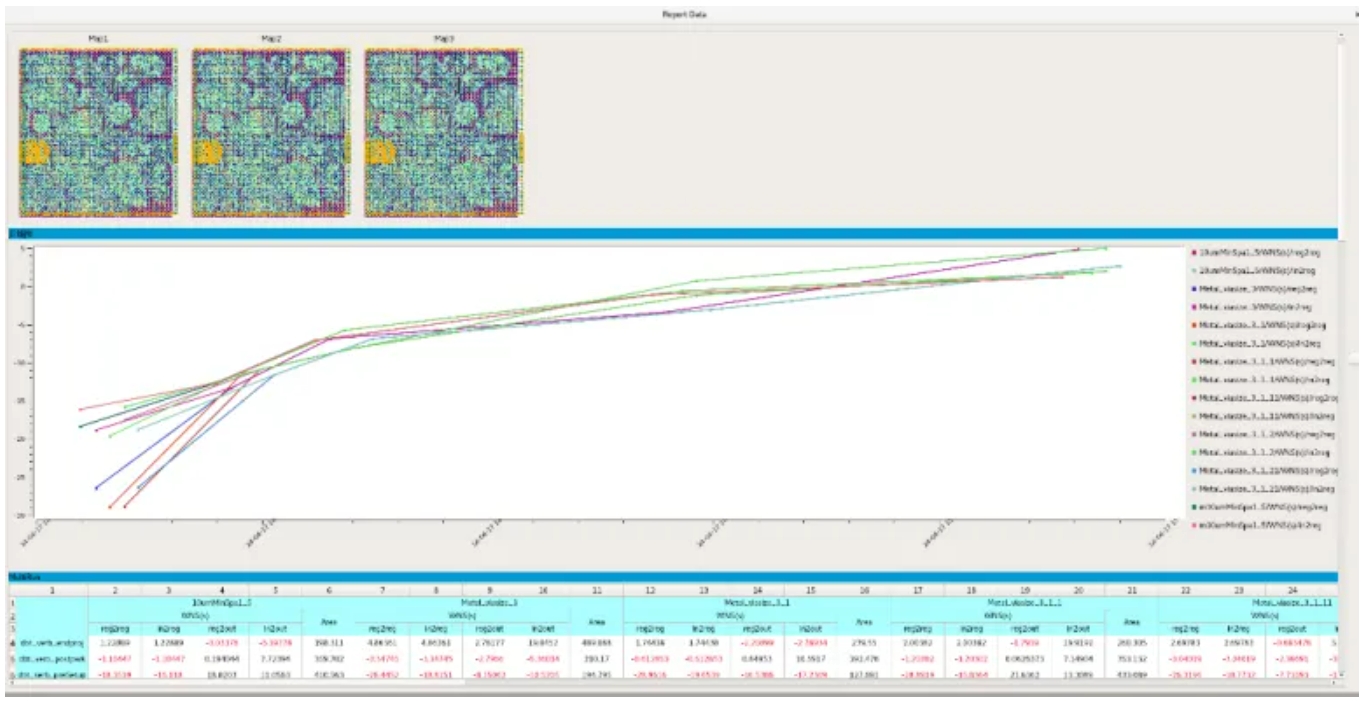

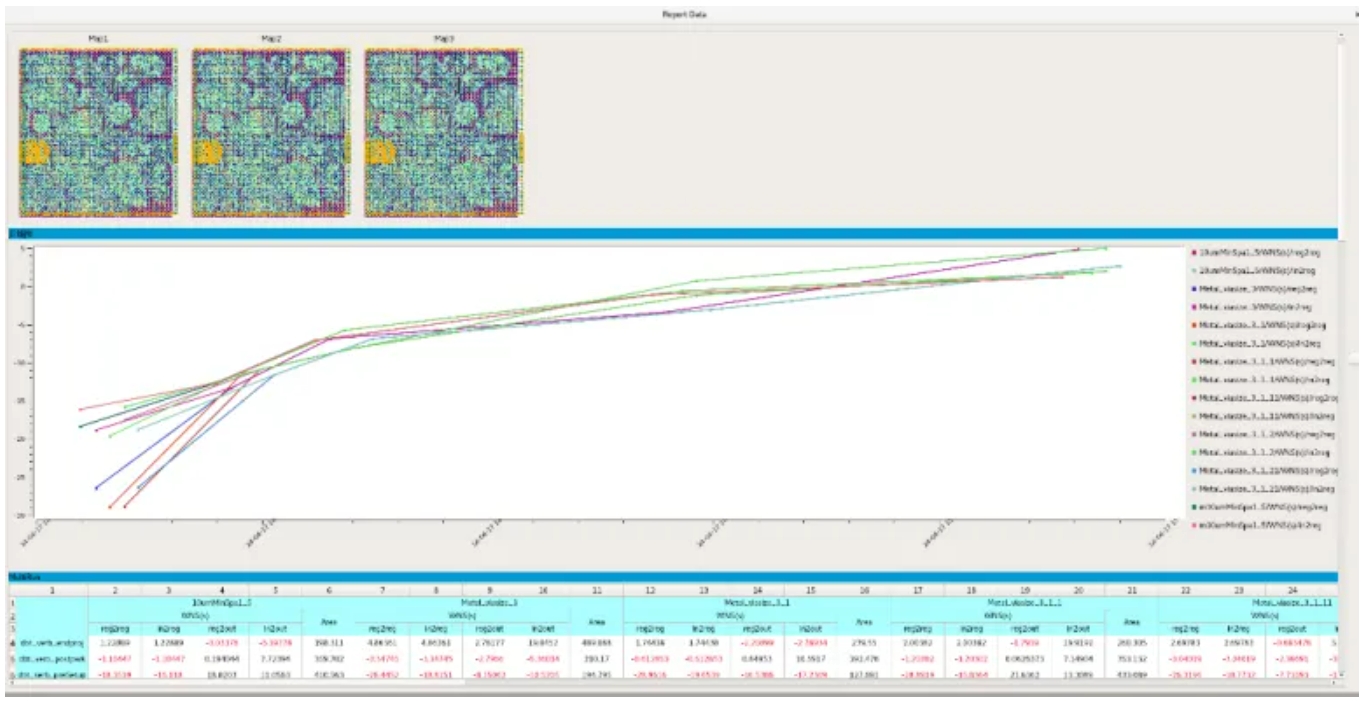

1.运行状态监控管理器:运行时对状态进行实时监控,实现状态的即时捕获与更新。

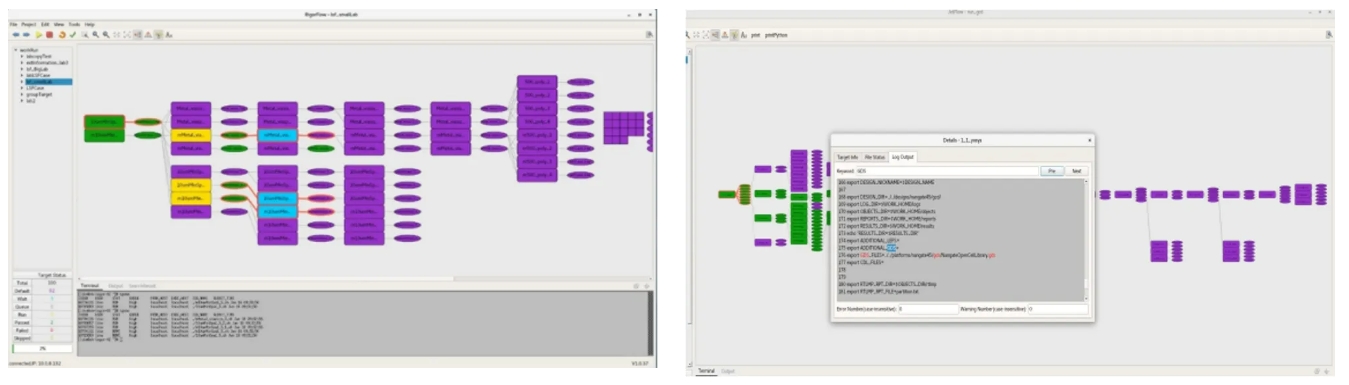

2.清晰明了的图形化流程管理:RigorFlow采用颜色编码GUI设计,结合网格视图报告,让用户可以直观识别并快速定位故障作业,便于迅速调试和解决问题。

图2:运行状态监控管理

3.多维度可视化统计分析:一键汇总展示当前工程关键数据,支持多个数据维度对比数据,方便设计人员查看任务的关键数据以及比较结果优劣。

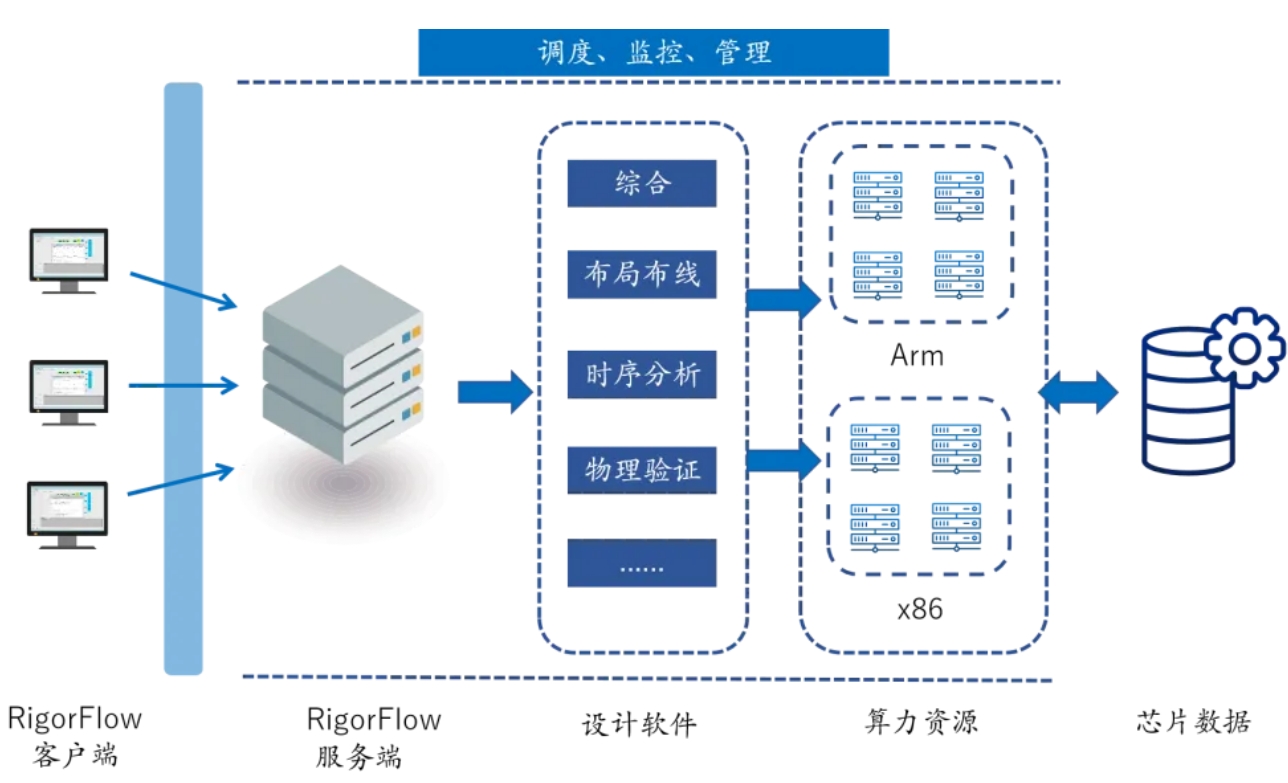

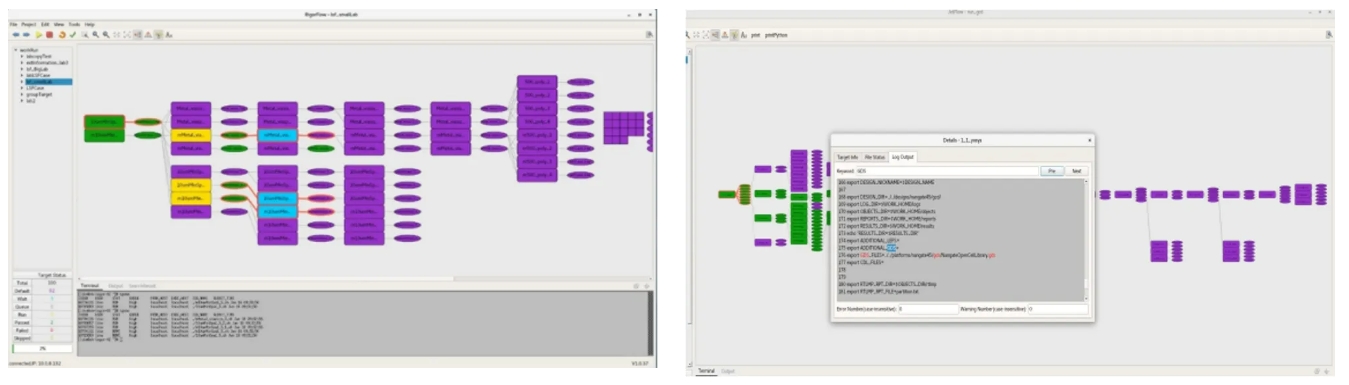

4.超大吞吐容量:RigorFlow设计轻量,内置调度程序,能够高效处理数百万作业,显著加快开发速度。

5.先进的分布式架构:利用先进的并行机制,RigorFlow能够将工作负担分配至本地及云端的分布式计算环境,同时支持批处理模式,优化资源使用。

图3:先进的分布式架构

6.透明的团队协作:通过直观的视图(包括网格、节点、流程图和依赖关系图)和抽象概念,RigorFlow促进组织内复杂工作流程的部署与共享,大大促进了团队合作。

在具体实操中,前述头部IC设计公司CAD团队已经完整导入RigorFlow2.0,并逐步在公司的实际项目中导入。通过将项目整体开发切换到RigorFlow2.0平台上,项目开发整体ROI得到了明显提升:举个例子,在日常的模块开发中,如果一个普通工程师正常可以承接3个普通模块,那么基于RigorFlow2.0平台,该工程师可以承接4个普通模块,并且开发流程还可以显著缩短将近20%的时间。

同时,经过2023年一年在国内某头部ASIC vendor处的磨合,RigorFlow进一步开发和优化了数据报告管理系统,通过对数字芯片开发中各个流程的数据报告深度挖掘和分析,极大的提高了管理团队的工作效率并且大幅度降低管理团队每天分析项目进度和瓶颈模块的数据分析时间,从而进一步提升项目管理者所能有效管理的团队规模。

另一方面,有效的数据分析和数据管理也进一步帮助ASIC vendor和客户的有效沟通。通过简洁明了的data talk,极大程度的减少了沟通障碍从而降低了沟通成本。大幅度提升了客户满意度。无论是在小型还是大型项目中,RigorFlow都展现出了其卓越的性能和价值。

为了进一步帮助国内芯片设计公司提升竞争力,日观芯设还将会在接下来的半年时间内为芯片设计企业提供本地部署和整体设计流程环境迁移能力,并推出个性化流程定制服务。

作为国产EDA的新兴力量,日观芯设将继续致力于推动IC设计流程管理的革新,为国内的半导体行业提供更加强大和高效的设计工具。

与此同时,为了庆祝RigorFlow2.0发布,日观芯设将推出限时免费的活动,欢迎大家扫描下方二维码或发送试用请求到日观的官方合作邮箱business@rigoron.com,日观会联系大家提供宝贵的免费使用的机会。

责任编辑:Ace

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根

- 4 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来