DAC 61周年 | 日观芯设携一站式数字后端签核平台重磅亮相

2024-06-21

17:05:00

来源: 互联网

点击

2024年6月23-27日,在一年一度的全球电子设计自动化盛会DAC(Design Automation Conference)上,面向来自世界各地的业内头部芯片设计厂商 ,作为EDA签核领域的后起之秀上海日观芯设自动化有限公司(Rigoron),届时将携全新升级的一站式数字后端签核工具系列重磅亮相61届DAC会议,并隆重发布并现场展示数字签核领域的一系列产品:

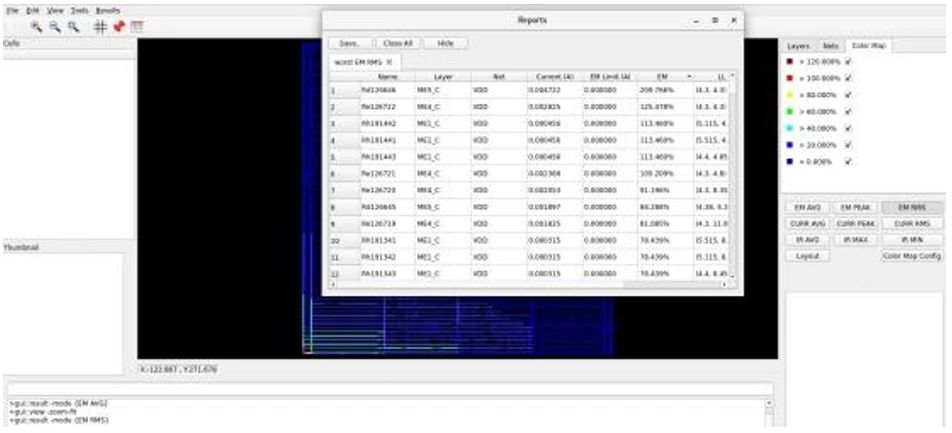

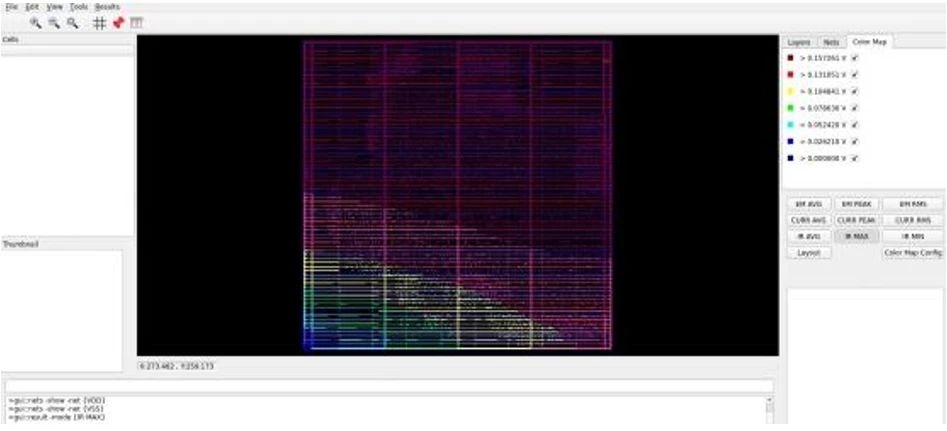

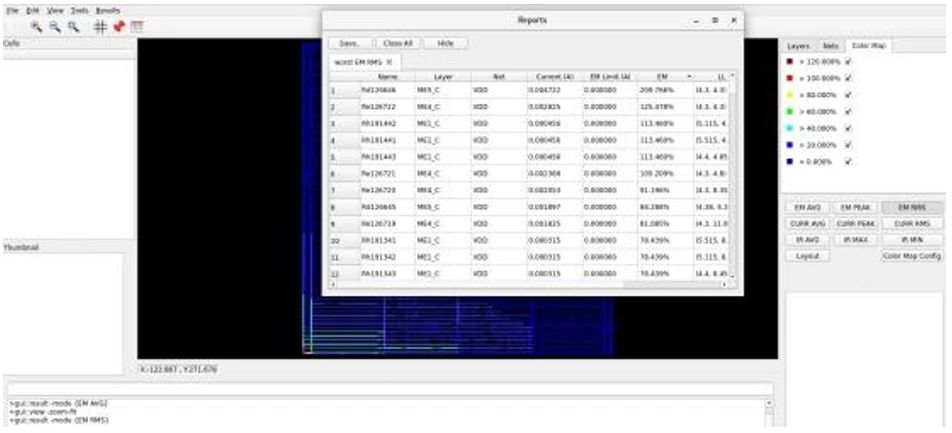

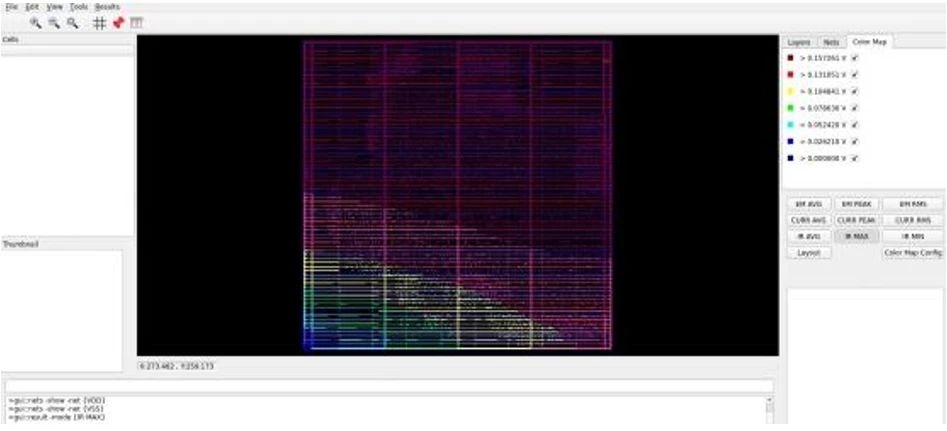

图3:RigorEMIR GUI界面

· IC设计全流程管理软件RigorFlow 2.0

· 时序约束验证与管理软件RigorCons

· 静态时序分析软件RigorTime

· 物理验证及签核软件RigorDRC

· 功耗分析及签核软件RigorEMIR

与此同时,日观芯设还将宣布RigorFlow2.0芯片设计效率管理工具现已经成功进入批量商用阶段,而RigorCons时序约束验证与管理软件和RigorDRC 物理验证工具也正于业内领军芯片设计厂商的定点试用中。这些重大进展标志着上海日观芯设自动化有限公司在数字后端签核和芯片设计自动化领域的持续创新和发展。

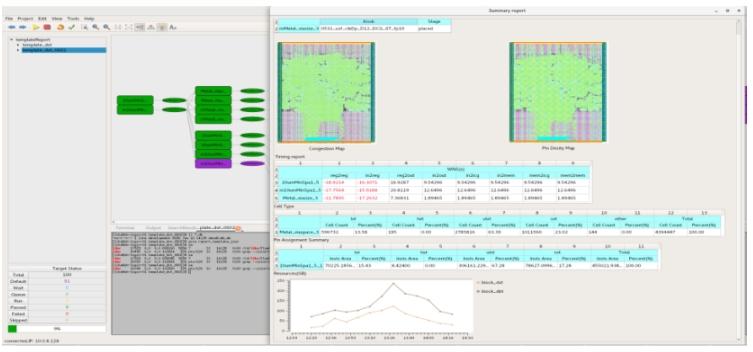

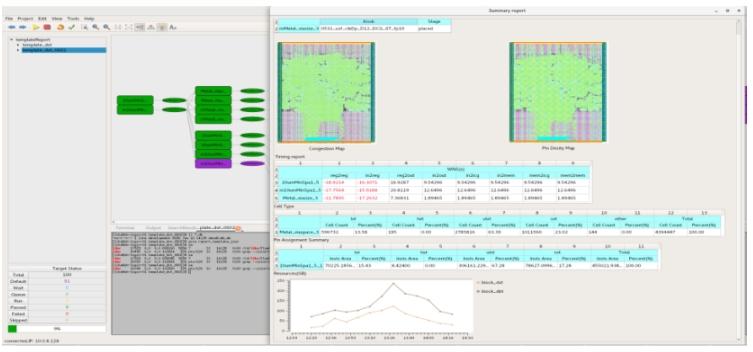

RigorFlow是日观芯设旗下一款创新的管理芯片设计全流程的EDA/CAD软件,旨在解决集成电路(IC)设计流程中多种难题与痛点,并大幅提升IC设计工程师的工作效率以及开发团队整体管理效率。

此次亮相DAC的RigorFlow 2.0在其前身1.0版本的基础上,进行了全面升级,特别是强化了实时数据存储与可视化统计分析功能。这一新功能使用户能够直观地比较不同设计方案的性能和效率,进而制定出更加科学、高效的设计决策,显著提升项目成功率。

图1:RigorFlow2.0数据对比与可视化统计分析

RigorFlow2.0还为复杂的工作流程管理提供一整套完备系统,它包括了:运行状态监控管理器、清晰明了的图形化流程管理、多维度可视化统计分析、超大吞吐容量、先进的分布式架构、透明的团队协作。

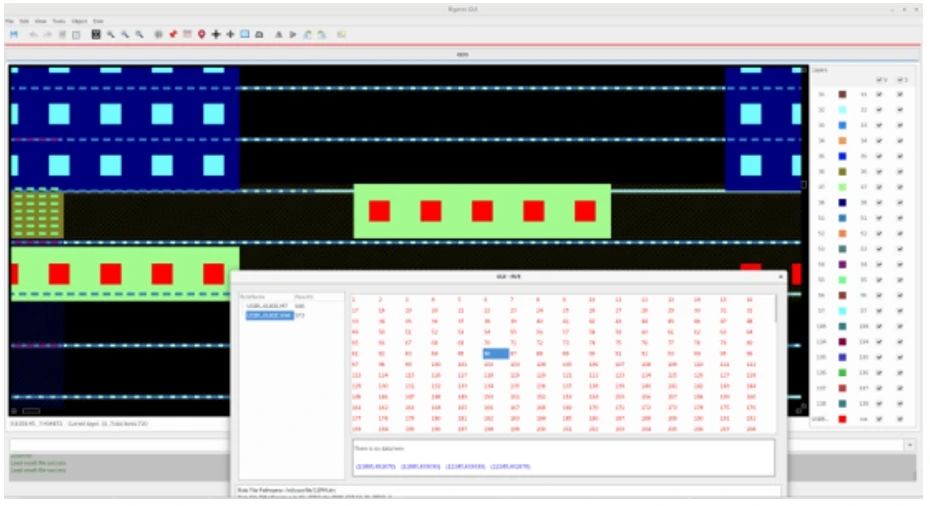

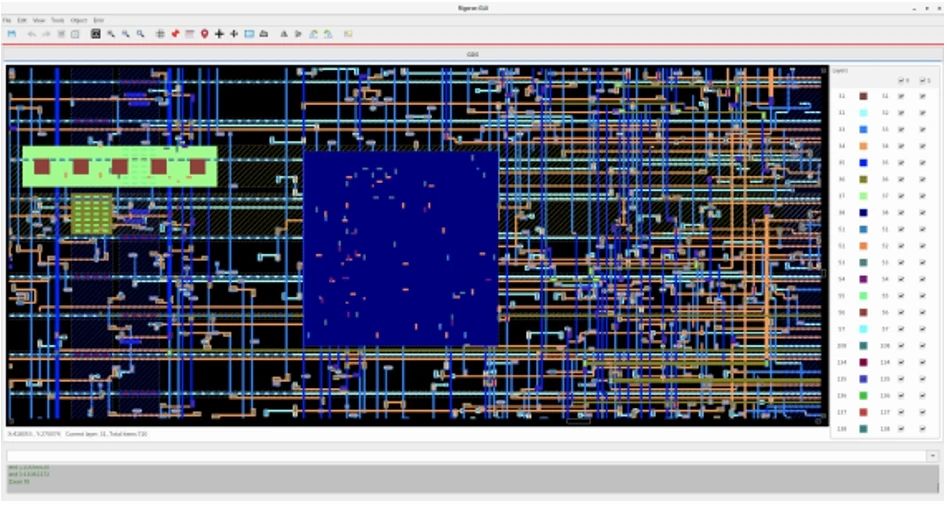

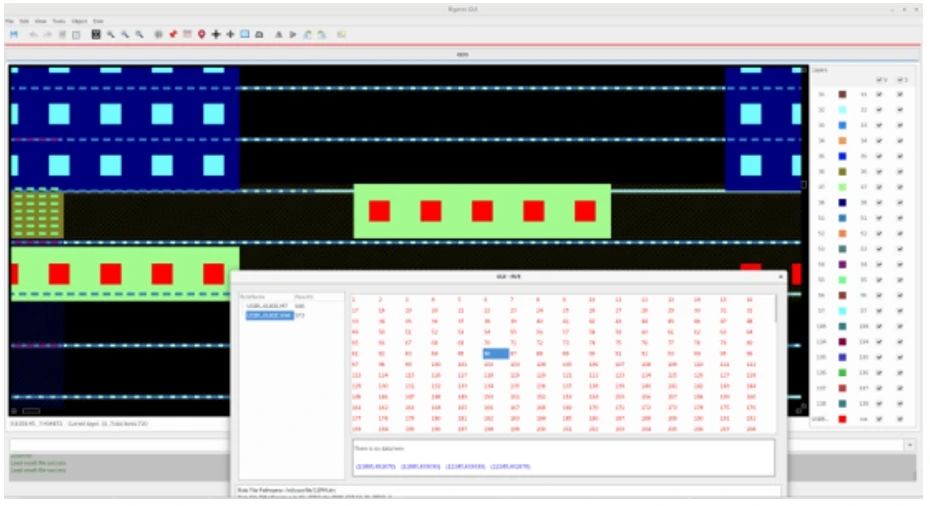

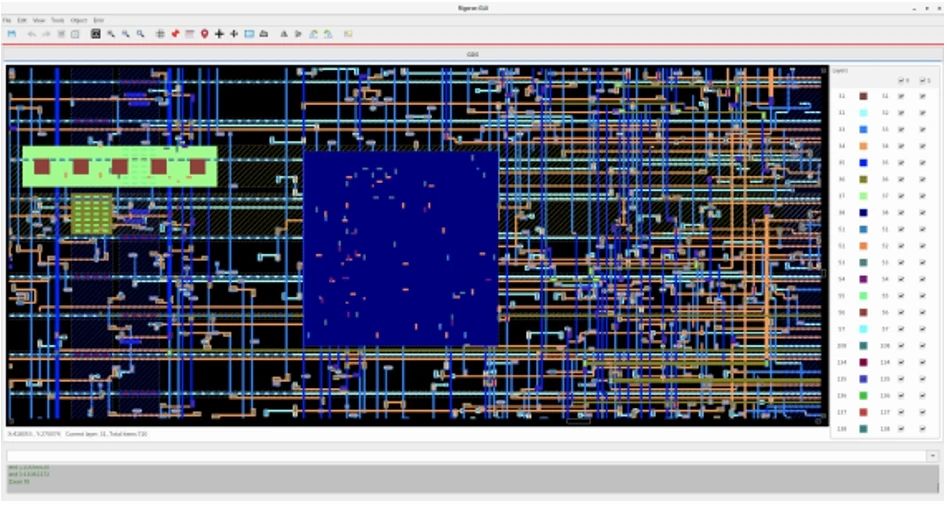

另一方面,RigorDRC 也是我们推出的一款重要里程碑式的物理验证工具。它能够快速而准确地检测和纠正电路设计中的物理错误,支持互连线 、单元/ 器件的设计 规则检查等。具有支持先进工艺节点的能力、.运行效率高于国外同类工具,更适宜于处理超大规模的版图,包含友好的图形界面工具,便于设计者快速修复发现的设计违例之处。

图2:RigorDRC GUI界面

此外,我们的RigorCons产品正在重点客户的定点试用中。RigorCons是一个强大的时序约束验证和管理工具,它可以帮助验证SoC、5G、GPU、CPU等芯片中的复杂SDC时序约束。为任何层次结构和模式自动生成和管理SDC,从而显著缩短时序收敛周期,保证签核的质量和效率。

与此同时,在本次DAC展会中日观芯设也将宣布,经过了过去一年半日观EMIR团队的努力,旗下功率分析和EMIR等技术产品将于下半年推出市场。

图3:RigorEMIR GUI界面

对于日观芯设于本届DAC中即将展示的一站式数字后端签核工具系列,许多即将参会的业界领袖都表现出了浓厚的兴趣。他们期待这些新产品能带来更高性能的设计验证,为未来的创新打开更广阔的可能性。

在此,日观芯设将热忱得欢迎您在DAC 展会期间参观日观芯设的展台(展位号:1552),亲自体验我们的一站式数字后端签核工具系列。我们将现场答疑和研讨,与业界专家和客户分享我们的最新成果和见解。

最后,希望在此次DAC展会上,能和客户以及业界专家进行深度交流和学习,同时也为日观带来了新的合作机会和可能性,与更多的伙伴共享资源、共赢市场。

责任编辑:Ace

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 复杂SoC芯片设计中有哪些挑战?

- 2 进迭时空完成A+轮数亿元融资 加速RISC-V AI CPU产品迭代

- 3 探索智慧实践,洞见AI未来!星宸科技2024开发者大会暨产品发布会成功举办

- 4 重磅发布:日观芯设IC设计全流程管理软件RigorFlow 2.0