破局带宽瓶颈,光纤PCIe引领数据中心互联新时代

2024-09-20

15:51:58

来源: 互联网

点击

AI和机器学习技术的迅猛发展,尤其是大语言模型(LLM)的兴起,对计算资源和数据传输速度提出了更高的要求,从而激发了对更高带宽解决方案的迫切需求。过去数年,PCIe作为数据中心服务器间互联的主力军,承担着高速数据传输的重任。而今,PCIe Gen 7.0标准即将发布,其在数据中心中的地位也将进一步得到巩固。

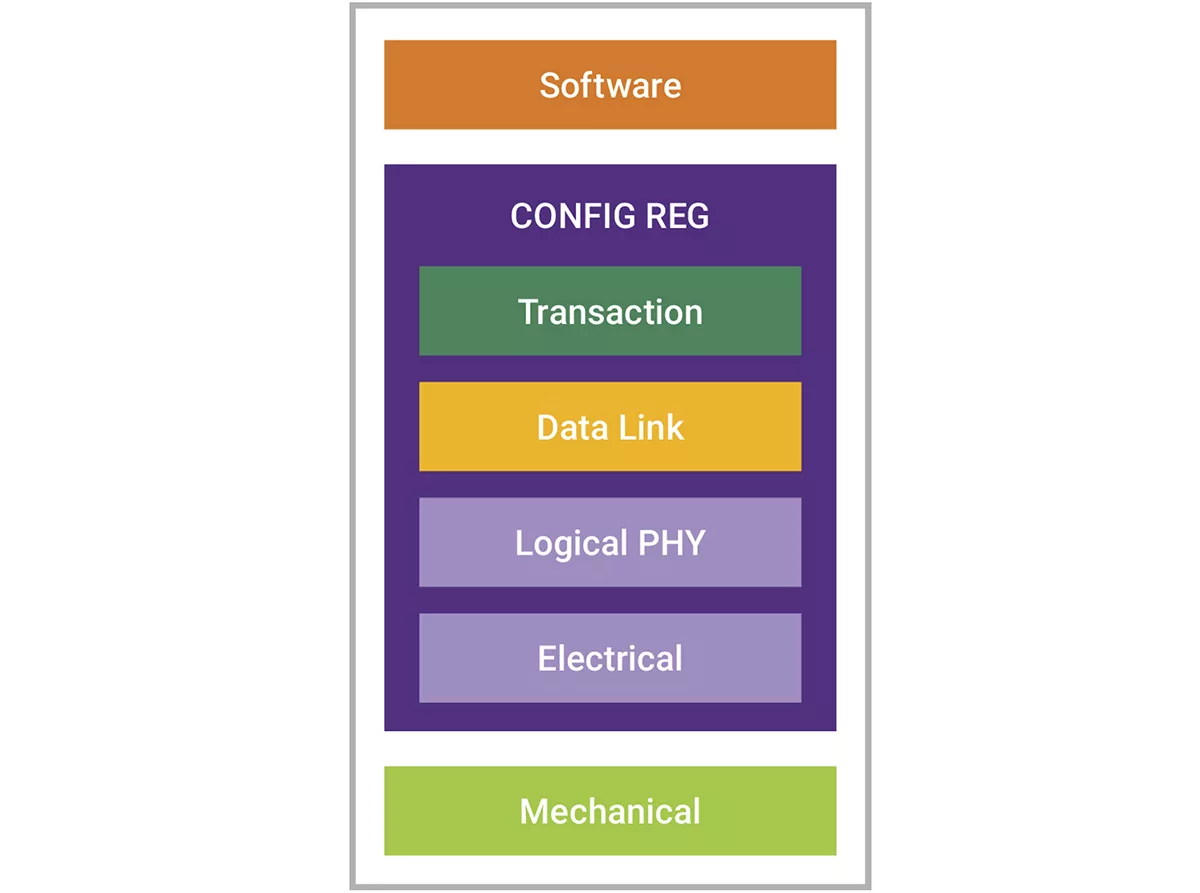

图 1:PCIe 链路上的数据通信全栈。

PCIe链路通过铜缆或背板将服务器内的各种资源连接起来,实现高速数据交换。

然而,面对不断增长的带宽需求,传统的PCIe架构也面临着新的挑战,例如资源限制、延迟和能耗等。而光纤链路因具备高带宽、低延迟和长传输距离等优势,有望成为下一代PCIe的创新方向。

数据中心的“四座大山”

面对爆炸式增长的AI工作负载,数据中心正面临四大严峻挑战。

1.资源限制:数据中心中的计算密集型任务,如大语言模型(LLM),对内存带宽和利用率提出了更高要求。当前,大部分数据中心仍依赖本地内存,这不仅限制了数据处理的速度,还导致内存资源的利用效率低下。尽管处理器技术在不断进步,增加了更多更快的内核,但内存带宽的瓶颈依然存在。如何有效提升内存带宽和利用率,成为提升数据处理能力的关键挑战。

2.延迟:延迟问题是很多AI/ML应用的性能提升瓶颈。当前,通过铜缆和背板进行的数据传输需要采用复杂的调制方案和先进的均衡技术(如前向纠错 FEC)来保证数据的完整性。这些技术虽然能够提升传输的可靠性,但同时也增加了系统延迟。这种延迟对需要实时数据处理的应用尤为关键,限制了整体系统的响应速度和处理能力。

3.能耗:数据中心的电力消耗是另一个亟需解决的问题。现有技术的高耗电芯片导致了数据中心大量的电力用于点对点的数据传输。据估计,这部分消耗占到了数据中心总电量的25%。随着AI/ML应用对数据传输需求的激增,这一比例可能进一步上升,增加了数据中心的运营成本和环境负担。降低能耗、提高能效成为提升数据中心可持续性的重要任务。

4.可扩展性:数据中心的扩展能力直接关系到其对新兴应用和技术的适应性。随着数据传输和处理需求的提高,网络架构也要能够根据实际需求进行动态调整资源,以应对不断变化的AI工作负载。

光纤PCIe来解围!

传统的铜缆PCIe 接口主要用于DAC 和 PCB 互连,随着数据速率的提升和电气损耗的加剧,这种方案的优势在减弱。与之相比,光纤链路的带宽密度更高,因此更加适应新的需求。光纤技术也支持让不同的处理单元去访问不同服务器单元或机架中的其他内存单元,从而能够突破内存限制,这有利于通过 CXL 交换机和其他类似应用进行资源集中或共享。

光纤链路在较长距离范围内保持能效和成本效益方面也表现优异。与电气链路相比,它们的损耗要小得多,这意味着它们在相同的距离内使用更少的重定时器和信号调节装置。此外,使用低成本、高良率的光纤元件可以进一步降低单位距离的成本。另一方面,铜缆互连在数据中心占据了很大的空间,不适合密集型数据中心。相比之下,光纤更灵活,占用的空间更小,使其成为提高数据中心密度的更好选择。

最后,线性直接驱动光纤链路也有助于减少延迟和降低功耗。可为光纤传输 PCIe 部署不同的光纤架构,从而改善延迟。

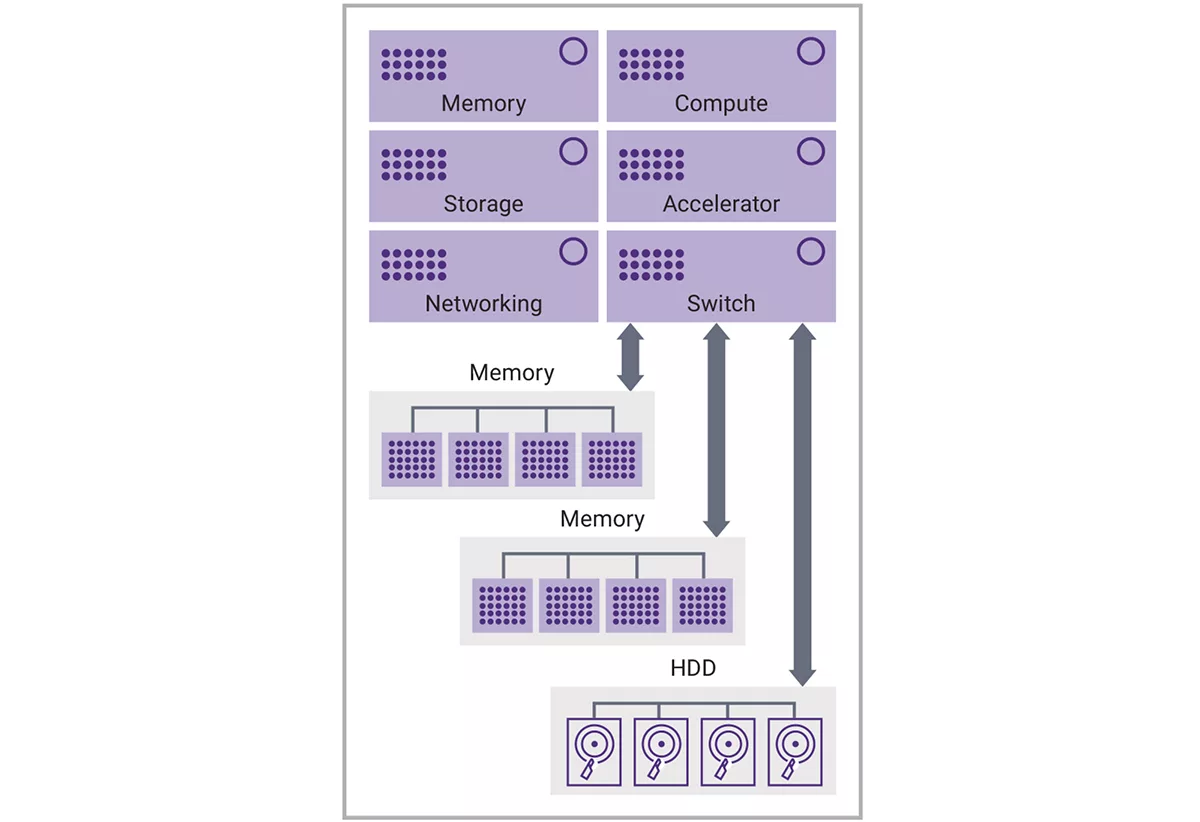

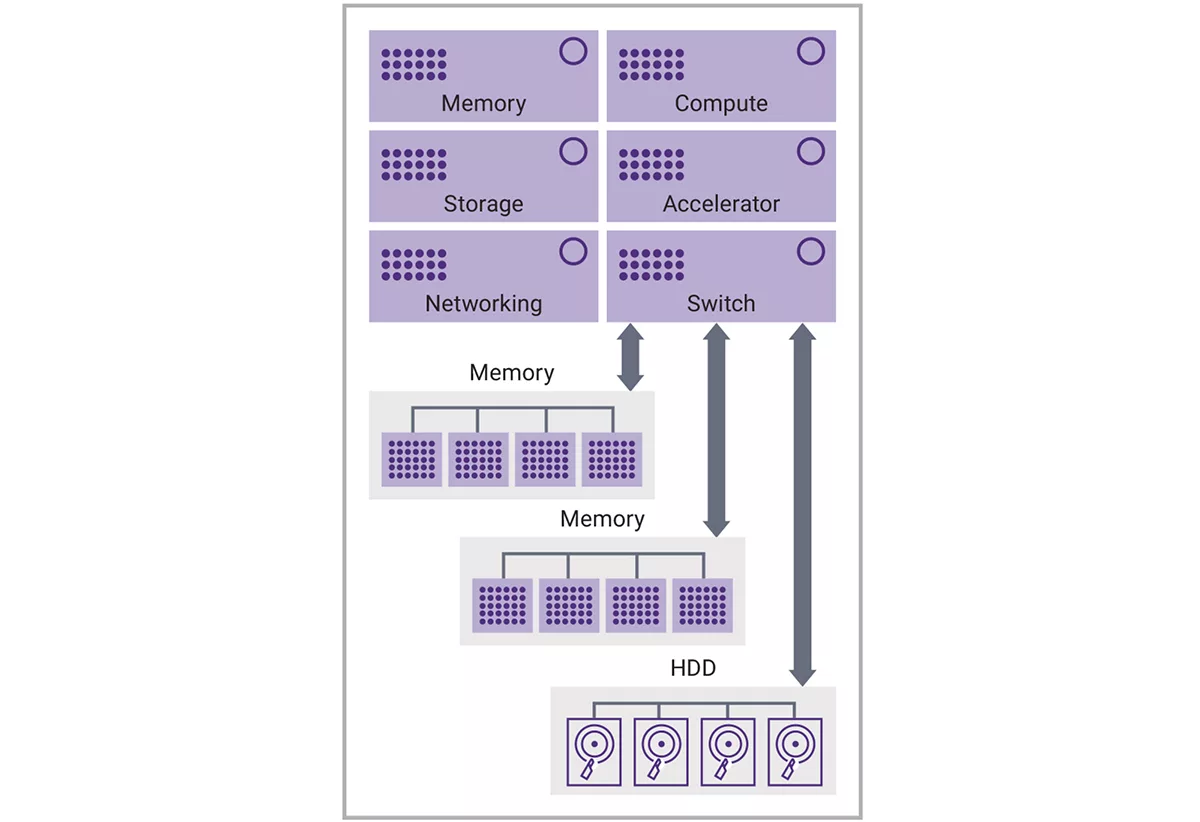

图 2 显示了一个光纤传输PCIe用例场景,用于根据OCP(开放计算项目)要求执行的数据中心机架内和机架间配置。此类应用包括NVMe和CXL支持的离散数据中心的计算、存储、加速器和内存连接场景。

图 2:OCP 通用机架内和机架间 PCIe 连接

实现光纤PCIe,不容易

PCIe接口的最初构思并未考虑光纤的兼容性。PCIe互连的应用(如 CPU 到 CPU、GPU 到 GPU以及GPU到存储器)通常使用当前的PCIe PHY和控制器,通过铜缆通道,从根联合体到端点加以实现。因此,从使用电气通道的PCIe过渡到光纤传输PCIe的过程复杂且充满挑战。

首先,要实现PCIe电气合规需要明确规范以确保互操作性,还需保持与光纤链路的兼容性。其次,光纤传输PCIe协议的支持可能需要对现有协议进行更改,包括Rx检测、电气IDLE状态管理、光纤器件的SSC时钟性能以及边带信号处理等方面。为应对这些挑战,PCI-SIG光纤工作组于2023年8月成立,新思科技也积极参与其中,推动“光纤友好型”PCIe标准的制定。

如何实现光纤传输 PCIe?

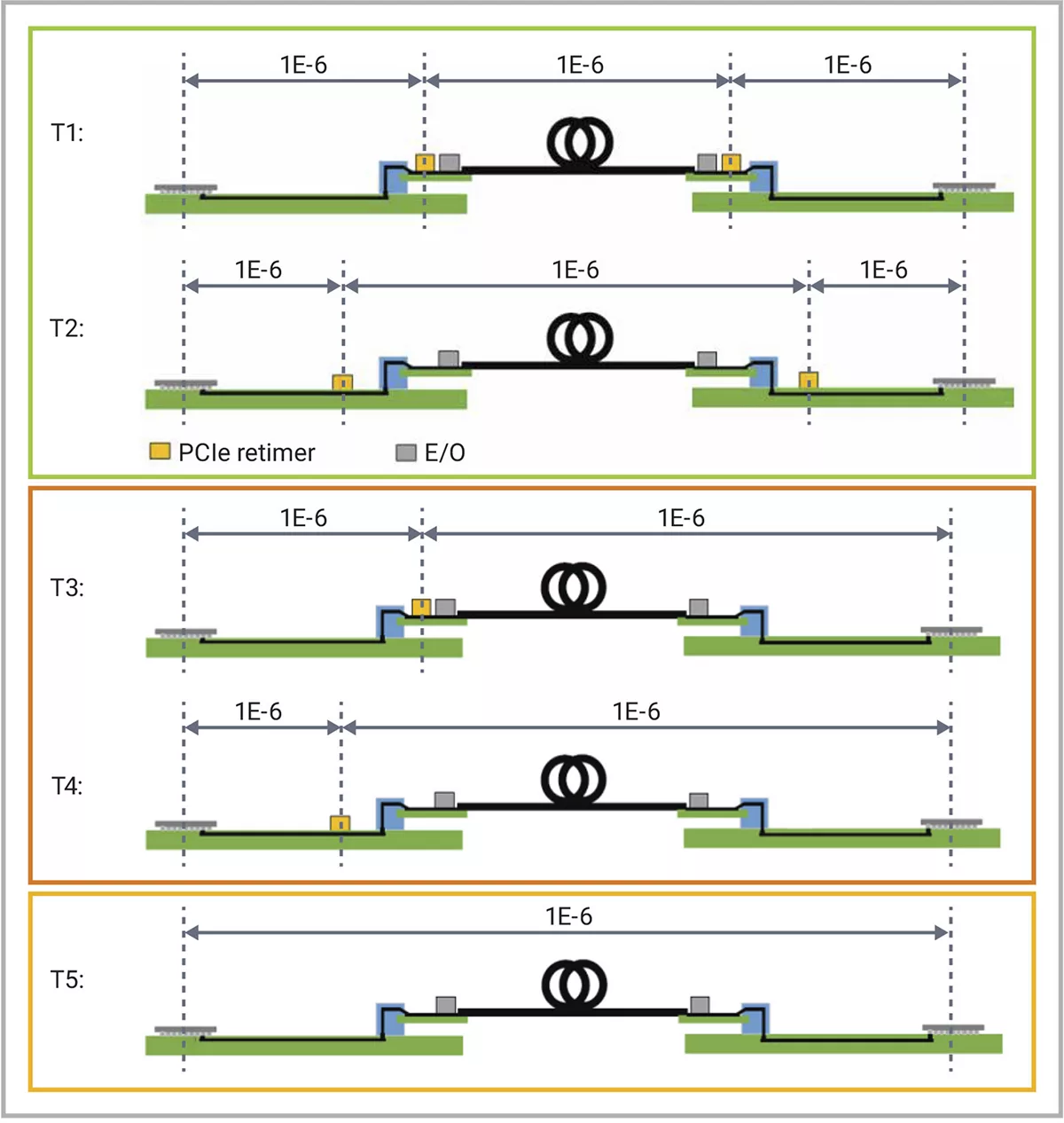

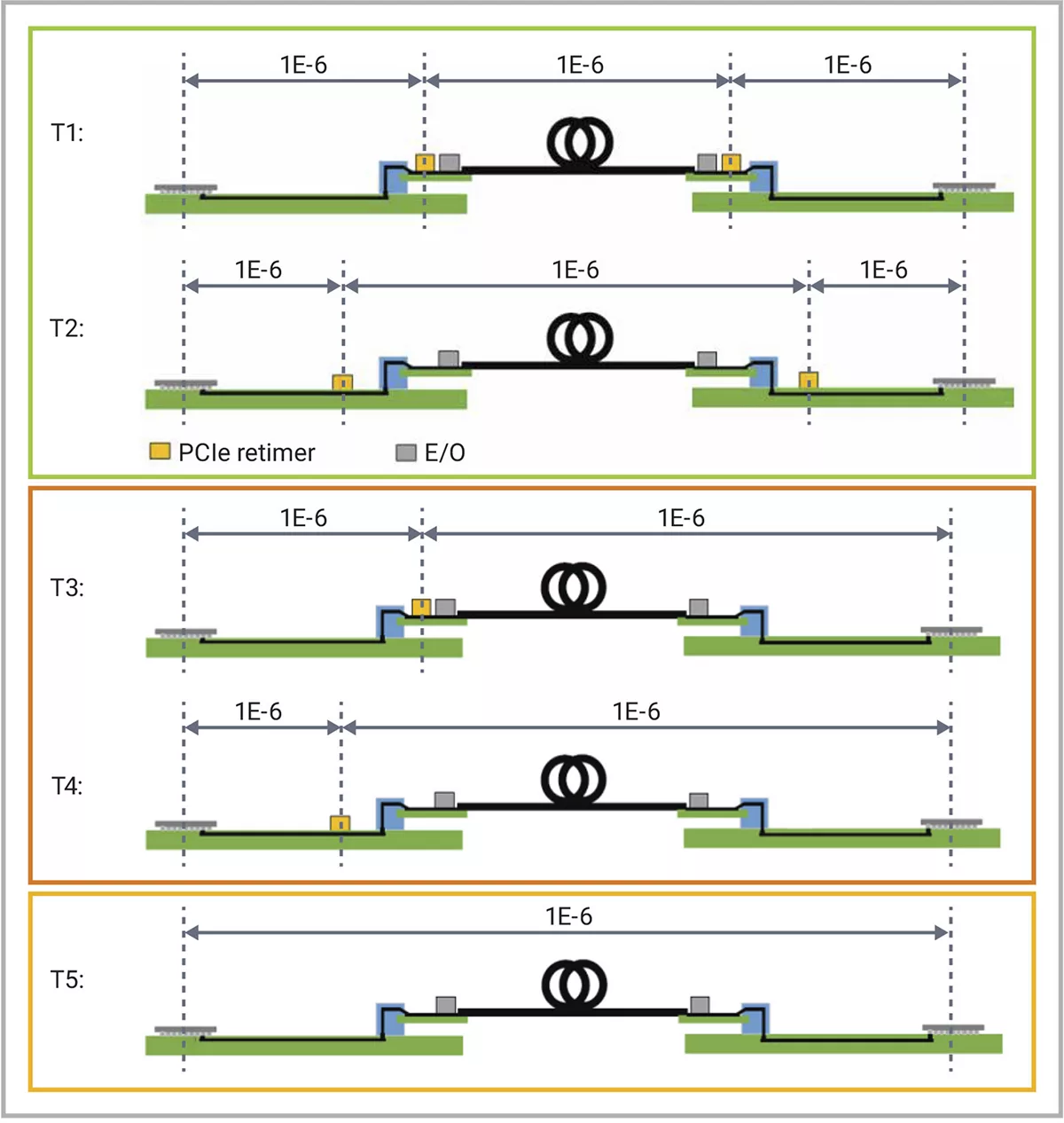

重定时拓扑是一种关键方法,最多可在端到端链路中使用两个重定时器。在此拓扑结构中需要考虑的一些重要方面包括战略布局,以及部署的重定时器的精确数量。

相反,非重定时(即线性)拓扑引入了一组更复杂的挑战。这主要是因为线性链路破坏了路径的连续性,使得更难以遵循现有的 PCIe 标准和合规性规定。在此拓扑中,有效调节通道损耗至关重要。此外,还需要对协议层进行重大改变,并且可能还需要对 PHY 层进行重大改变。对所有类型的光纤引擎进行全面的可行性研究,也是该拓扑结构的一个关键方面。

图3:实现光纤传输PCIe的各种拓扑

除了链路拓扑外,还应考虑其他关键元素,如外形标准化和 FEC 方案,以便通过光纤成功建立 PCIe 链路。目前正在评估 CDFP、OSFP、QSFP、QSFPDD 等形状,仔细考虑每个形状的优缺点。FEC 讨论中也发生了同样的情况,正在考虑采用级联 FEC 架构部分满足光纤 PMD 要求或扩展其范围,同时为整个系统提供低延迟。

全球首款光纤传输 PCIe 7.0

光纤传输PCIe是实现机架单元互联并使其作为集群运行的关键。PCIe作为控制器,连接数字逻辑和特定软件。主要挑战在于确保向光纤PCIe的过渡不干扰软件堆栈的控制过程,以及物理层的管理和电气-光纤接口的互操作性。

在这方面,新思科技与OpenLight 合作,提供可与光纤 IP 配合使用的电气 IP 解决方案。一旦建立通用标准,任何光晶粒供应商都将能够集成 PCIe。

新思科技和OpenLight在OFC 2024期间展示了全球首款采用线性驱动方法的光纤传输 PCIe 7.0 数据速率演示版本,此外,还展示了光纤传输 PCIe 6.x 演示版本。该演示版本展示了端到端链路 BER 性能比 FEC 阈值高出几个数量级,表明采用光纤传输 PCIe 7.0 的可行性优于采用 128Gbps PAM4 传输。这样的性能是通过使用离散电气和光纤组件构建光纤传输 PCIe 链路达到的。正如 OFC24 期间展示的那样,驱动具有卓越 PPA 和延迟的电气 PCIe 链路的 新思科技 SerDes 依然不受这种不理想甚至最差情况用例场景的限制,展示了新思科技SerDes的灵活性和稳定性。

总结

在AI/ML及其带来的带宽需求时代,光纤传输PCIe代表了信号传输的未来趋势。其开发和采用依赖于支持性生态系统的建设,新思科技正在积极推进,利用其完整的PCIe IP解决方案,通过PCIe 7.0和PCIe 6.x互操作性演示和成功的现场成绩,减少集成风险并实现首次流片成功。

责任编辑:Ace

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 东方晶源YieldBook 3.0 “BUFF叠满” DMS+YMS+MMS三大系统赋能集成电路良率管理

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 智能驾驶拐点将至,地平线:向上捅破天,向下扎深根