隼瞻科技 elexcon2024 深圳国际电子展回顾

2024-08-30

17:11:34

来源: 隼瞻科技

320点击

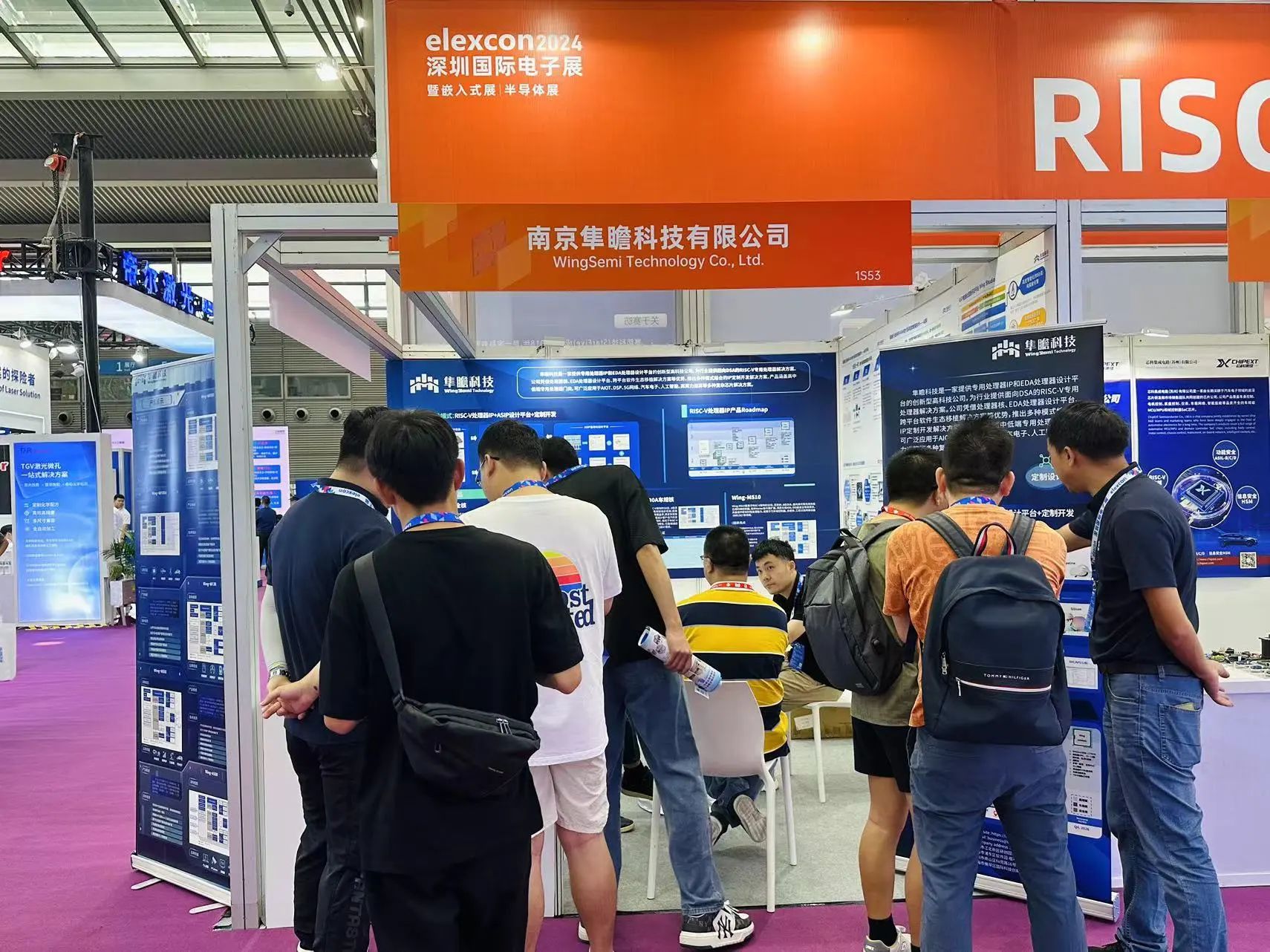

8月29日,为期三天的elexcon2024深圳国际电子展在深圳会展中心(福田)圆满落幕。展会不仅汇集了世界各地的领先企业和行业专家,同时也是促进新技术、新产品和新理念交流与碰撞的平台。隼瞻科技携四款明星产品——安全核Wing-M050S与Wing-M130S、车规核Wing-M130A、及高可靠性、高实时性处理器Wing-M510亮相本次展会。隼瞻科技创始人兼CEO曾轶先生受邀参加RISC-V与AIOT分论坛,围绕“基于RISC-V面向应用的专用处理器解决方案”发表相关主题演讲。与此同时,隼瞻科技凭借其技术与产品上的独特优势,备受行业权威媒体的认可,荣获“年度市场创新突破奖”。

展台&明星展品

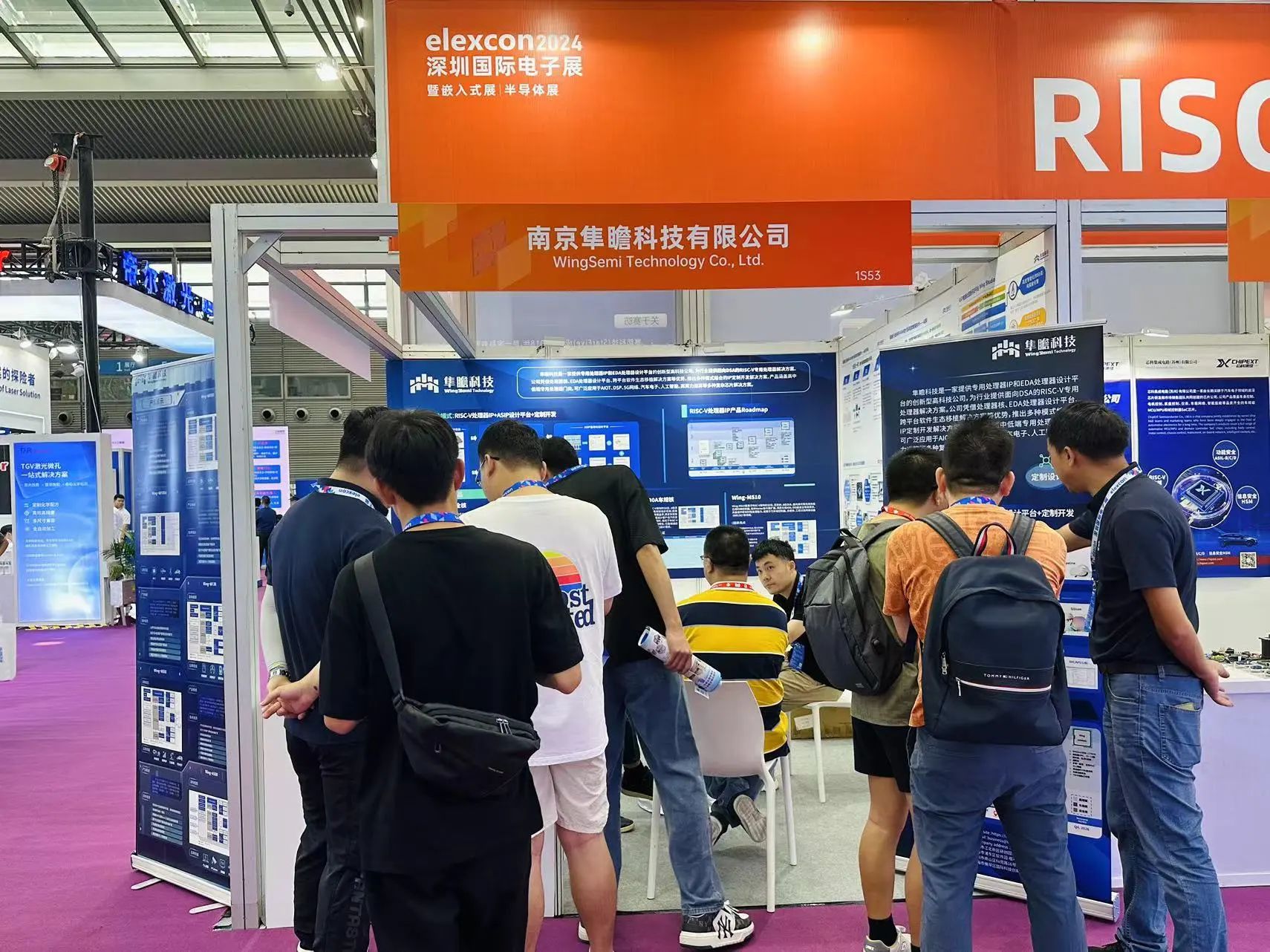

展会现场人头攒动

展会现场人头攒动

Safety Goal Violations

Safety Goal Violations

请跟随我们一起走近elexcon2024隼瞻科技!

展台&明星展品

展会现场人头攒动

展会现场人头攒动安全核——Wing-M050S & Wing-M130S

Wing-M050S与Wing-M130S是两款专为物理安全、信息安全设计的超低功耗嵌入式RISC-V处理器IP,可以对标ARM Secure CPU SC000/SC300。其兼顾低功耗、高性能、及丰富安全特性,不仅能满足企业对安全性的严格要求,同时能协助芯片厂商快速、低成本地把产品推向市场,为物联网、移动支付,多媒体以及移动存储等众多领域发展提供源源不断的安全动力。

安全特性示意图

安全特性示意图

Wing-M050S与Wing-M130S拥有随机指令、随机执行周期、寄存器保护、物理内存保护、跳转保护等多种安全特性,能够有效抵御侧信道攻击、故障注入攻击、代码篡改攻击、控制流攻击等,为客户产品的高安全性、高可靠性保驾护航。

安全特性示意图

安全特性示意图Wing-M050S与Wing-M130S拥有随机指令、随机执行周期、寄存器保护、物理内存保护、跳转保护等多种安全特性,能够有效抵御侧信道攻击、故障注入攻击、代码篡改攻击、控制流攻击等,为客户产品的高安全性、高可靠性保驾护航。

车规核——Wing-130A

Wing-M130A是基于RISC-V架构的32位、3级流水线的的微控制器。其采用双核锁步机制,提高单点故障覆盖率和潜在故障覆盖率,已获车规ISO26262 ASIL-D认证。该产品能够显著减少客户在汽车安全标准认证上的时间成本。同时,依托于RISC-V架构的模块化和高度可定制的特性,它能够适应多样化的车载系统级芯片(SoC)设计需求。

Safety Goal Violations

Safety Goal Violations高可靠性、高实时性处理器——Wing-M510

Wing-M510是基于RISC-V架构的32位、双发射、8级流水,面向高可靠性高性能应用的微控制器,可对标ARM Cortex M7/R5/R52。其支持Vector指令集扩展,满足车规ASIL-D功能安全等级需求,具备强中断实时性处理能力,适用于汽车域控制器,多媒体,工控以及网络设备(Wifi/5G)等领域。其技术亮点包含:

- 领先的处理器架构性能,强大的控制及运算能力,支持RVV指令集扩展

- 基于EDA敏捷开发平台的客制化指令集扩展功能

- 增强代码密度的扩展指令集

- 增强的指令和数据跟踪特性

- 高实时性和低中断延迟- 支持RTOS虚拟化

- 支持多核配置- 高可靠性,满足车规ASIL-D等级要求

- 先进的操作系统与应用迁移技术

Wing-M510演示Demo

Wing-M510演示Demo

- 基于EDA敏捷开发平台的客制化指令集扩展功能

- 增强代码密度的扩展指令集

- 增强的指令和数据跟踪特性

- 高实时性和低中断延迟- 支持RTOS虚拟化

- 支持多核配置- 高可靠性,满足车规ASIL-D等级要求

- 先进的操作系统与应用迁移技术

Wing-M510演示Demo

Wing-M510演示Demo演讲

RISC-V架构因其开源、可定制等特性,在处理器领域日益受到重视。但传统SoC架构面临存算墙问题、编译架构紊乱、灵活性差等诸多问题,这大大限制了RISC-V处理器在更多元、更高端应用场景的想象。为了解决该行业痛点,隼瞻科技将目光聚焦在了DSA(垂直领域架构)上。据曾轶介绍,DSA技术拥有三大核心优势:1. 拥有针对AI算法扩展指令集,即不用再向ARM采购CPU和Tensilica采购DSP,自己即可实现专用AI算法的指令集定制;2. 灵活可编程,完备AI指令集和编译器,达到AI编译体系的高度统一;3. PPA大幅优化,显著降低成本、面积、功耗,大幅提升垂直场景处理器性能。兼具灵活、可扩展的通用性与特定场景的专用性,使DSA技术具备广泛的下游应用场景,如:音频、图像、通信、AI、高性能计算等。与此同时,曾轶还预告了DSA敏捷开发平台Wing Studio将于2024年Q4正式发布!

演讲现场

演讲现场

演讲现场

演讲现场曾轶还提到了另一大行业痛点——代码密度问题,“相比成熟的Arm 架构,代码密度并非 RISC-V 传统强项。在 ArmCC 等商业编译器的加持影响下,某些应用场景中两者代码密度差距甚至达一倍之大,这直接影响到面积、功耗和整体成本”。

针对以上痛点,隼瞻追根溯源,推出了全新的“四位一体”代码密度增强技术方案。通过社区标准优化、Xwingc 扩展指令集、WingGCC 编译器、WingLib基础库等四项手段,一步步有效提高代码密度优化,且获得了显著效果。根据客户反馈,在同样的业务代码下,隼瞻科技产品的代码规模仅有ARM同级产品代码规模的89%,显著降低了客户芯片片上内存面积!

隼瞻科技创始人兼CEO:曾轶

隼瞻科技创始人兼CEO:曾轶

隼瞻科技创始人兼CEO:曾轶

隼瞻科技创始人兼CEO:曾轶奖项

为表彰在行业中表现卓越的上游元器件供应厂商,elexcon 2024深圳国际电子展携手电子发烧友网,特设 “2024年度市场卓越表现奖” 五大类别奖项。隼瞻科技拥有强大的研发团队和深厚的设计经验,面向垂直领域推出极致“能效比”和“面效比”的RISC-V 专用处理器解决方案,其中安全核Wing-M050S和Wing-M130S,与车规核Wing-M130A均在头部客户进入量产阶段。同时,隼瞻科技推出开创性的DSA处理器敏捷开发平台Wing Studio,辅以行业领先的代码密度优化技术及中断实时性增强技术。凭借以上独特优势,隼瞻科技备受行业权威媒体的认可,荣获“年度市场创新突破奖”。

左二:隼瞻科技联合创始人兼COO 张开明

左二:隼瞻科技联合创始人兼COO 张开明

左二:隼瞻科技联合创始人兼COO 张开明

左二:隼瞻科技联合创始人兼COO 张开明未来,隼瞻科技将继续秉承其创新与钻研精神,不断推动RISC-V专用处理器技术的发展。同时,公司也将持续优化产品,以满足市场不断变化的需求。此外,隼瞻科技还将积极构建一个健康的行业生态系统,通过与行业内生态上下游领先企业的合作,共同推动RISC-V技术的发展和应用。这种开放的合作模式将不仅加速技术的创新步伐,也会为整个行业带来更多的机遇和可能性。

责任编辑:Sophie

-

- 半导体行业观察

-

- 摩尔芯闻

2025年1月

日

一

二

三

四

五

六

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

最新新闻

热门文章 本日 七天 本月

- 1 全球首款NFC PSSD亮相CES 2025,江波龙创新产品备受业界瞩目

- 2 英特尔发布两款芯片,发力软件定义汽车

- 3 合见工软,完成近10亿元新融资

- 4 ASML的投资者日,透露了哪些行业发展趋势?