【深度好文】一文讲透高速信号完整性分析和测试

2024-12-27

08:38:51

来源: 互联网

点击

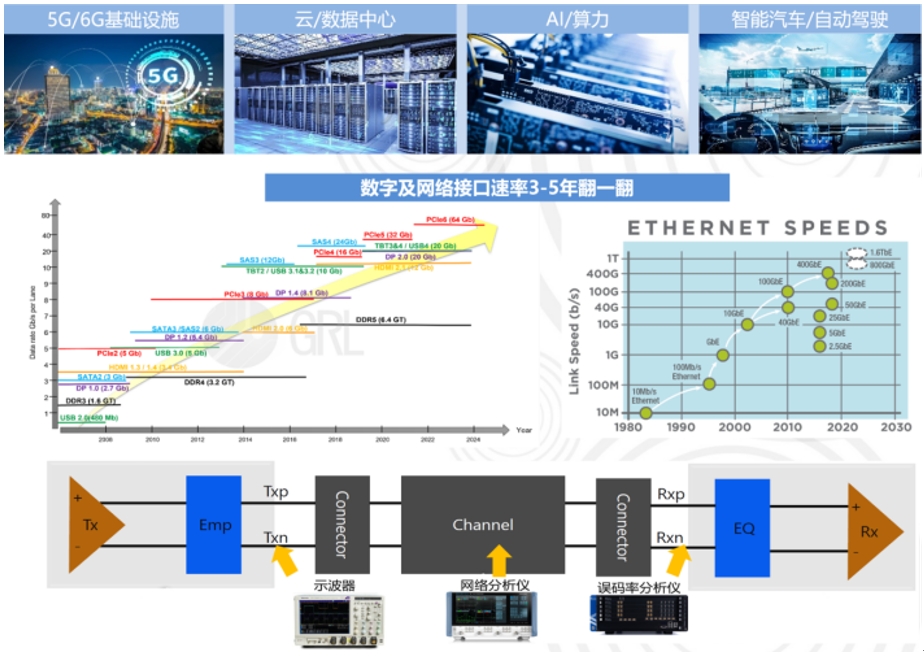

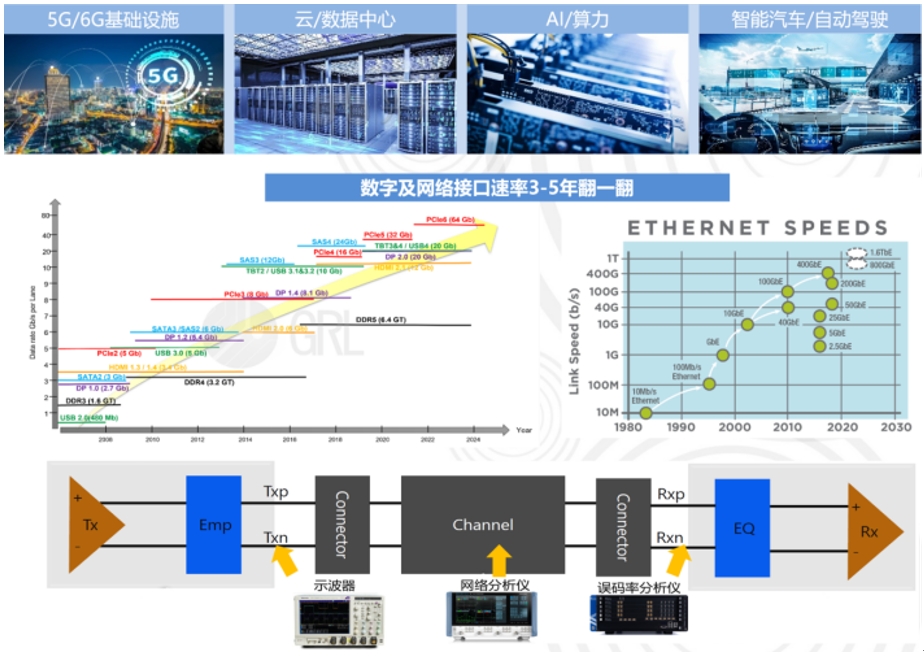

高速IEEE ETH以太网主流速率已经从10G支持到100G、200G、400G、800G以及未来的1.6T,消费电子类的高速总线USB3/4/PCIE6的信号速率已经覆盖了从2.5G到64Gbps的速率范围,高速FPGA的串行高速接口速率则从8Gbps猛增到28Gbps,DSP和ADC/DAC从3Gbps过渡到32Gbps。

随着数字电路工作速度的提高,PCB、连接器、背板上信号的传输速率也越来越高,其中串行数据通信在传输中占据主导地位。按照最严格性能标准制造的拥有精密设计的各种高速互连的PCIE/ETH/VPX背板,以及高速线缆,在当今社会对于高速信号需求普遍存在的大背景下变得至关重要。背板是嵌入式系统中的通信主干,必须按照严格的信号完整性标准进行设计,以确保系统内模块之间及时、准确的数据传输,要满足高速传输的性能预期,信号完整性至关重要。

由于高速串行信号传输速率不断攀升,在电路设计过程中,工程师常常遇到诸多棘手问题,诸如:系统不稳定、间歇性的死机、不同产品兼容性差以及经常出现误码等,而这些现象多半是信号完整性的问题。依照信号传输的完整流程,分别针对 TX 端(发送端)、传输链路以及 RX 端(接收端)进行测试,便能够精准地定位问题根源,从而为后续的优化改进工作提供有力依据,确保高速传输系统的高效稳定运行。

什么是信号完整性?

信号完整性(Signal Integrity,简称SI)是指信号在线路传输过程中保持质量的能力,其核心要求在于确保信号的完整性、准确性和可靠性。在电子系统设计中,如果信号能够按照既定的时序、持续时间和电压幅度到达接收端,则表明该电路具有良好的信号完整性。良好的信号完整性意味着信号在传输和接收过程中能够维持规定的电平和时序。反之,若信号完整性差,其影响因素诸多。其中主要是电源完整性问题。影响因素包括时序问题、反射、串扰、传输距离、信号衰减、温度变化、信号传输介质、杂散、地弹、振铃等,这些都会对信号完整性造成负担,从而导致系统的稳定性下降、误码率增加、功耗增加和性能下降。因此,在高速电路设计中,确保良好的信号完整性至关重要。

在高速电路设计面临三个严峻的问题:信号完整性SI ,电源完整性PI,电磁干扰EMI。SI的主要任务是保证数字电路各芯片之间信号的准确传递;PI的主要目的是确保各部分电路和芯片的可靠供电和噪声抑制;EMI主要目的是确保PCB电路即不干扰其它设备,也不被其它设备干扰。值得注意的是SI的问题,一半以上是因为电源不好引发的信号质量问题,在EMI问题中,一个重要的影响因素是PDN上的高频噪声尤其是电源/地之间的高频噪声。

如何评估高速信号完整性?

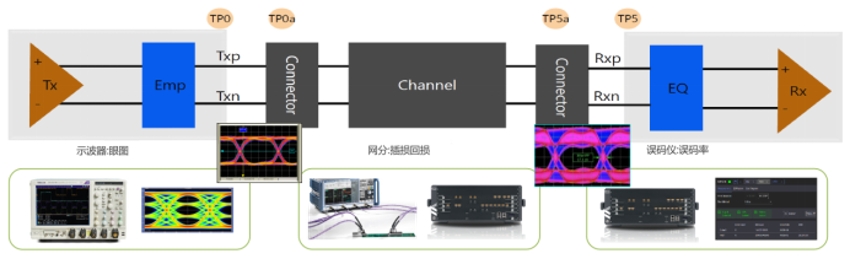

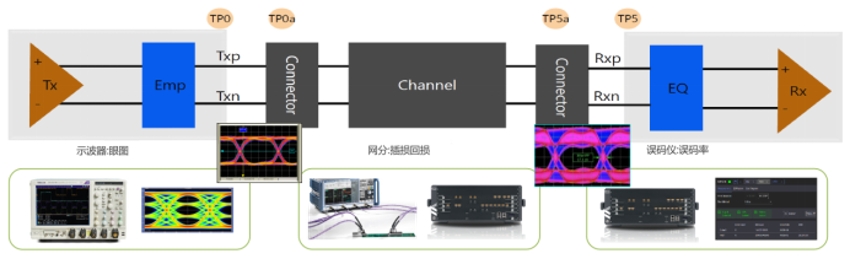

在高速信号传输链路中互连链路上任何一个环节的故障可能影响整个系统工作的效率以及稳定性,对于测试人员需要花费更多的成本去发现问题、定位问题、分析问题、解决问题。新标准逐渐从单一互连简单要求的基础上,额外增加协同整体要求。整个高速链路性能的评估,包括Tx发送端,传输链路,以及Rx接收端三大部分组成,发送、接收、电缆或者背板需要放在一个互连链路中评估。评估时按照时域、频域和其他进行不同仪表的选取。

高速链路信号完整性测试工具

其中TX发送端经常用示波器进行波形完整性、时序完整性、电源完整性、抖动/眼图等测试。

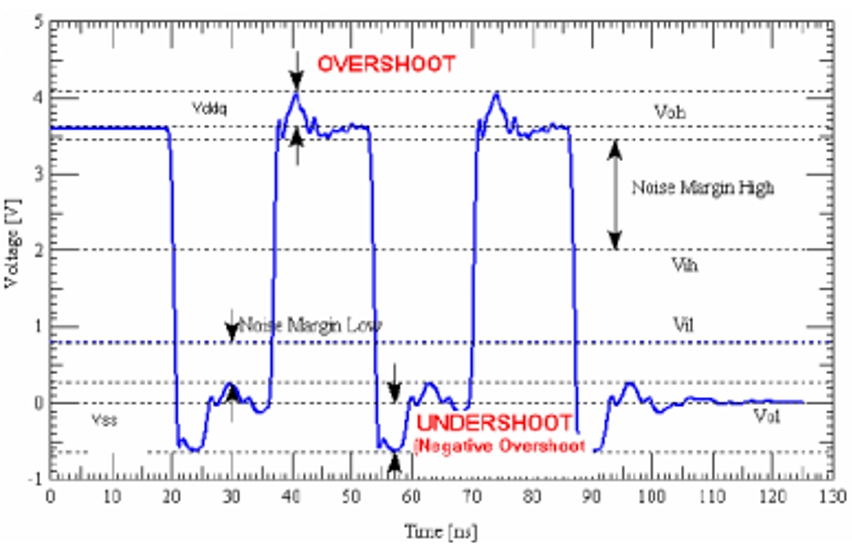

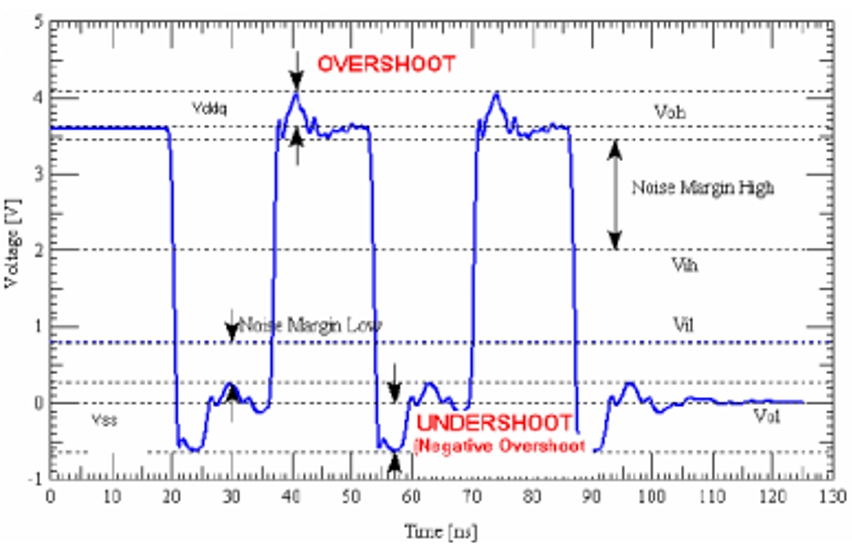

波形完整性:

主要关注波形的单调性(monotonic)、过冲(overshoot,undershoot)、振铃(ringing)、衰减。

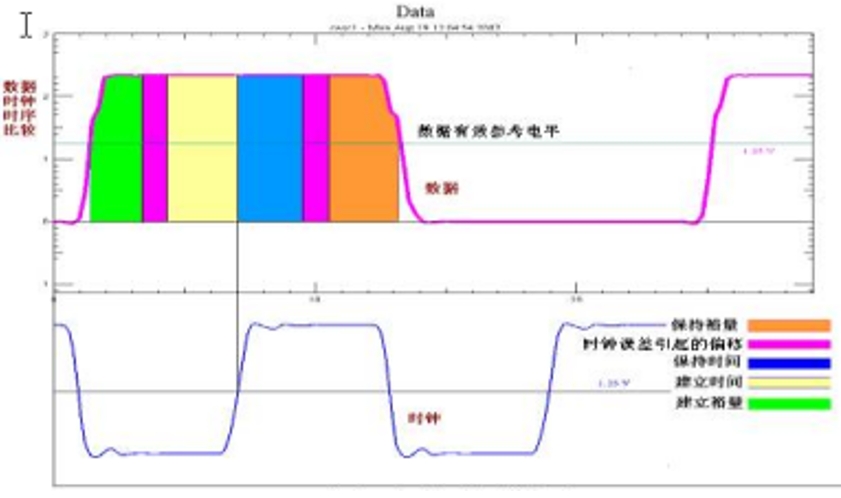

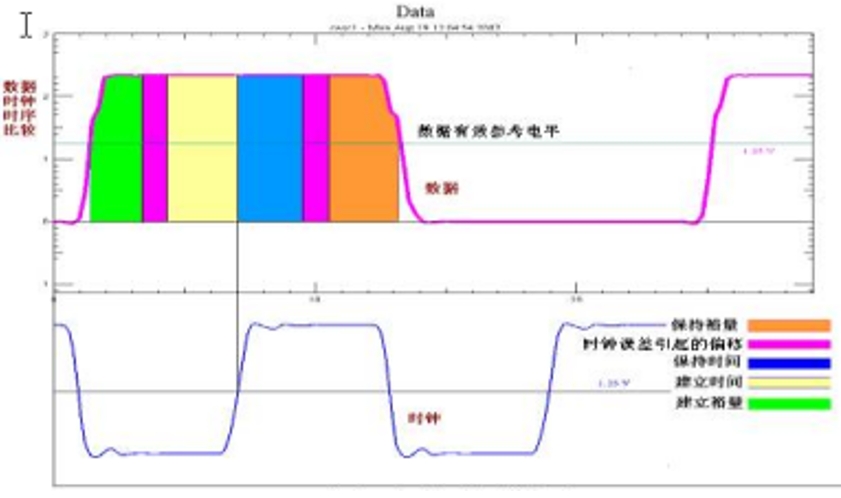

时序完整性:

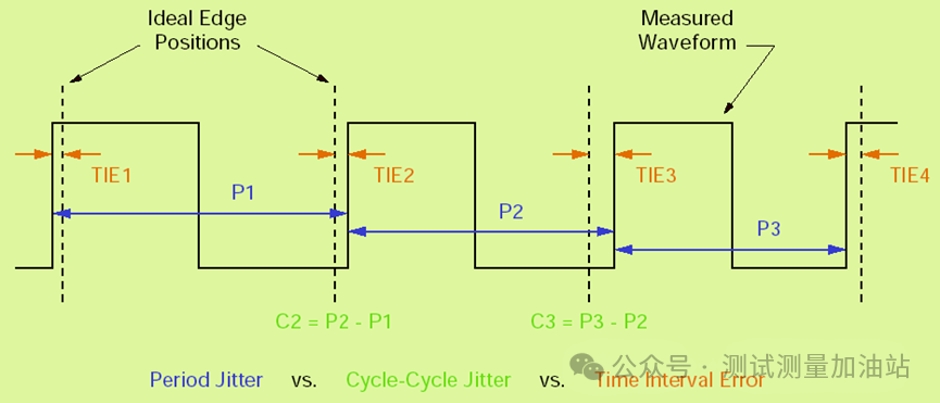

主要关注建立保持时间(setup/hold time)、时序抖动(timing jitter)、skew、毛刺等。

电源完整性:

简称PI,是单板电源设计的一项技术,通过合理的电源平面和滤波设计,为单板上的器件提供稳定/洁净的电源供电,保证单板稳定工作,所以纹波测试为电源测试的必测项,PI和SI是相互影响的。PI包括电源系统设计、直流压降分析、电压瞬态分析、同步开关噪声以及器件建模等。

抖动/眼图:

损耗、反射、串扰三大信号完整性的杀手给信号传输带来巨大影响,会使信号的抖动变大,眼图变差,干扰时钟恢复,降低系统性能,进而在接收端带来误码。

在高速串行信号物理层一致性测试中,抖动和眼图已经成为了一个绕不开的话题,它是评估高速信号质量的关键测试。随着串行数据传输系统的信号速率越来越高,电压摆幅不断降低来节约功耗,系统中的抖动占信号区间的比例正变得越来越大。因此,抖动眼图已经成为限制性能的一个重要因素。随着抖动的增加,系统误码率便会越大。

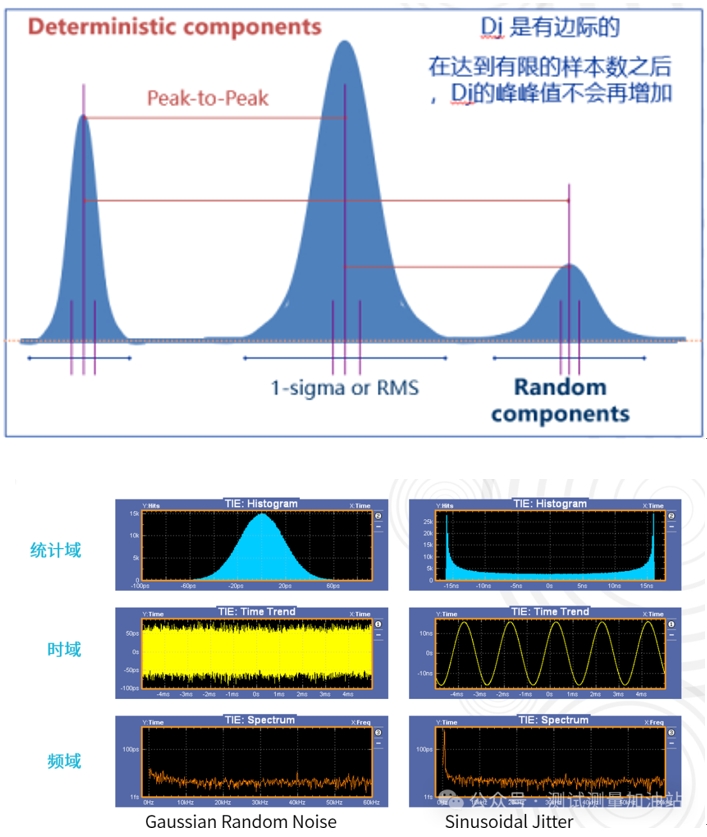

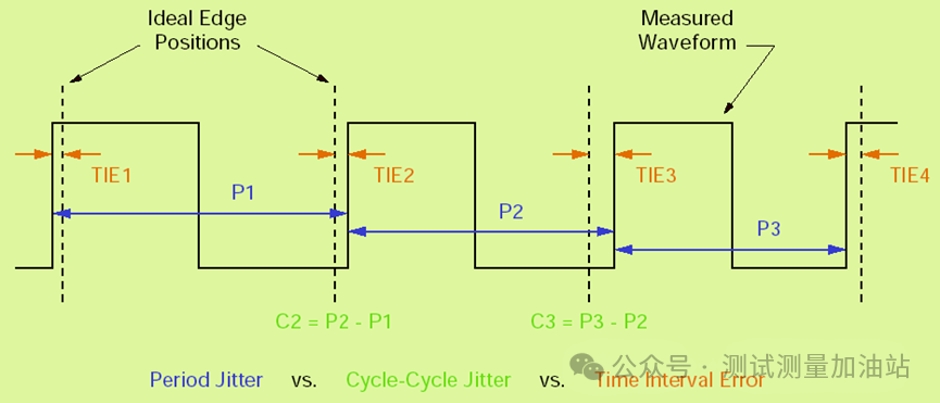

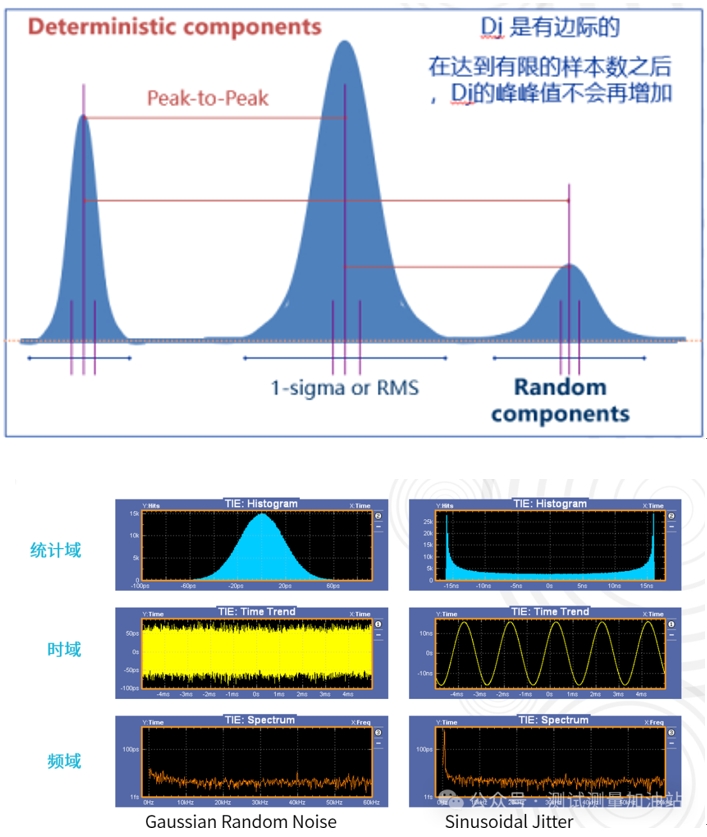

抖动又可以按照成因分为:TJ、RJ、DJ。DJ中又可细分为PJ、DCD、ISI/DDJ。

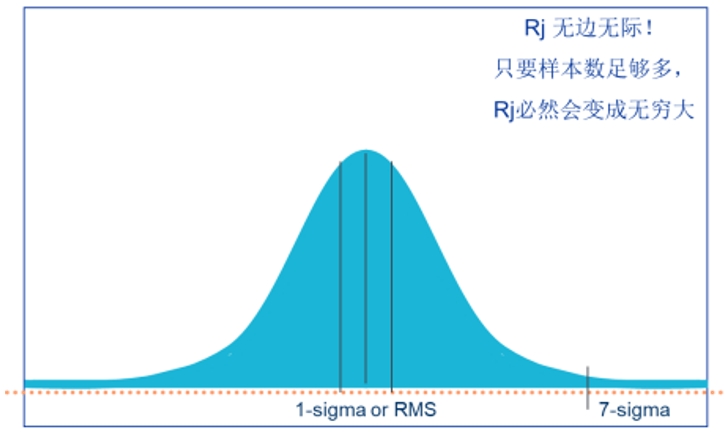

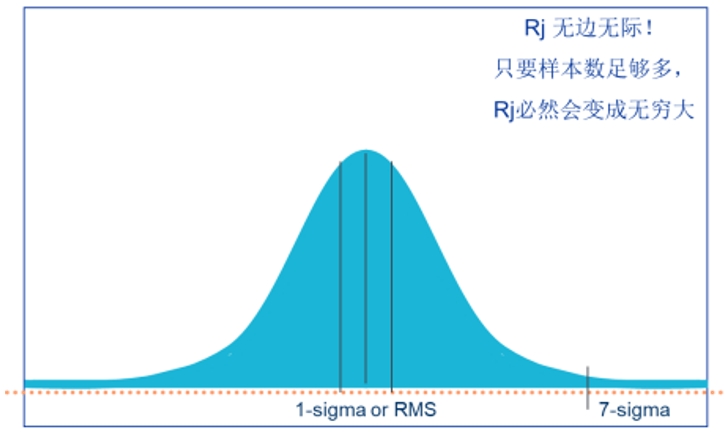

其中Random Jitter(随机抖动)的统计分布是正态高斯分布,是无界抖动,随着样本量的增加RJ会一直增加。

然而Deterministic Jitter (确定性抖动)是有界抖动,在达到有限样本数之后,DJ的peak-peak值不会再增加。

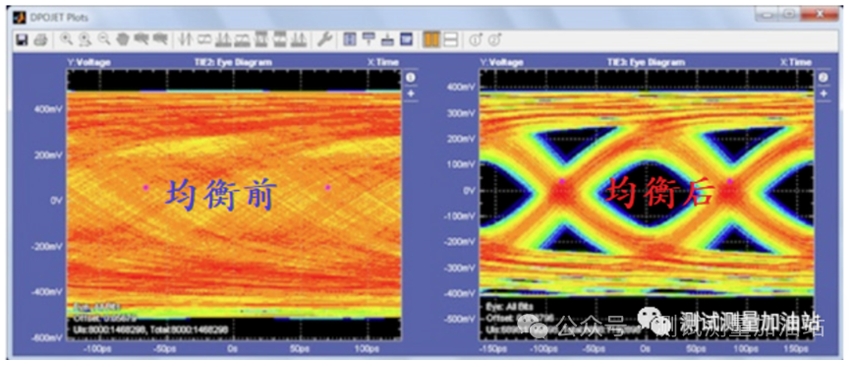

上述抖动在测试中经常用来定位问题信号完整性问题来源,除此之外,我们通常还需要进行眼图的测试来直观的表述信号质量的好坏。眼图是把连续的比特流按照某一特定的时钟,分割为单独的比特,而后叠加而形成的图形,类似一个张开的眼睛,故得名眼图(Eye-diagram)。眼图是高速串行信号的宏观信号质量的整体体现,在眼图中可以直接反映出串行信号的幅度、抖动特性等。

评估一个眼图的好和坏,通常利用一些常见的指标来衡量,比如眼高,眼宽,抖动,占空比等。为了简单而又直观地判断眼图的指标是否符合规范的要求,眼图模板测试是一种评估高速串行信号质量的手段,将规范指标的要求编写成一个眼图模板,然后利用示波器来调用这个模板,这样就可以直观看到眼图是否有碰到模板。如果眼图没有碰到模板区域,表示眼图符合规范要求,结果是Pass;同样如果有碰到模板区域,结果是Fail,需要工程师对电路进行整改,改进信号质量到Pass。

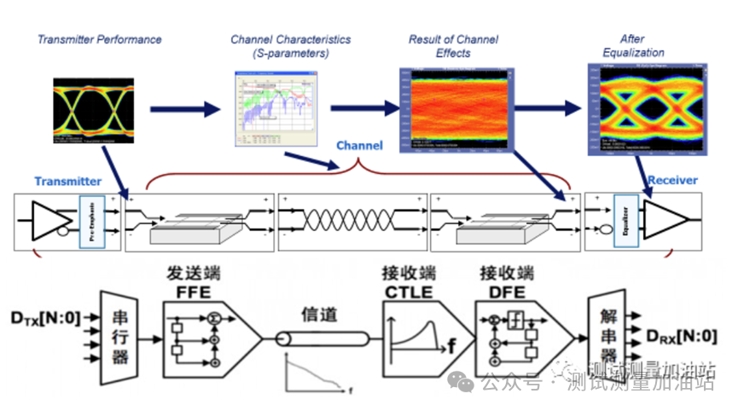

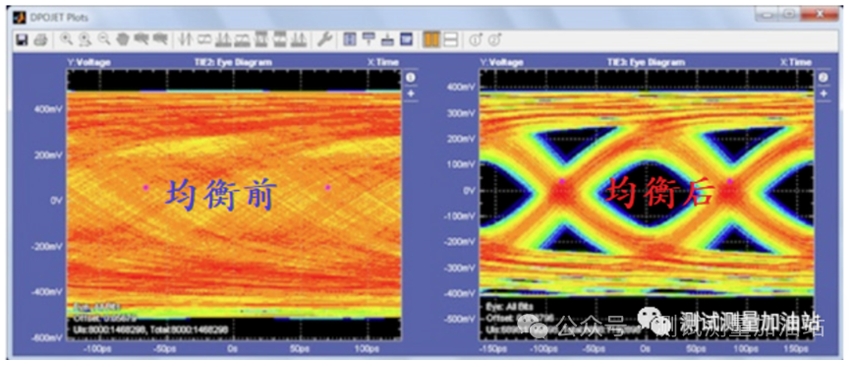

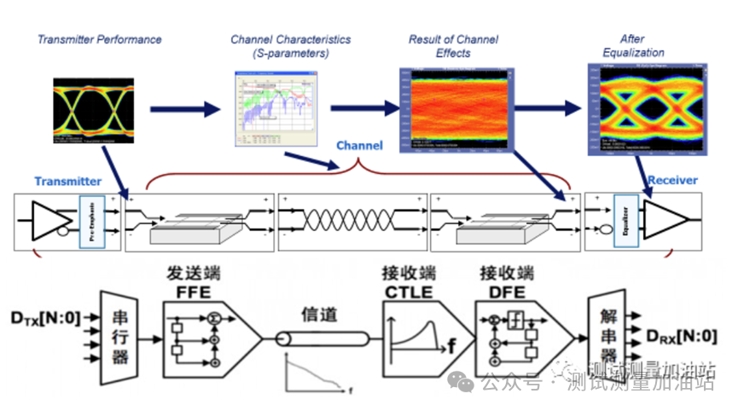

均衡技术:

随着高速串行信号的数据速率的越来越高,如PCIE6.0的数据速率已经达到64GT/s,USB4.0 V2的信号速率已经达到80Gb/s。高速信号的趋肤效应和传输线的介质损耗,当信号经过传输链路时,由于信道损耗、阻抗不连续、以及其它信道的干扰等,信号完整性会变差,信噪比也降低,导致接收端的信号抖动变大,眼图闭合,系统可能出现误码。为了改善接收端信号质量,在接收端能得到比较好的眼图。通常会在发送端做FFE均衡和接收端做均衡来完成信号进行补偿,常用的均衡技术有发送端的预加重和去加重以及接收端的CTLE均衡和DFE均衡。

均衡技术是通过均衡器(Equalizer)均衡信道的衰减、均衡数据的码间干扰。均衡技术以前在通信领域使用,随着高速串行信号的传输速率越来越高,均衡技术的使用场合越来越广,比如现在的PCIE、USB、HDMI、DDR、DP、TBT等高速信号中都使用了均衡的技术。使用了均衡技术后,补偿数据的高频损耗,使信号的高频成分与低频成分基本均衡,从而降低高速信号的码间干扰.

其中TX端的预加重和去加重的目的都是尽量平衡高频分量和低频分量,减少传输链路对高频分量衰减大于低频分量衰减。预加重技术就是在传输线的始端增强信号的高频分量,以补偿高频分量在传输链路中较大的衰减。去加重则是降低低频分量的始端信号。

其中RX端最常用的均衡包括FFE、CTLE、DFE。

· FFE实质是使用数字线性高通滤波器提高信号的高频分量,实现信道的补偿, FFE是SerDes系统常用的均衡。为了缓解接收端均衡的压力,通常SerDes的发送端会采用FFE均衡技术对信号进行预均衡。

· CTLE是直接通过线性模拟高通滤波器拟合信道的衰减,实现信道的补偿。信道的频率响应可以看做是一个低通滤波器,因此将信道和一个高通滤波器串联就能得到一个全通的滤波器。

· DFE为判决反馈均衡,就是将判决后的信号反馈到输入信号上。与FFE类似,DFE也是通过数字高频滤波器实现的,DFE可以只放大高频信号,而不放大高频噪声。

高速传输链路评估

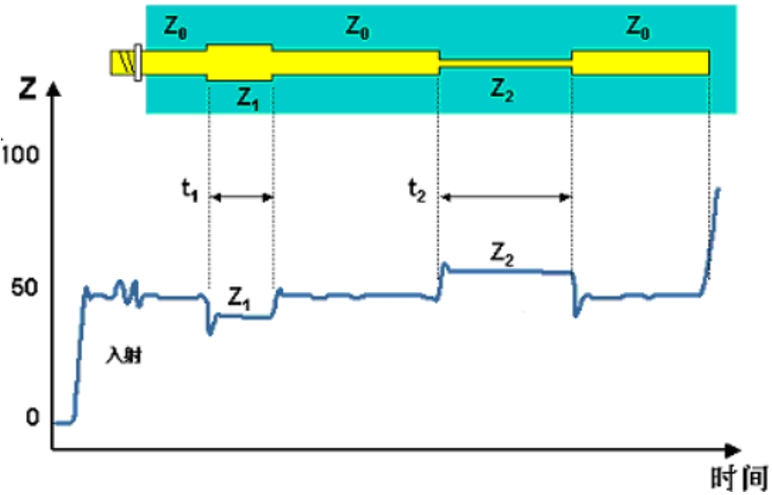

随着信号数据速率的越来越高,信号的上升时间也越来越快,阻抗不匹配和偏差可能会导致反射,当快上升沿的信号在电路板上遇到阻抗不连续的位置就会产生很大的反射,会降低信号质量,影响信号完整性。因此走线阻抗是影响高速信号完整性的一个非常关键的因素。

如何验证测试电缆、连接器、PCB板、背板中差分和单端阻抗是否达到设计要求,成为生产商以及高速数字电路设计人员必须关注的问题。对于高速电路,很重要的一点是要保证信号传输路径上阻抗的连续性,这样可以避免信号产生大的反射。因此需要测试高速电路板的信号传输路径上阻抗的变化情况,从而可以分析问题原因,更好地定位问题的根源,保证高质量的产品快速进入市场。

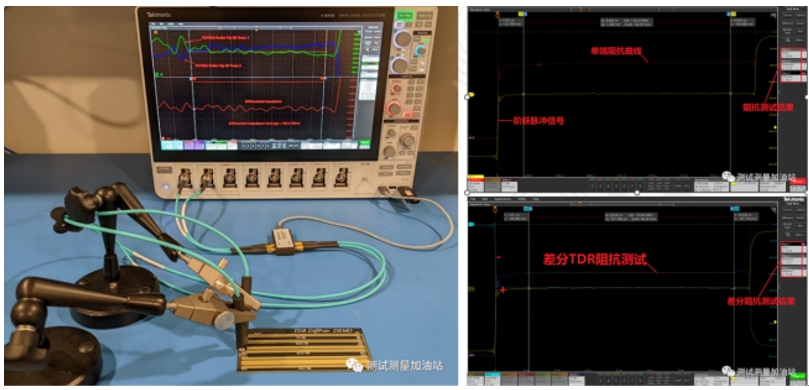

在高速信号电路设计中,经常采用差分传输模式,差分阻抗的测试不同于单端阻抗测试;另外,在高速信号电路中,多个相邻的信号之间会产生串扰。对PCB走线特别是差分走线的阻抗控制提出了更高的要求。如何验证差分阻抗是否达到设计要求成为高速设计的工程师关注的问题。目前验证电缆、连接器、PCB板、背板等传输线特性阻抗的最常用方法是TDR方法。

信号在传输链路路径上传输时会有损耗,反射,串扰的问题,导致信号发生畸变。

· 损耗:传输线的损耗对不同频率是不均匀的,频率越高,损耗越大,上升沿越缓。速率越高,传输线越长,损耗所带来的问题越严重,眼图越容易闭合。

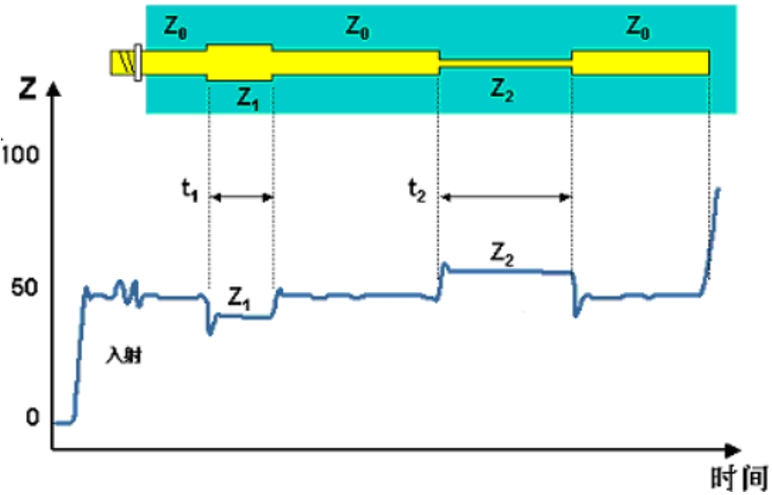

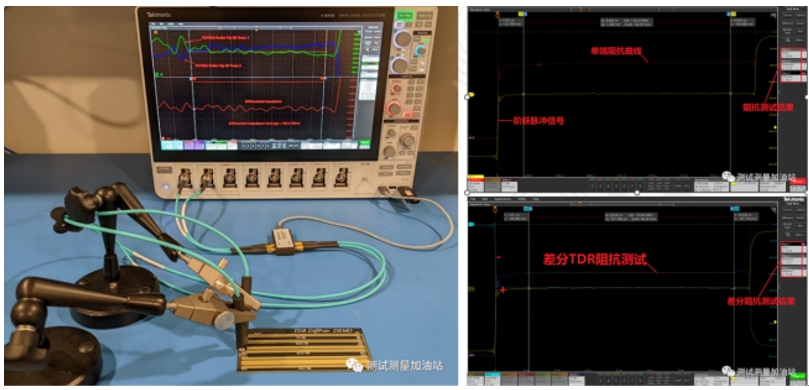

· 反射:传输线上分布电容、电感、和小电阻的存在,会导致传输线的分布式阻抗不均匀,信号流经传输线时部分能量会沿原路反射回去,通常使用TDR来测量传输路径的阻抗变化,如下图:

下面为实时示波器TDR阻抗测试:

信号在传输过程中,对不同速率其损耗不同,反射和串扰都可以导致信号的波形发生 失真,导致眼图闭合。通常使用矢量网络分析仪VNA进行S参数测试和TDR或VNA进行阻抗测试。

接收端容限测试至关重要。RX接收端是整个高速链路的最终环节,接收端测试由于在芯片内部,在绝大多数场景无法直接观测信号完整性问题。最主流的方式是通过创建最的压力眼来模拟真实世界最苛刻的运行环境。误码仪是构建和校准压力眼的核心测试仪器。对于一个高速传输链路,接收端需要在最严苛的环境中保证可靠的接收传输的数据。发送端和链路上的各种信号完整性问题都会恶化信号,减小接收机的余量。接收端测试需要误码分析仪注入多种不同类型的抖动和噪声等压力信号,模拟严苛复杂的真实环境,来完成RX接收端的抖动容限和噪声容限测试。误码仪是进行高速SerDes芯片接收端测试必备仪器。

测试原理:

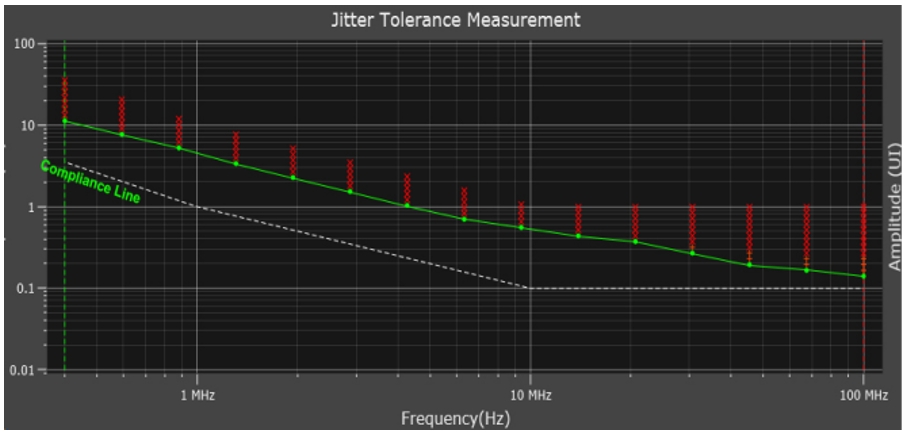

使用测试仪表产生一个劣化(注入抖动)的眼图信号,俗称压力眼信号。压力眼信号的参数有明确规定,,在不同的规范中具体指标会有不同。通过校准后的压力眼会输入被测接收机进行抖动容限测试。中星联华SL3000B系列高性能误码仪可提供PJ、RJ、BUJ等抖动注入,可以为RX JTOL测试提供强力支持。

测试流程:

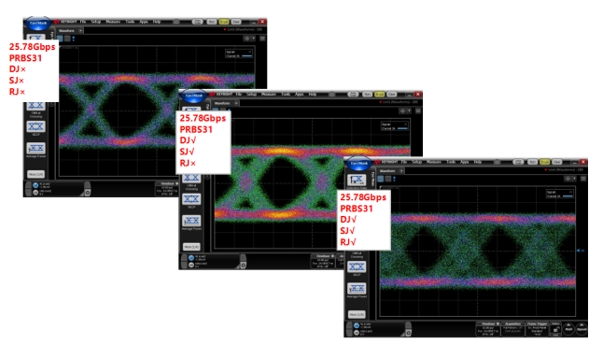

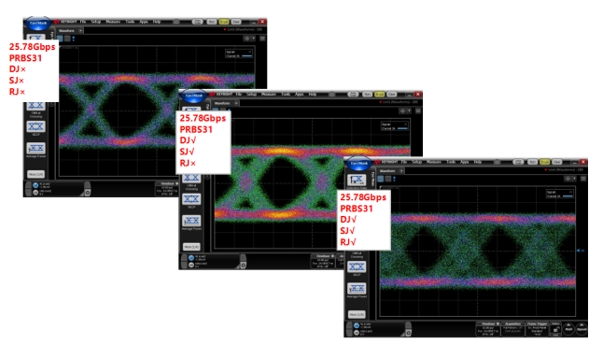

注入抖动眼图:

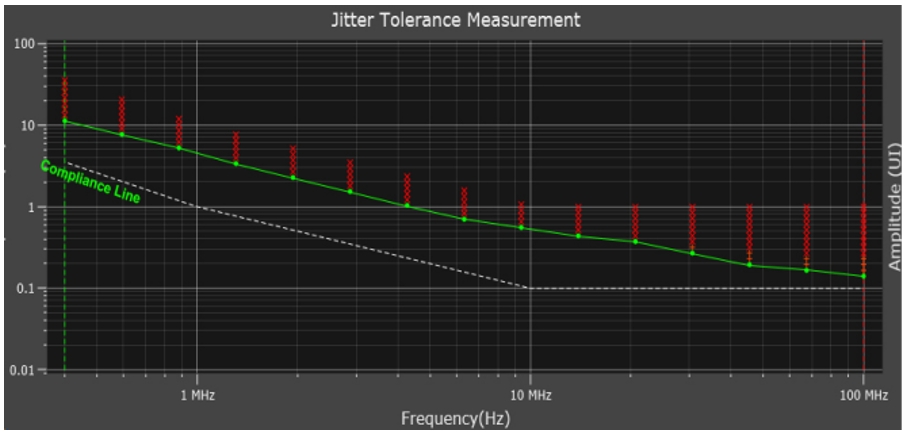

测试结果图:

目前,中星联华的高性能误码仪是国内首个支持注入抖动和加噪声创建压力信号的高性能误码仪,也是目前国内首款能够满足接收端抖动容限JTOL和噪声容限ITOL测试的误码仪。其中可支持的注入抖动类型有低频正弦抖动、高频周期抖动、BUJ串扰抖动、RJ随机抖动以及SSC扩频时钟等;支持的噪声类型有CMI和DMI和BBN宽带白噪声,有效地解决“卡脖子”的难题。

RX接收端测试利器——中星联华高性能误码仪

产品特色:

中星联华高性能误码分析仪具有模块化设计、灵活的通道配置、高速率、注抖加噪创建压力眼信号、超长用户自定义码型等业内领先的核心技术,可用于高速Serdes芯片和高速接口、光芯片、光器件、光模块、光传输、高速互连等领域苛刻的测试。

未来,中星联华将继续秉承开放包容的心态,在产业龙头的需求牵引下,在国家的大力支持下,与国内外同行共同成长,不断开拓,以开放包容的心态持续为国产电子测量仪器产品体系增砖添瓦,为行业应用打造更多可靠易用的测试测量工具!

中星联华科技(北京)股份有限公司

电话:010-81028321

传真:010-81028322

售前咨询:400-1818-879

网址:www.sinolink-technologies.com

中星联华科技(Sinolink Technologies)成立于2009年,长期从事高频率、高速率、大带宽、宽频带测试测量技术研发,为卫星通信、雷达、复杂电磁环境等传统应用领域及5G移动通信、高速互连等新兴行业提供稳定可靠、性能卓越的专属测试测量工具。

聚焦成就专业,创新服务应用。深度理解行业应用,依托传统测试测量理论和技术,协同行业领军精英共同致力于改善测试工具的实用性、便捷性和经济性,帮助工程师将更多时间与精力投入到研发、生产的本身。以创新测试工具加速相关领域技术发展,推动所服务行业的迭代更新,为人类文明进步增砖添瓦。

随着数字电路工作速度的提高,PCB、连接器、背板上信号的传输速率也越来越高,其中串行数据通信在传输中占据主导地位。按照最严格性能标准制造的拥有精密设计的各种高速互连的PCIE/ETH/VPX背板,以及高速线缆,在当今社会对于高速信号需求普遍存在的大背景下变得至关重要。背板是嵌入式系统中的通信主干,必须按照严格的信号完整性标准进行设计,以确保系统内模块之间及时、准确的数据传输,要满足高速传输的性能预期,信号完整性至关重要。

由于高速串行信号传输速率不断攀升,在电路设计过程中,工程师常常遇到诸多棘手问题,诸如:系统不稳定、间歇性的死机、不同产品兼容性差以及经常出现误码等,而这些现象多半是信号完整性的问题。依照信号传输的完整流程,分别针对 TX 端(发送端)、传输链路以及 RX 端(接收端)进行测试,便能够精准地定位问题根源,从而为后续的优化改进工作提供有力依据,确保高速传输系统的高效稳定运行。

什么是信号完整性?

信号完整性(Signal Integrity,简称SI)是指信号在线路传输过程中保持质量的能力,其核心要求在于确保信号的完整性、准确性和可靠性。在电子系统设计中,如果信号能够按照既定的时序、持续时间和电压幅度到达接收端,则表明该电路具有良好的信号完整性。良好的信号完整性意味着信号在传输和接收过程中能够维持规定的电平和时序。反之,若信号完整性差,其影响因素诸多。其中主要是电源完整性问题。影响因素包括时序问题、反射、串扰、传输距离、信号衰减、温度变化、信号传输介质、杂散、地弹、振铃等,这些都会对信号完整性造成负担,从而导致系统的稳定性下降、误码率增加、功耗增加和性能下降。因此,在高速电路设计中,确保良好的信号完整性至关重要。

在高速电路设计面临三个严峻的问题:信号完整性SI ,电源完整性PI,电磁干扰EMI。SI的主要任务是保证数字电路各芯片之间信号的准确传递;PI的主要目的是确保各部分电路和芯片的可靠供电和噪声抑制;EMI主要目的是确保PCB电路即不干扰其它设备,也不被其它设备干扰。值得注意的是SI的问题,一半以上是因为电源不好引发的信号质量问题,在EMI问题中,一个重要的影响因素是PDN上的高频噪声尤其是电源/地之间的高频噪声。

如何评估高速信号完整性?

在高速信号传输链路中互连链路上任何一个环节的故障可能影响整个系统工作的效率以及稳定性,对于测试人员需要花费更多的成本去发现问题、定位问题、分析问题、解决问题。新标准逐渐从单一互连简单要求的基础上,额外增加协同整体要求。整个高速链路性能的评估,包括Tx发送端,传输链路,以及Rx接收端三大部分组成,发送、接收、电缆或者背板需要放在一个互连链路中评估。评估时按照时域、频域和其他进行不同仪表的选取。

高速链路信号完整性测试工具

TX发送端信号质量的评估

其中TX发送端经常用示波器进行波形完整性、时序完整性、电源完整性、抖动/眼图等测试。

波形完整性:

主要关注波形的单调性(monotonic)、过冲(overshoot,undershoot)、振铃(ringing)、衰减。

时序完整性:

主要关注建立保持时间(setup/hold time)、时序抖动(timing jitter)、skew、毛刺等。

电源完整性:

简称PI,是单板电源设计的一项技术,通过合理的电源平面和滤波设计,为单板上的器件提供稳定/洁净的电源供电,保证单板稳定工作,所以纹波测试为电源测试的必测项,PI和SI是相互影响的。PI包括电源系统设计、直流压降分析、电压瞬态分析、同步开关噪声以及器件建模等。

抖动/眼图:

损耗、反射、串扰三大信号完整性的杀手给信号传输带来巨大影响,会使信号的抖动变大,眼图变差,干扰时钟恢复,降低系统性能,进而在接收端带来误码。

在高速串行信号物理层一致性测试中,抖动和眼图已经成为了一个绕不开的话题,它是评估高速信号质量的关键测试。随着串行数据传输系统的信号速率越来越高,电压摆幅不断降低来节约功耗,系统中的抖动占信号区间的比例正变得越来越大。因此,抖动眼图已经成为限制性能的一个重要因素。随着抖动的增加,系统误码率便会越大。

抖动又可以按照成因分为:TJ、RJ、DJ。DJ中又可细分为PJ、DCD、ISI/DDJ。

其中Random Jitter(随机抖动)的统计分布是正态高斯分布,是无界抖动,随着样本量的增加RJ会一直增加。

然而Deterministic Jitter (确定性抖动)是有界抖动,在达到有限样本数之后,DJ的peak-peak值不会再增加。

上述抖动在测试中经常用来定位问题信号完整性问题来源,除此之外,我们通常还需要进行眼图的测试来直观的表述信号质量的好坏。眼图是把连续的比特流按照某一特定的时钟,分割为单独的比特,而后叠加而形成的图形,类似一个张开的眼睛,故得名眼图(Eye-diagram)。眼图是高速串行信号的宏观信号质量的整体体现,在眼图中可以直接反映出串行信号的幅度、抖动特性等。

评估一个眼图的好和坏,通常利用一些常见的指标来衡量,比如眼高,眼宽,抖动,占空比等。为了简单而又直观地判断眼图的指标是否符合规范的要求,眼图模板测试是一种评估高速串行信号质量的手段,将规范指标的要求编写成一个眼图模板,然后利用示波器来调用这个模板,这样就可以直观看到眼图是否有碰到模板。如果眼图没有碰到模板区域,表示眼图符合规范要求,结果是Pass;同样如果有碰到模板区域,结果是Fail,需要工程师对电路进行整改,改进信号质量到Pass。

均衡技术:

随着高速串行信号的数据速率的越来越高,如PCIE6.0的数据速率已经达到64GT/s,USB4.0 V2的信号速率已经达到80Gb/s。高速信号的趋肤效应和传输线的介质损耗,当信号经过传输链路时,由于信道损耗、阻抗不连续、以及其它信道的干扰等,信号完整性会变差,信噪比也降低,导致接收端的信号抖动变大,眼图闭合,系统可能出现误码。为了改善接收端信号质量,在接收端能得到比较好的眼图。通常会在发送端做FFE均衡和接收端做均衡来完成信号进行补偿,常用的均衡技术有发送端的预加重和去加重以及接收端的CTLE均衡和DFE均衡。

均衡技术是通过均衡器(Equalizer)均衡信道的衰减、均衡数据的码间干扰。均衡技术以前在通信领域使用,随着高速串行信号的传输速率越来越高,均衡技术的使用场合越来越广,比如现在的PCIE、USB、HDMI、DDR、DP、TBT等高速信号中都使用了均衡的技术。使用了均衡技术后,补偿数据的高频损耗,使信号的高频成分与低频成分基本均衡,从而降低高速信号的码间干扰.

其中TX端的预加重和去加重的目的都是尽量平衡高频分量和低频分量,减少传输链路对高频分量衰减大于低频分量衰减。预加重技术就是在传输线的始端增强信号的高频分量,以补偿高频分量在传输链路中较大的衰减。去加重则是降低低频分量的始端信号。

其中RX端最常用的均衡包括FFE、CTLE、DFE。

· FFE实质是使用数字线性高通滤波器提高信号的高频分量,实现信道的补偿, FFE是SerDes系统常用的均衡。为了缓解接收端均衡的压力,通常SerDes的发送端会采用FFE均衡技术对信号进行预均衡。

· CTLE是直接通过线性模拟高通滤波器拟合信道的衰减,实现信道的补偿。信道的频率响应可以看做是一个低通滤波器,因此将信道和一个高通滤波器串联就能得到一个全通的滤波器。

· DFE为判决反馈均衡,就是将判决后的信号反馈到输入信号上。与FFE类似,DFE也是通过数字高频滤波器实现的,DFE可以只放大高频信号,而不放大高频噪声。

高速传输链路评估

随着信号数据速率的越来越高,信号的上升时间也越来越快,阻抗不匹配和偏差可能会导致反射,当快上升沿的信号在电路板上遇到阻抗不连续的位置就会产生很大的反射,会降低信号质量,影响信号完整性。因此走线阻抗是影响高速信号完整性的一个非常关键的因素。

如何验证测试电缆、连接器、PCB板、背板中差分和单端阻抗是否达到设计要求,成为生产商以及高速数字电路设计人员必须关注的问题。对于高速电路,很重要的一点是要保证信号传输路径上阻抗的连续性,这样可以避免信号产生大的反射。因此需要测试高速电路板的信号传输路径上阻抗的变化情况,从而可以分析问题原因,更好地定位问题的根源,保证高质量的产品快速进入市场。

在高速信号电路设计中,经常采用差分传输模式,差分阻抗的测试不同于单端阻抗测试;另外,在高速信号电路中,多个相邻的信号之间会产生串扰。对PCB走线特别是差分走线的阻抗控制提出了更高的要求。如何验证差分阻抗是否达到设计要求成为高速设计的工程师关注的问题。目前验证电缆、连接器、PCB板、背板等传输线特性阻抗的最常用方法是TDR方法。

信号在传输链路路径上传输时会有损耗,反射,串扰的问题,导致信号发生畸变。

· 损耗:传输线的损耗对不同频率是不均匀的,频率越高,损耗越大,上升沿越缓。速率越高,传输线越长,损耗所带来的问题越严重,眼图越容易闭合。

· 反射:传输线上分布电容、电感、和小电阻的存在,会导致传输线的分布式阻抗不均匀,信号流经传输线时部分能量会沿原路反射回去,通常使用TDR来测量传输路径的阻抗变化,如下图:

下面为实时示波器TDR阻抗测试:

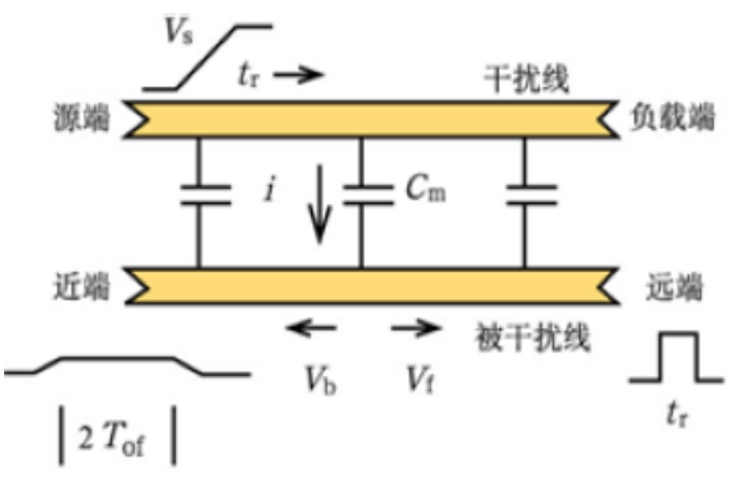

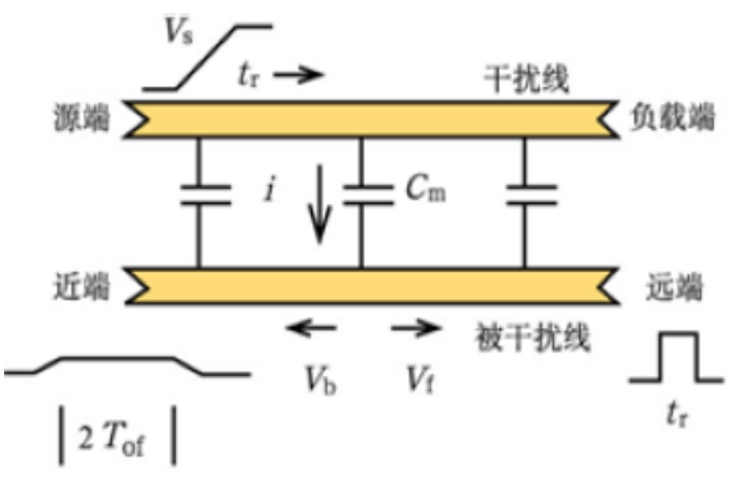

- 串扰:相邻通道间通过地线或空间辐射产生的互相影响。频率越高,串扰越大。串扰会带来额外的噪声,毛刺,抖动,并且使得信噪比变差。远端串扰: 同向传输(同源)信号的干扰,幅度高,脉冲很窄。近端串扰: 反向传输(非同源)信号的干扰,幅度低,脉冲很

信号在传输过程中,对不同速率其损耗不同,反射和串扰都可以导致信号的波形发生 失真,导致眼图闭合。通常使用矢量网络分析仪VNA进行S参数测试和TDR或VNA进行阻抗测试。

RX接收端容限能力的评估

要满足高速传输的性能预期,高信号完整性至关重要,发送端一般利用实时示波器测抖动和眼图,接收端需要利用误码仪进行抖动容限测试和噪声容限测试。接收端中包括CDR时钟恢复、复杂的均衡和信号调理等复杂结构。单纯考察发送端是不足以保证没有误码,接收端的测试也是非常重要,各种高速标准也明确提出了接收端容限测试的规范。接收端容限测试至关重要。RX接收端是整个高速链路的最终环节,接收端测试由于在芯片内部,在绝大多数场景无法直接观测信号完整性问题。最主流的方式是通过创建最的压力眼来模拟真实世界最苛刻的运行环境。误码仪是构建和校准压力眼的核心测试仪器。对于一个高速传输链路,接收端需要在最严苛的环境中保证可靠的接收传输的数据。发送端和链路上的各种信号完整性问题都会恶化信号,减小接收机的余量。接收端测试需要误码分析仪注入多种不同类型的抖动和噪声等压力信号,模拟严苛复杂的真实环境,来完成RX接收端的抖动容限和噪声容限测试。误码仪是进行高速SerDes芯片接收端测试必备仪器。

测试原理:

使用测试仪表产生一个劣化(注入抖动)的眼图信号,俗称压力眼信号。压力眼信号的参数有明确规定,,在不同的规范中具体指标会有不同。通过校准后的压力眼会输入被测接收机进行抖动容限测试。中星联华SL3000B系列高性能误码仪可提供PJ、RJ、BUJ等抖动注入,可以为RX JTOL测试提供强力支持。

测试流程:

- 产生规范要求的抖动分量,在不同的频点上分别产生相应的抖动量;

- 将stressed信号注入DUT Rx;

- 统计DUT Tx端发出的信号的误码率是否达到要求

注入抖动眼图:

测试结果图:

目前,中星联华的高性能误码仪是国内首个支持注入抖动和加噪声创建压力信号的高性能误码仪,也是目前国内首款能够满足接收端抖动容限JTOL和噪声容限ITOL测试的误码仪。其中可支持的注入抖动类型有低频正弦抖动、高频周期抖动、BUJ串扰抖动、RJ随机抖动以及SSC扩频时钟等;支持的噪声类型有CMI和DMI和BBN宽带白噪声,有效地解决“卡脖子”的难题。

RX接收端测试利器——中星联华高性能误码仪

产品特色:

- 模块化:多通道灵活配置,单机支持32发32收

- 高速率:1G-120Gbps,数据速率灵活可调

- 压力眼:注抖加噪,让信号拥有72般变化

- UDP:最大可支持16Gbit超长用户自定义码型

中星联华高性能误码分析仪具有模块化设计、灵活的通道配置、高速率、注抖加噪创建压力眼信号、超长用户自定义码型等业内领先的核心技术,可用于高速Serdes芯片和高速接口、光芯片、光器件、光模块、光传输、高速互连等领域苛刻的测试。

未来,中星联华将继续秉承开放包容的心态,在产业龙头的需求牵引下,在国家的大力支持下,与国内外同行共同成长,不断开拓,以开放包容的心态持续为国产电子测量仪器产品体系增砖添瓦,为行业应用打造更多可靠易用的测试测量工具!

中星联华科技(北京)股份有限公司

电话:010-81028321

传真:010-81028322

售前咨询:400-1818-879

网址:www.sinolink-technologies.com

中星联华科技(Sinolink Technologies)成立于2009年,长期从事高频率、高速率、大带宽、宽频带测试测量技术研发,为卫星通信、雷达、复杂电磁环境等传统应用领域及5G移动通信、高速互连等新兴行业提供稳定可靠、性能卓越的专属测试测量工具。

聚焦成就专业,创新服务应用。深度理解行业应用,依托传统测试测量理论和技术,协同行业领军精英共同致力于改善测试工具的实用性、便捷性和经济性,帮助工程师将更多时间与精力投入到研发、生产的本身。以创新测试工具加速相关领域技术发展,推动所服务行业的迭代更新,为人类文明进步增砖添瓦。

责任编辑:Ace

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 英伟达,又挖了一道护城河

- 2 NVIDIA重磅出击:三台计算机助力人形机器人飞跃

- 3 奕行智能(EVAS Intelligence)完成数亿元A轮融资,加速推出RISC-V计算芯片产品,共同助力新时代到来

- 4 江波龙全球最小尺寸eMMC,为AI穿戴设备“减负”