半导体未来三大支柱:先进封装、晶体管和互连

2024-12-13

09:45:53

来源: 杜芹

点击

最近一段时间以来,芯片巨头英特尔在商业和市场层面经历了诸多挑战。但有一说一,英特尔在前沿技术领域的探索和布局依然具有行业标杆意义,其发布的技术路线图和成果为半导体行业提供了重要参考方向。

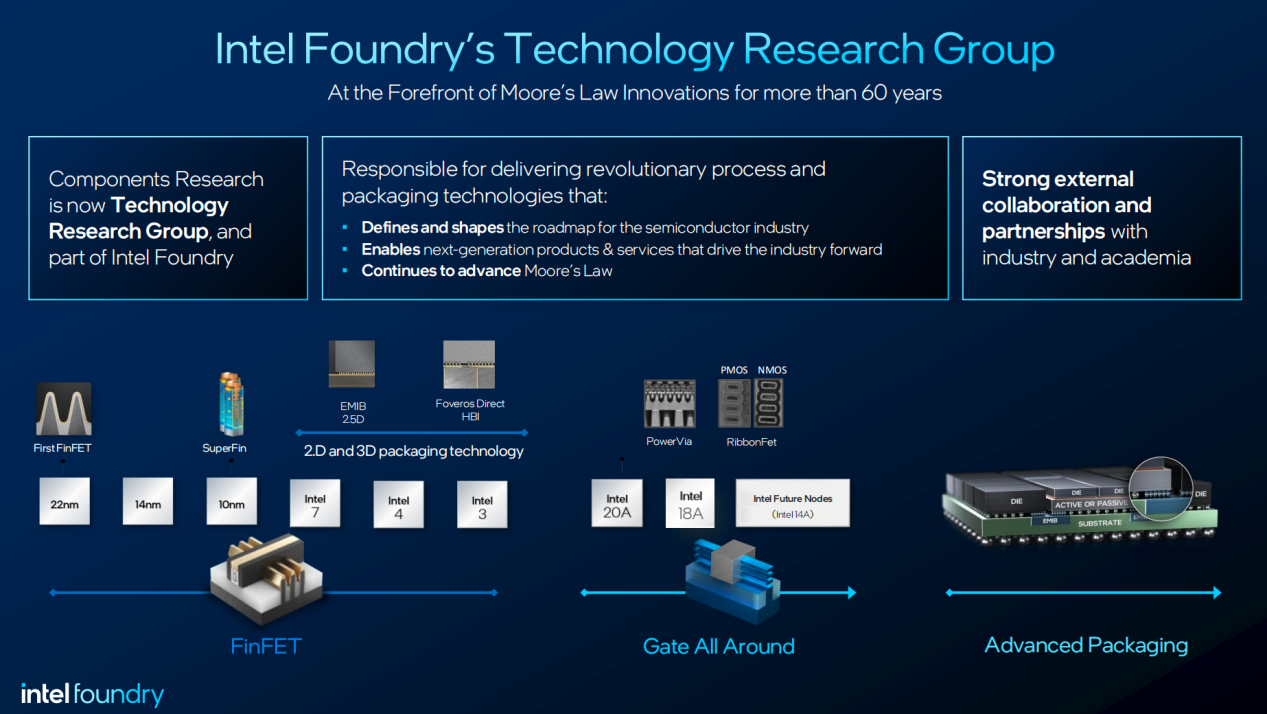

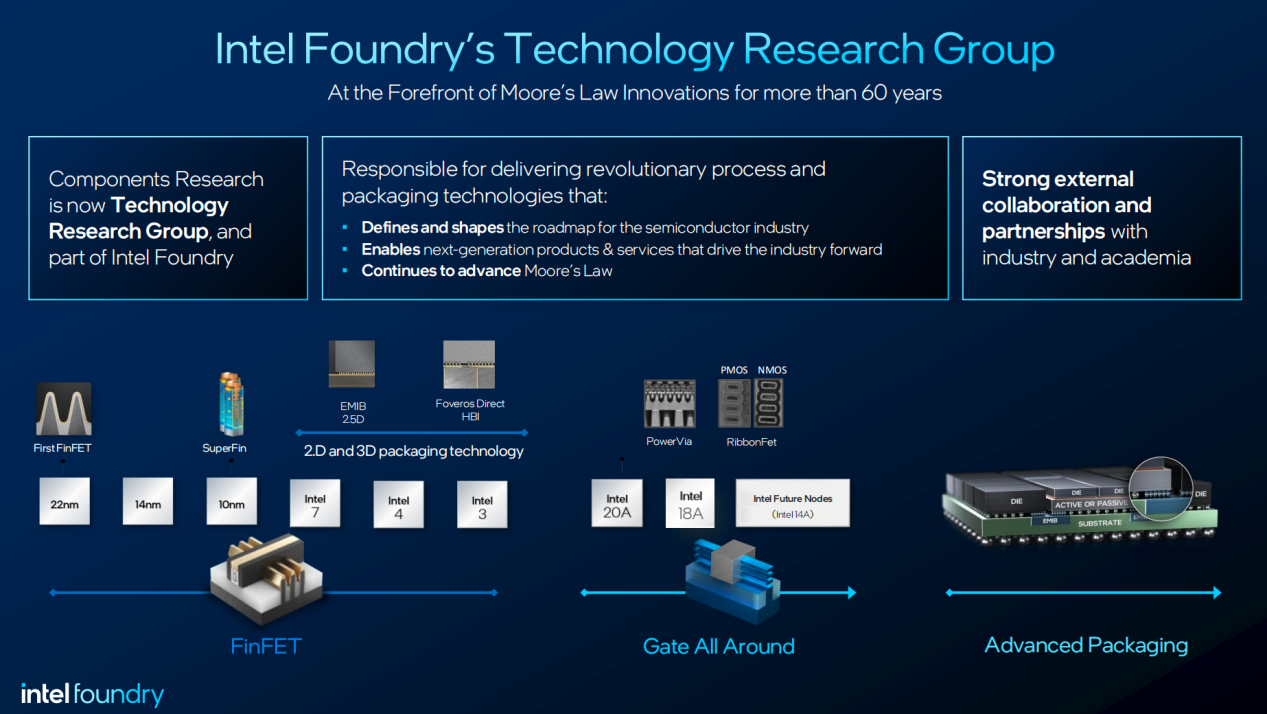

在IEDM 2024大会上,英特尔发布了7篇技术论文,展示了多个关键领域的创新进展。这些技术涵盖了从FinFET到2.5D和3D封装(EMIB、Foveros、Foveros Direct),即将在Intel 18A节点应用的PowerVia背面供电技术,以及全环绕栅极(GAA)晶体管RibbonFET等。此外,英特尔还揭示了一些面向未来的先进封装技术,为推动行业发展提供了新的视角。

在这些前沿技术中,三个核心领域尤为值得关注:面向AI发展的先进封装、晶体管微缩技术和互连微缩技术。在IEDM 2024大会上,英特尔代工高级副总裁兼技术研究总经理Sanjay Natarajan详细介绍了这些领域的关键突破。

先进封装的突破:选择性层转移技术

异构集成已经成为当今芯片界的主流实现性能提升的手段。但是异构集成技术面临着很大的挑战。当前异构集成技术主要采用“晶圆对晶圆键合”(Wafer-to-Wafer HB)或“芯片对晶圆键合”(Chip-to-Wafer HB),会因顺序装配芯粒而导致吞吐量、芯片尺寸和厚度受限。

英特尔通过选择性层转移(Selective Layer Transfer)技术,突破了当前异构集成的技术瓶颈。这项技术能够以超高效率完成超过15,000个芯粒的并行转移,仅需几分钟即可实现相较于传统方法数小时或数天的提升。其创新性地实现了亚微米级芯粒的转移,支持仅1平方毫米大小、厚度为人类头发1/17的芯粒。这提供了一种灵活且成本效益显著的异构集成架构,使得处理器与存储器技术的混合搭配成为可能。Intel Foundry率先采用无机红外激光脱键技术,实现了芯粒转移的技术突破,推动了旗舰AI产品开发所需的先进异构集成技术的发展。

Sanjay Natarajan表示:“我们有理由期待这一技术能够像PowerVia背面供电技术一样在业内普及。我们将积极开创并推动这项技术的发展,我认为我们会看到业内领先企业都逐步采用这一技术。”

面向AI时代,英特尔提出了全面的封装解决方案,以实现AI系统的大规模量产。除了选择性层转移技术,英特尔还聚焦于:

l 先进内存集成(memory integration):解决容量、带宽和延迟瓶颈,提升性能。

l 混合键合(hybrid bodning)互连的间距缩放:实现异构组件间的高能效和高带宽密度连接。

l 模块化系统的扩展:通过连接解决方案降低网络延迟和带宽限制。

GAA晶体管的突破:物理和二维材料

晶体管技术的进步一直以来都是英特尔的主业之一,英特尔的目标是到2030年实现一万亿晶体管的宏伟目标。

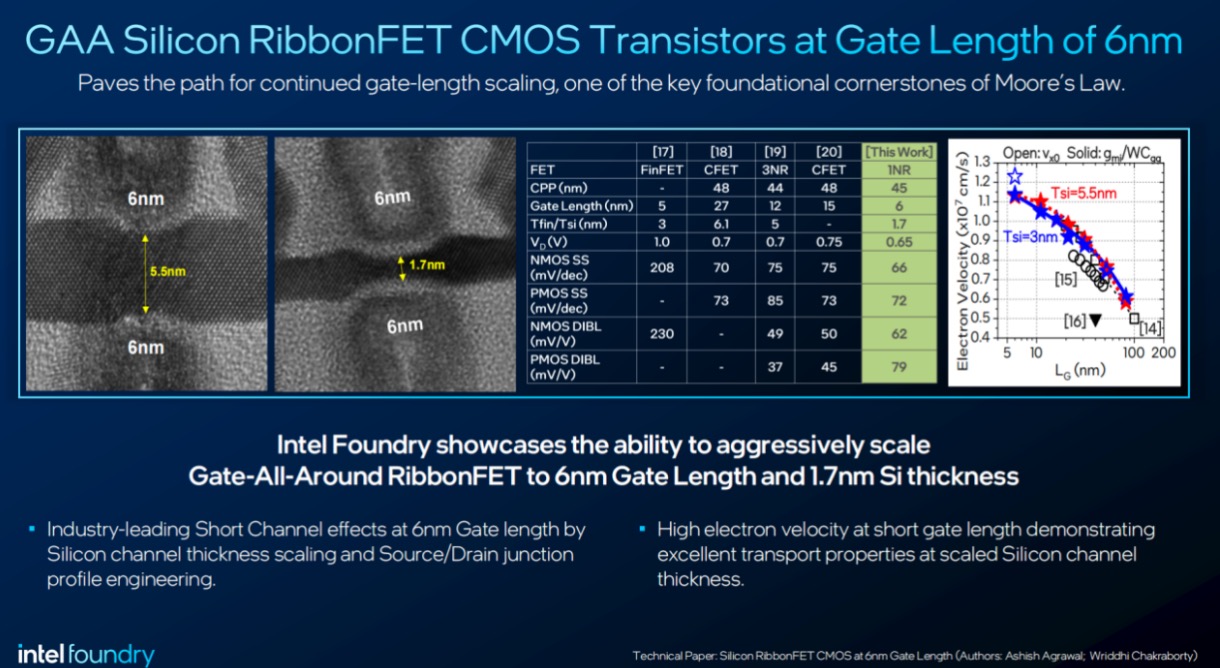

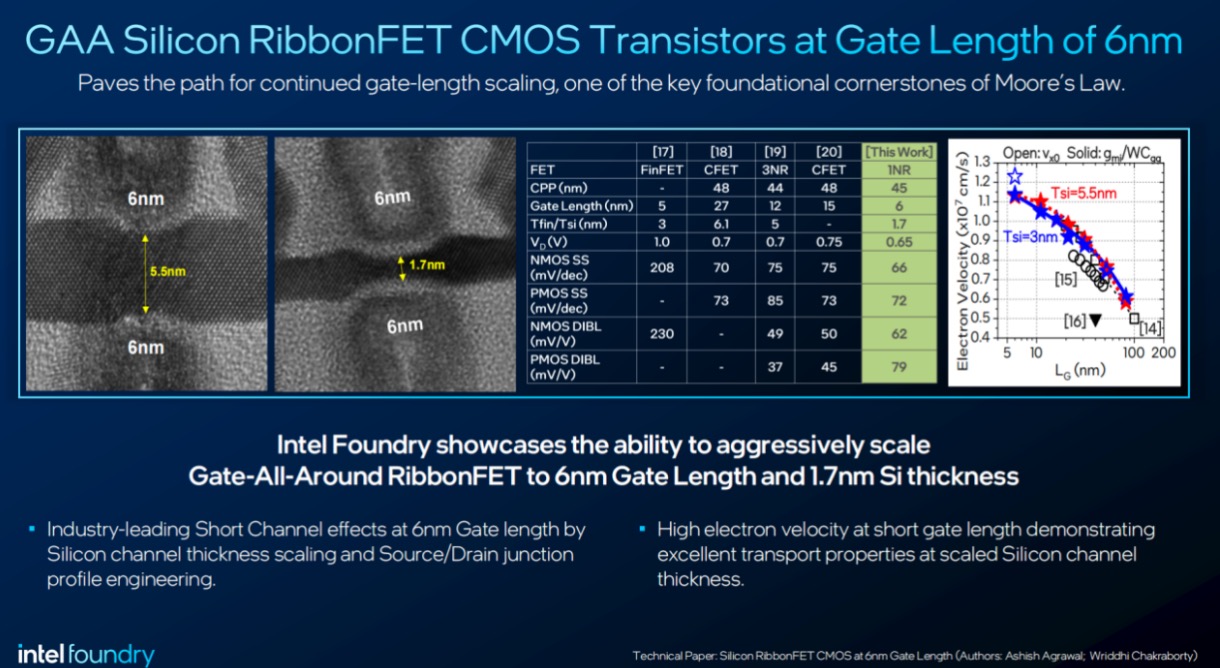

Intel展示了其在Gate-All-Around(GAA)RibbonFET晶体管上的技术突破,成功将栅极长度缩小至6nm,并实现1.7nm硅通道厚度。通过对硅通道厚度和源漏结的精准工程设计,有效减少了漏电流和器件退化,提高了晶体管在极短栅极长度下的性能稳定性。英特尔研究数据显示,与其他先进节点技术相比,在6nm栅极长度下,RibbonFET在短栅极长度下具备更高的电子迁移率和更优的能效特性。除此之外,RibbonFET实现了最佳的亚阈值摆幅(Subthreshold Swing,SS)和漏电流抑制性能(DIBL)。

左图是透射电子显微镜(TEM)图像,中间展示看这些晶体管的部分关键参数,右图是栅极长度与电子速度关系图

这一进展展示了在短沟道效应优化方面的行业领先水平,这为未来更高密度、更低功耗的芯片设计奠定了基础,同时推动了摩尔定律的持续发展,满足了下一代计算和AI应用对半导体性能的严苛需求。

为了推进GAA晶体管技术的发展,英特尔也将目光瞄准了二维半导体材料。

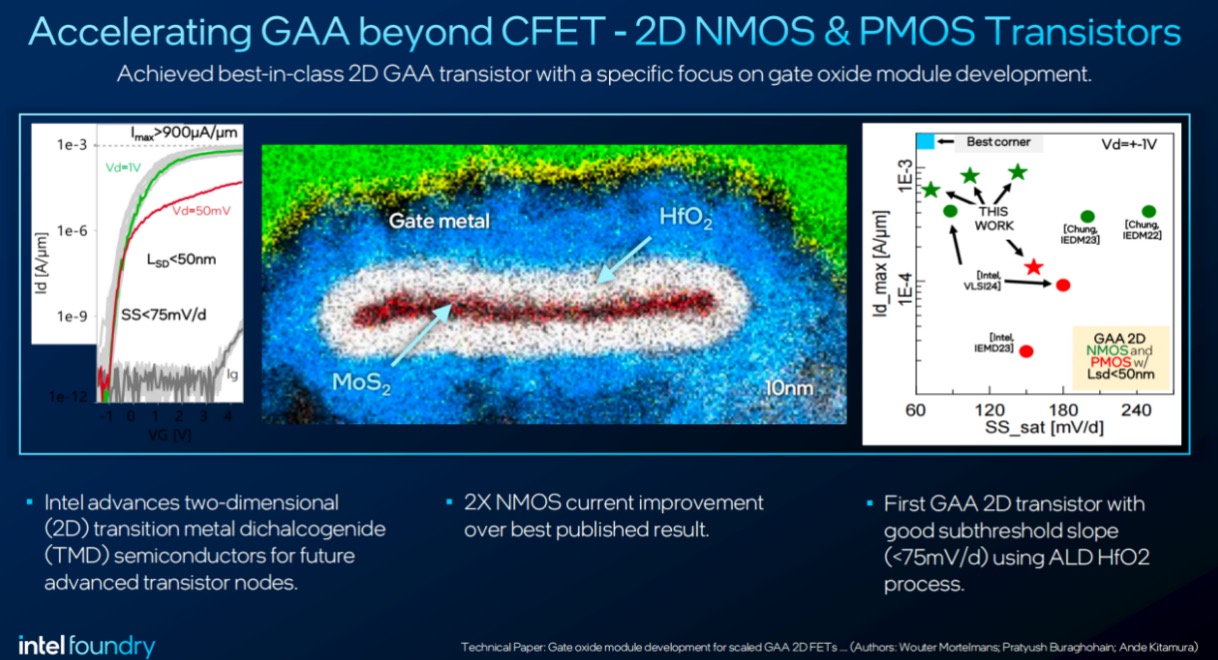

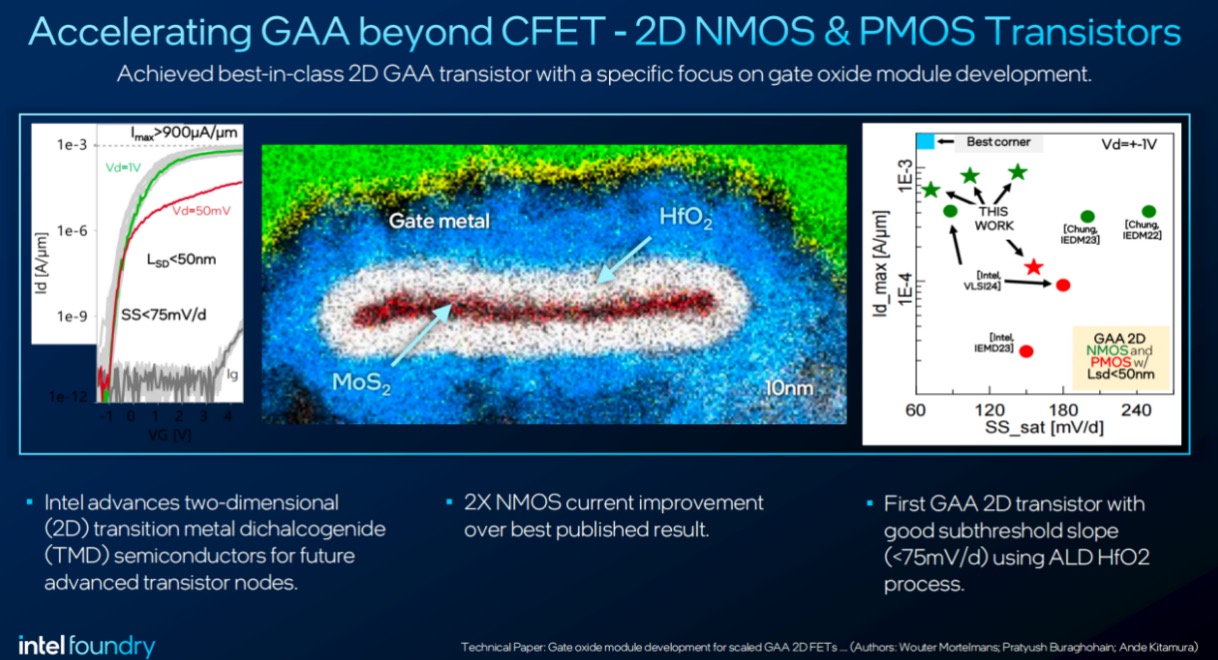

据Sanjay Natarajan的介绍,具体而言,英特尔在GAA技术中引入了二维(2D)NMOS和PMOS晶体管,该晶体管以二维MoS2为沟道材料,结合高介电常数的HfO2作为栅氧化层,通过ALD(原子层沉积)工艺实现精确控制。下图的横截面成像清晰展示了栅极金属、HfO₂氧化物和二维MoS2之间的结构集成,其整体厚度在纳米级别,漏源间距(L_SD)小于50nm,次阈值摆幅(SS)低于75mV/d,最大电流性能(I_max)达到900µA/µm以上,能够显著提升栅极对沟道的控制能力。

右侧的图表中将Intel的研究结果(THIS WORK)与其他同类研究进行了对比,显示在驱动电流和次阈值摆幅上的明显优势。

英特尔的研究验证了结合GAA架构和2D材料,晶体管性能堪称飞跃。而且一旦英特尔将基于硅的沟道性能推至极限,采用2D材料的GAA晶体管很有可能会成为下一步发展的合理方向。

就英特尔所观察到的而言,晶体管数量的指数级增长趋势,符合摩尔定律,从微型计算机到数据中心,晶体管数量每两年翻倍。但是,随着AI工作负载的持续增加,AI相关能耗可能会在2035年超越美国当前的总电力需求,能源瓶颈成为未来计算发展的关键挑战。因此,未来需要的是新型晶体管。下一代晶体管需要具备超陡次阈值摆幅(低于60mV/dec)和极低的静态漏电流(I_off),支持在超低供电电压(<300mV)下运行。

英特尔也在材料和物理层面不断探索,并在IEDM上展示了采用Ge(锗)纳米带结构的晶体管,其9nm厚度和结合氧化物界面的创新设计,为实现低功耗和高效传输奠定了基础。Intel进一步研究结合高介电常数材料和新型界面工程,以开发更加节能高效的下一代晶体管。

英特尔也呼吁整个行业共同推动晶体管技术的革命,以满足万亿晶体管时代中AI应用的需求。通过对过去60年晶体管发展的总结,Intel同时提出了未来10年的发展目标:1)必须开发能够在超低供电电压(<300mV)下工作的晶体管,以显著提高能效,为普遍化的AI应用提供支持;2)持续增加晶体管数量的技术是可行的,但能源效率的革命性突破将是未来发展的重点。

互联缩放的突破:钌线路

随着晶体管和封装技术的持续微缩,互连已成为半导体体系中的第三个关键要素。这些互连导线负责连接数以万亿计的晶体管。然而,我们清晰地看到,铜互连的时代正逐渐走向尾声。铜互连存在一个实际问题:使用时需要添加阻挡层和籽晶层。随着尺寸的不断缩小,这些相对高电阻的层占据了更多的可用空间。英特尔观察到,当线宽不断缩小时,铜线的电阻率呈指数级上升,达到难以接受的程度。因此,尽管晶体管尺寸越来越小、密度和性能不断提升,但传统的布线方式已无法满足连接所有晶体管的需求。

英特尔的突破在于采用具有高成本效益的空气间隙钌(Ru)线路,作为铜互连的潜在替代方案。这个空气间隙解决方案无需昂贵的光刻技术,也不需要自动对准通孔工艺。它巧妙地将空气间隙、减法钌工艺和图案化相结合,有望打造出合理的下一代互连技术,使之与未来的晶体管和封装技术相匹配。

这种新工艺在小于25nm的间距下,实现了在匹配电阻条件下高达25%的电容降低,有效提升了信号传输速度并减少了功耗。高分辨率的显微成像展示了钌互连线和通孔的精确对齐,验证了没有发生通孔突破或严重错位的问题。减法钌工艺支持大规模生产(HVM),通过消除复杂的气隙排除区和选择性蚀刻需求,具备实际应用的经济性和可靠性。

写在最后

半导体产业是一个高度复杂的生态系统,需要各方共同努力才能取得突破。英特尔在封装、晶体管和互联等领域的创新成果,为整个行业提供了宝贵的经验和启示。如同Sanjay Natarajan所述,英特尔的目标是为整个行业提供路线图,以协调和统一我们所有的研发资金和努力。这样,下一代产品和服务就能推动整个行业向前发展,并继续推进摩尔定律。英特尔确实始终将自己视为摩尔定律的守护者,致力于承担这一责任,不断探索推进摩尔定律的新技术。这不仅是为了英特尔的利益,更是为了整个行业的共同利益。

在IEDM 2024大会上,英特尔发布了7篇技术论文,展示了多个关键领域的创新进展。这些技术涵盖了从FinFET到2.5D和3D封装(EMIB、Foveros、Foveros Direct),即将在Intel 18A节点应用的PowerVia背面供电技术,以及全环绕栅极(GAA)晶体管RibbonFET等。此外,英特尔还揭示了一些面向未来的先进封装技术,为推动行业发展提供了新的视角。

在这些前沿技术中,三个核心领域尤为值得关注:面向AI发展的先进封装、晶体管微缩技术和互连微缩技术。在IEDM 2024大会上,英特尔代工高级副总裁兼技术研究总经理Sanjay Natarajan详细介绍了这些领域的关键突破。

先进封装的突破:选择性层转移技术

异构集成已经成为当今芯片界的主流实现性能提升的手段。但是异构集成技术面临着很大的挑战。当前异构集成技术主要采用“晶圆对晶圆键合”(Wafer-to-Wafer HB)或“芯片对晶圆键合”(Chip-to-Wafer HB),会因顺序装配芯粒而导致吞吐量、芯片尺寸和厚度受限。

英特尔通过选择性层转移(Selective Layer Transfer)技术,突破了当前异构集成的技术瓶颈。这项技术能够以超高效率完成超过15,000个芯粒的并行转移,仅需几分钟即可实现相较于传统方法数小时或数天的提升。其创新性地实现了亚微米级芯粒的转移,支持仅1平方毫米大小、厚度为人类头发1/17的芯粒。这提供了一种灵活且成本效益显著的异构集成架构,使得处理器与存储器技术的混合搭配成为可能。Intel Foundry率先采用无机红外激光脱键技术,实现了芯粒转移的技术突破,推动了旗舰AI产品开发所需的先进异构集成技术的发展。

Sanjay Natarajan表示:“我们有理由期待这一技术能够像PowerVia背面供电技术一样在业内普及。我们将积极开创并推动这项技术的发展,我认为我们会看到业内领先企业都逐步采用这一技术。”

面向AI时代,英特尔提出了全面的封装解决方案,以实现AI系统的大规模量产。除了选择性层转移技术,英特尔还聚焦于:

l 先进内存集成(memory integration):解决容量、带宽和延迟瓶颈,提升性能。

l 混合键合(hybrid bodning)互连的间距缩放:实现异构组件间的高能效和高带宽密度连接。

l 模块化系统的扩展:通过连接解决方案降低网络延迟和带宽限制。

GAA晶体管的突破:物理和二维材料

晶体管技术的进步一直以来都是英特尔的主业之一,英特尔的目标是到2030年实现一万亿晶体管的宏伟目标。

Intel展示了其在Gate-All-Around(GAA)RibbonFET晶体管上的技术突破,成功将栅极长度缩小至6nm,并实现1.7nm硅通道厚度。通过对硅通道厚度和源漏结的精准工程设计,有效减少了漏电流和器件退化,提高了晶体管在极短栅极长度下的性能稳定性。英特尔研究数据显示,与其他先进节点技术相比,在6nm栅极长度下,RibbonFET在短栅极长度下具备更高的电子迁移率和更优的能效特性。除此之外,RibbonFET实现了最佳的亚阈值摆幅(Subthreshold Swing,SS)和漏电流抑制性能(DIBL)。

左图是透射电子显微镜(TEM)图像,中间展示看这些晶体管的部分关键参数,右图是栅极长度与电子速度关系图

这一进展展示了在短沟道效应优化方面的行业领先水平,这为未来更高密度、更低功耗的芯片设计奠定了基础,同时推动了摩尔定律的持续发展,满足了下一代计算和AI应用对半导体性能的严苛需求。

为了推进GAA晶体管技术的发展,英特尔也将目光瞄准了二维半导体材料。

据Sanjay Natarajan的介绍,具体而言,英特尔在GAA技术中引入了二维(2D)NMOS和PMOS晶体管,该晶体管以二维MoS2为沟道材料,结合高介电常数的HfO2作为栅氧化层,通过ALD(原子层沉积)工艺实现精确控制。下图的横截面成像清晰展示了栅极金属、HfO₂氧化物和二维MoS2之间的结构集成,其整体厚度在纳米级别,漏源间距(L_SD)小于50nm,次阈值摆幅(SS)低于75mV/d,最大电流性能(I_max)达到900µA/µm以上,能够显著提升栅极对沟道的控制能力。

右侧的图表中将Intel的研究结果(THIS WORK)与其他同类研究进行了对比,显示在驱动电流和次阈值摆幅上的明显优势。

英特尔的研究验证了结合GAA架构和2D材料,晶体管性能堪称飞跃。而且一旦英特尔将基于硅的沟道性能推至极限,采用2D材料的GAA晶体管很有可能会成为下一步发展的合理方向。

就英特尔所观察到的而言,晶体管数量的指数级增长趋势,符合摩尔定律,从微型计算机到数据中心,晶体管数量每两年翻倍。但是,随着AI工作负载的持续增加,AI相关能耗可能会在2035年超越美国当前的总电力需求,能源瓶颈成为未来计算发展的关键挑战。因此,未来需要的是新型晶体管。下一代晶体管需要具备超陡次阈值摆幅(低于60mV/dec)和极低的静态漏电流(I_off),支持在超低供电电压(<300mV)下运行。

英特尔也在材料和物理层面不断探索,并在IEDM上展示了采用Ge(锗)纳米带结构的晶体管,其9nm厚度和结合氧化物界面的创新设计,为实现低功耗和高效传输奠定了基础。Intel进一步研究结合高介电常数材料和新型界面工程,以开发更加节能高效的下一代晶体管。

英特尔也呼吁整个行业共同推动晶体管技术的革命,以满足万亿晶体管时代中AI应用的需求。通过对过去60年晶体管发展的总结,Intel同时提出了未来10年的发展目标:1)必须开发能够在超低供电电压(<300mV)下工作的晶体管,以显著提高能效,为普遍化的AI应用提供支持;2)持续增加晶体管数量的技术是可行的,但能源效率的革命性突破将是未来发展的重点。

互联缩放的突破:钌线路

随着晶体管和封装技术的持续微缩,互连已成为半导体体系中的第三个关键要素。这些互连导线负责连接数以万亿计的晶体管。然而,我们清晰地看到,铜互连的时代正逐渐走向尾声。铜互连存在一个实际问题:使用时需要添加阻挡层和籽晶层。随着尺寸的不断缩小,这些相对高电阻的层占据了更多的可用空间。英特尔观察到,当线宽不断缩小时,铜线的电阻率呈指数级上升,达到难以接受的程度。因此,尽管晶体管尺寸越来越小、密度和性能不断提升,但传统的布线方式已无法满足连接所有晶体管的需求。

英特尔的突破在于采用具有高成本效益的空气间隙钌(Ru)线路,作为铜互连的潜在替代方案。这个空气间隙解决方案无需昂贵的光刻技术,也不需要自动对准通孔工艺。它巧妙地将空气间隙、减法钌工艺和图案化相结合,有望打造出合理的下一代互连技术,使之与未来的晶体管和封装技术相匹配。

这种新工艺在小于25nm的间距下,实现了在匹配电阻条件下高达25%的电容降低,有效提升了信号传输速度并减少了功耗。高分辨率的显微成像展示了钌互连线和通孔的精确对齐,验证了没有发生通孔突破或严重错位的问题。减法钌工艺支持大规模生产(HVM),通过消除复杂的气隙排除区和选择性蚀刻需求,具备实际应用的经济性和可靠性。

写在最后

半导体产业是一个高度复杂的生态系统,需要各方共同努力才能取得突破。英特尔在封装、晶体管和互联等领域的创新成果,为整个行业提供了宝贵的经验和启示。如同Sanjay Natarajan所述,英特尔的目标是为整个行业提供路线图,以协调和统一我们所有的研发资金和努力。这样,下一代产品和服务就能推动整个行业向前发展,并继续推进摩尔定律。英特尔确实始终将自己视为摩尔定律的守护者,致力于承担这一责任,不断探索推进摩尔定律的新技术。这不仅是为了英特尔的利益,更是为了整个行业的共同利益。

责任编辑:sophie

相关文章

-

- 半导体行业观察

-

- 摩尔芯闻

最新新闻

热门文章 本日 七天 本月

- 1 芯明闪耀2024:中国半导体与集成电路领域商业潜力新标杆

- 2 喜迎澳门回归25周年,澳门一微科技公司举行“新质引领·共赴琴澳”产品发布会

- 3 半导体未来三大支柱:先进封装、晶体管和互连

- 4 庆祝显示技术30年创新历程