[原创] 遇到eFPGA,5G基站难题有解了

目前,全球市场约有75亿个处于激活状态的移动设备,这一数字比全球人口还要多。蜂窝网络连接对人们所产生的影响是深远的; 例如,两年前的研究表明,撒哈拉以南非洲地区每100人通常有1个固定电话,但有74个移动连接设备。毫无疑问,随着无线基础设施发展到5G,它将变得更加普遍,并与我们日常生活的方方面面完全融为一体。它将支持我们更高的带宽需求,并扩展到更多设备和应用场景。

趋势

硬件设计人员必须清楚市场发展的主要趋势,首先就是对增强型移动宽带(eMBB)和其他应用的带宽增加需求,特别是以10倍电流速率驱动瞬时可用带宽。此外,5G的部署也将根据频段进行,首先部署6GHz以下,然后是mmWave频率的连续频段,以便在稍后阶段实现更多的关键eMBB应用。其次,随着物联网(IoT)时代的到来,大量设备之间的连接需求将会出现爆发式增长。预计两年内将有500亿台蜂窝连接设备。这些需求当中的一部分可以通过现有标准解决,另外就是要靠3GPP的Release 16版本中的mMTC规范去实现了。

此外,新的应用场景也在不断涌现,这对移动设备及其蜂窝基础设施提出了新的要求,如用于连接电池供电的物联网端点,以及用于连接和监控mMTC对低带宽、低功耗的要求;用于车辆到车辆和车辆到基础设施的连接(C-V2X),以补充现有的V2X解决方案,如碰撞检测,以及为远程手术和增强/虚拟现实等新兴应用提供高可靠性、低延迟支持的需求。后两个示例将通过即将推出的超可靠、低延迟连接(URLLC)的3GPP标准来解决。

了解趋势是边缘分析和移动边缘计算(MEC)的一项重要新兴需求。计算重心正在从以前的将数据发送到集中式计算资源的处理过程,转变为移到位于数据原点附近的分布式计算资源的新范例。这种转变的原因包括严格的延迟要求,越来越庞大的数据量,以及优化网络资源和能源的愿望。

第1层处理

基带从网络接口(例如以太网)获取数据,并将其转换为通过前传(Fronthaul)接口传输到RF前端的复杂样本。

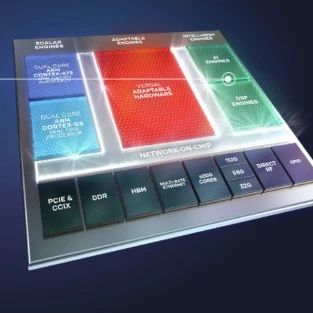

SoC架构可以成功解决5G的独特需求,该架构包括高性能CPU子系统和硬件处理元件,包括FPGA可重编程加速。这里,基带处理的第1层可以映射到关键处理元件,如处理器子系统、CPU和DSP内核,以及固定和灵活的硬件加速,如图1所示。

图1:关键基带处理元素

前传的灵活性

除了前面描述的处理元件之外,还有一个灵活的天线接口功能块:这是连接基带和RF前端所需的元件。传统上,这是通用公共无线电接口(CPRI),有时是开放式基站架构计划(OBSAI)。然而,越来越多应用需要指定更灵活的前传接口,以允许基带和RF前端之间的不同映射(如图1所示)。IEEE对下一代前传接口NGFI(IEEE1914)进行了持续的跟进,包括用于基于分组的前传传输网络和IEEE1914.3以太网无线电(RoE)封装和映射的IEEE1914.1标准。同时,还有其他行业计划指定了5G前传接口并可共享,例如eCPRI。

鉴于前传接口的各种规范、标准和要求,FPGA很适合其应用,并通常用于支持此接口,如上面的图1所示。

独立架构缩短了产品上市时间

如图2所示,其将5G所需的处理元素映射为具有独立器件的分立式架构,包括CPU SoC,旁视FPGA加速和天线接口。此配置反映了在使用优化的5G ASIC之前,可以在5G原型设计和已经成熟量产的实施中部署。

CPU片上系统包括:ARM处理复合体以及用于第1层处理和硬化加速器的DSP内核,用于固定的、定义明确的功能。在此示例中,假设现有的4G ASIC SoC可用,因此具有通用加速(例如MACSEC)以及LTE特定加速:前向纠错(特别是turbo编解码器),快速傅立叶变换和离散傅里叶变换。在上行链路上支持SC-FDMA。

灵活的天线接口:如前所述,前传天线接口非常适合用FPGA实现。这是在线配置的,数据从RF前端发出(在上行链路),然后被转换为具有标准连接的协议,如以太网。

硬件加速FPGA:旁视加速FPGA实现了基础SoC上不可用的所有必要的计算密集型功能。这可以是5G特定功能或先前未设想的功能。

在此处显示的示例中,使用CCIX互连。该标准允许基于不同指令集架构的处理器将缓存一致性、对等处理的优势扩展到包括FPGA和定制ASIC在内的多种加速器件。

图2:加速5G上市时间的分立结构

Chiplet替代方案

图3显示了与图2所示类似的架构,但是使用基于小芯片(chiplet)的方法进行了重新配置。在这种情况下,使用更高带宽、更低延迟和更低功耗的接口将CPU SoC芯片与后备硬件加速FPGA芯片连接起来。支持与RF前端的前传连接的FPGA器件在该示例中不是封装集成的,但实际上,如果有足够的资源,它可以是与硬件加速chiplet相同的chiplet器件。

图3:基于Chiplet的方法可实现更高的集成度

封装集成的两种主要技术和方案是使用硅中介层或有机基板和某种形式的超短距离(USR)收发器。

完全集成的5G架构

最后,图4显示了此处考虑的最终、最高集成度的基带架构。该方法包括与先前相同的处理元件,具有相同的功能,但嵌入式FPGA(eFPGA)集成在了芯片内。

图4:采用单片集成的异构多核片上系统,应用于5G基带

这种紧密集成的单片集成方法具有许多优点。与基于小芯片的方法相比,该接口具有更高的带宽,更低的延迟和更低的每比特能耗。此外,资源组合可以根据所考虑的特定应用进行定制,因此避免了不需要的接口、存储器和核心逻辑器件。这样可以实现以上所考虑的三种架构的最低单位成本。

如前所述,这里的主要目标是提供更快的上市时间、灵活性和未来验证。之所以加快了上市时间,是因为SoC可以提前流片,因为后期修改(例如5G中Polar码的出现)可以针对eFPGA而不是ASIC。新算法(例如新的加密标准)的灵活性可以通过嵌入式可编程逻辑而不是软件或外部FPGA来解决。最后,未来验证可以延长SoC生命周期,因为大型新兴需求(例如URLLC和mMTC等新标准)可以通过现有产品解决,而不需要新的开发。

从5G的角度来看,高度可编程的解决方案可以加快产品上市速度。在标准最终确定之前,不再需要推迟SoC的流片时间,后续追加的要求可以在软件或可编程硬件中实现。对于早期5G部署所面临的压力,以及新标准的不断涌现,这是一个突出优势。